1. 1

Устройство относится к вычислительной технике и может быть использовано при конструировании и разработке специализированных и универсальных арифметико-логических устройств.

Цель изобретения - увеличение быстродействия устройства.

На чертеже представлена функциональная схема устройства.

Устройство содержит входы 1-4, значащих разрядов первого и второго слагаемых входы 5 и 6 знаковых разрядов соответственно первого и второго операндов, двухразрядный

1сомбина1 ;ионный сумматор 7, блок 8 формирования результата, первый 9 и второй 10 элементы задержки, элемент И 11, элемент ИЛИ 12, выходы 13 и 14 первого, второго значащих разрядов результата, выход 15 знакового разряда результата устройства, вход 16 управления видом операции.

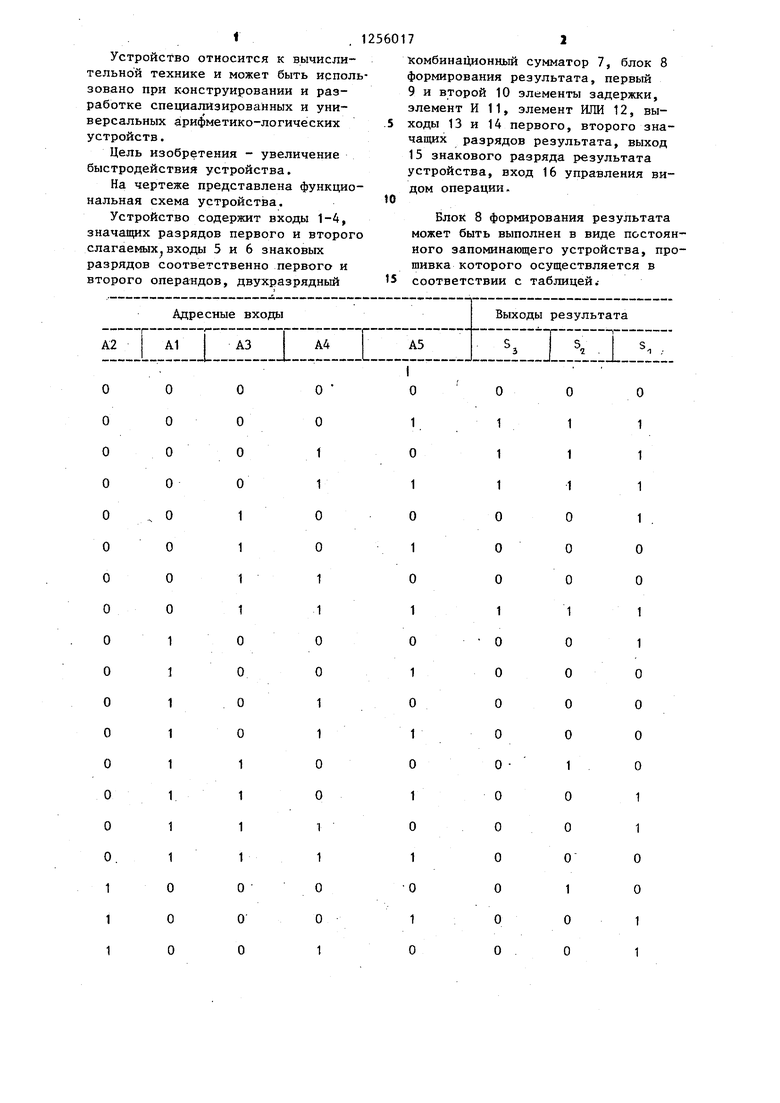

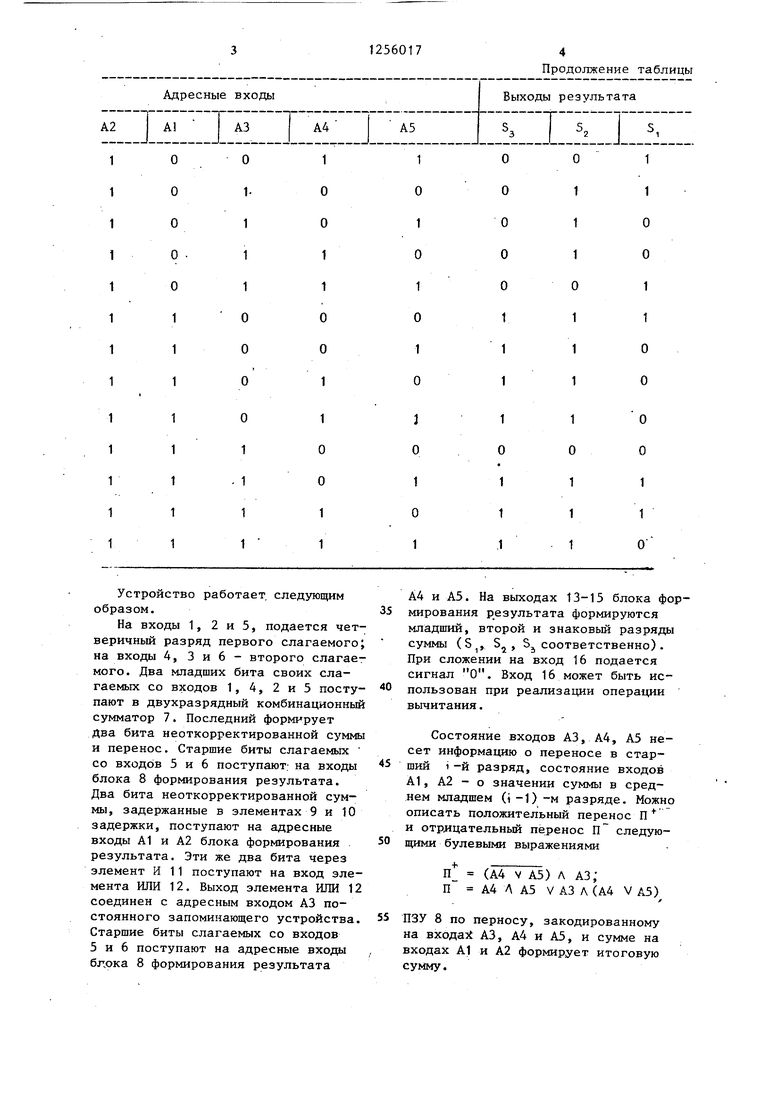

Блок 8 формирования результата может быть выполнен в виде постоянного запоминающего устройства, прошивка которого осуществляется в соответствии с таблицей.Устройство работает, следующим образом.

На входы 1, 2 и 5, подается четверичный разряд первого слагаемого; на входы 4, 3 и 6 - второго слагаемого. Два младших бита своих слагаемых со входов 1, 4, 2 и 5 поступают в двухразрядный комбинационный сумматор 7. Последний формирует Два бита неоткорректированной суммы и перенос. Старшие биты слагаемых со входов 5 и 6 поступают; на входы блока 8 формирования результата. Два бита неоткорректированной суммы, задержанные в элементах 9 и 10 задержки, поступают на адресные входы А1 и А2 блока формирования . результата. Эти же два бита через элемент И 11 поступают на вход элемента ИЛИ 12. Выход элемента ШШ 12 соединен с адресным входом A3 постоянного запоминающего устройства. Старшие биты слагаемых со входов 5 и 6 поступают на адресные входы бг.ока 8 формирования результата

Продолжение таблицы

А4 и А5. На выходах 13-15 блока формирования результата формируются младший, второй и знаковый разряды суммы (5, S, , Sj соответственно) . При сложении на вход 16 подается сигнал О. Вход 16 может быть использован при реализации операции вычитания.

Состояние входов A3, А4, А5 несет информацию о переносе в старший i-и разряд, состояние входов А1, А2 - о значении суммы в среднем младшем (i-1) -м разряде. Можно описать положительный перенос П и отрицательный перенос П следующими булевыми выражениями

П

п

(А4 V А5) Л A3;

А4 Л А5 V A3 Л (А4 V А5)

55 ПЗУ 8 по перносу, закодированному на входа-it. A3, А4 и А5, и сумме на входах А1 и А2 формирует итоговую сумму.

5. 1

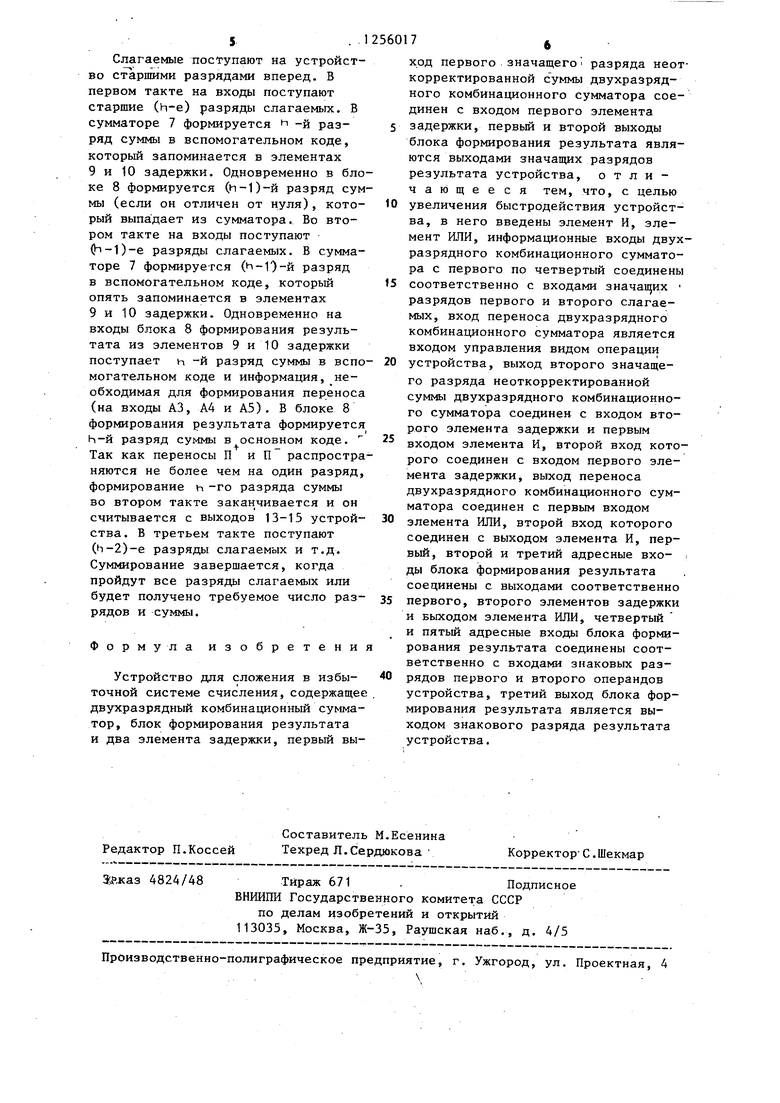

Слагаемые поступают на устройство ст-аршими разрядами вперед. В первом такте на входы поступают старшие (h-e) разряды слагаемых. В сумматоре 7 формируется -и раз- ряд суммы в вспомогательном коде, который запоминается в элементах 9 и 10 задержки. Одновременно в блоке 8 формируется (п-1)-й разряд суммы (если он отличен от нуля), кото- рый выпадает из сумматора. Во втором такте на входы поступают (Ь-1)-е разряды слагаемых. В сумматоре 7 формируется (ь-1 )-й разряд в вспомогательном коде, которьй опять запоминается в элементах 9 и 10 задержки. Одновременно на входы блока 8 формирования результата из элементов 9 и 10 задержки поступает н -и разряд суммы в вспо могательном коде и информация,необходимая для формирования переноса (на входы A3, А4 и А5). В блоке 8 формирования результата формируется h-й разряд суммы в основном коде. Так как переносы П и П распространяются не более чем на один разряд, формирование н -го разряда суммы во втором такте закан чивается и он считывается с выходов 13-15 устрой- ства. В третьем такте поступают (h-2)-e разряды слагаемых и т.д. Суммирование завершается, когда пройдут все разряды слагаемых или будет получено требуемое число раз- рядов и суммы.

Формула изобретени

Устройство для сложения в избы- точной системе счисления, содержащее двухразрядный комбинационный сумматор, блок формирования результата и два элемента задержки, первый выРедактор П.Коссей

Составитель М.Есенина Техред Л.Сердйкова

4824/48

Тираж 671 .Лодписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ход первого значащего разряда неоткорректированной суммы двухразрядного комбинационного сумматора соединен с входом первого элемента задержки, первый и второй выходы блока формирования результата являются выходами значащих разрядов результата устройства, о т л и - чающееся тем, что, с целью увеличения быстродействия устройства, в него введены элемент И, элемент ИЛИ, информационные входы двухразрядного комбинационного сумматора с первого по четвертый соединены соответственно с входами значаи их разрядов первого и второго слагаемых, вход переноса двухразрядного комбинационного сумматора является входом управления видом операции устройства, выход второго значащего разряда неоткорректированной суммы двухразрядного комбинационного сумматора соединен с входом второго элемента задержки и первым входом элемента И, второй вход которого соединен с входом первого элемента задержки, выход переноса двухразрядного комбинационного сумматора соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента И, первый, второй и третий адресные вхо- ды блока формирования результата соецинены с выходами соответственно первого, второго элементов задержки и выходом элемента ИЛИ, четвертый и пятый адресные входы блока формирования результата соединены соответственно с входами знаковых разрядов первого и второго операндов устройства, третий выход блока формирования результата является выходом знакового разряда результата устройства.

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Экстраполятор видеосигнала изображения | 1989 |

|

SU1718246A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для сложения в избыточной восьмеричной системе счисления | 1982 |

|

SU1040485A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| Устройство вычисления функции @ @ с исправлением ошибок | 1984 |

|

SU1288690A1 |

| Цифровой преобразователь тригонометрических функций | 1986 |

|

SU1327094A1 |

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

| Устройство для сложения в избыточной системе счисления | 1983 |

|

SU1200279A1 |

Изобретение относится к вычислительной технике и может быть использовано при конструировании и разработке специализированных и универсальных последовательных арифметико-логических устройств. Цель изобретения - увеличение быстродействия устройства. Она содержит двухразрядный комбинационный сумматор 7, блок 8 формирования результата, два элемента задержки 9, 10, элемент И It, элемент ИЛИ 12. Сумматор 7 формирует два бита неоткорректированной суммы и перенос, а в блоке 8 формируется h-и разряд суммы в ocHOBiToM коде. Суммирование завершается, когда пройдут все разряды слагаемых или будет получено требуемое число разрядов и суммы. 1 ил. г сл

| Устройство для сложения в избыточной системе счисления | 1980 |

|

SU924698A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сложения в избыточной двоичной системе | 1977 |

|

SU717763A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-07—Публикация

1984-12-25—Подача