(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

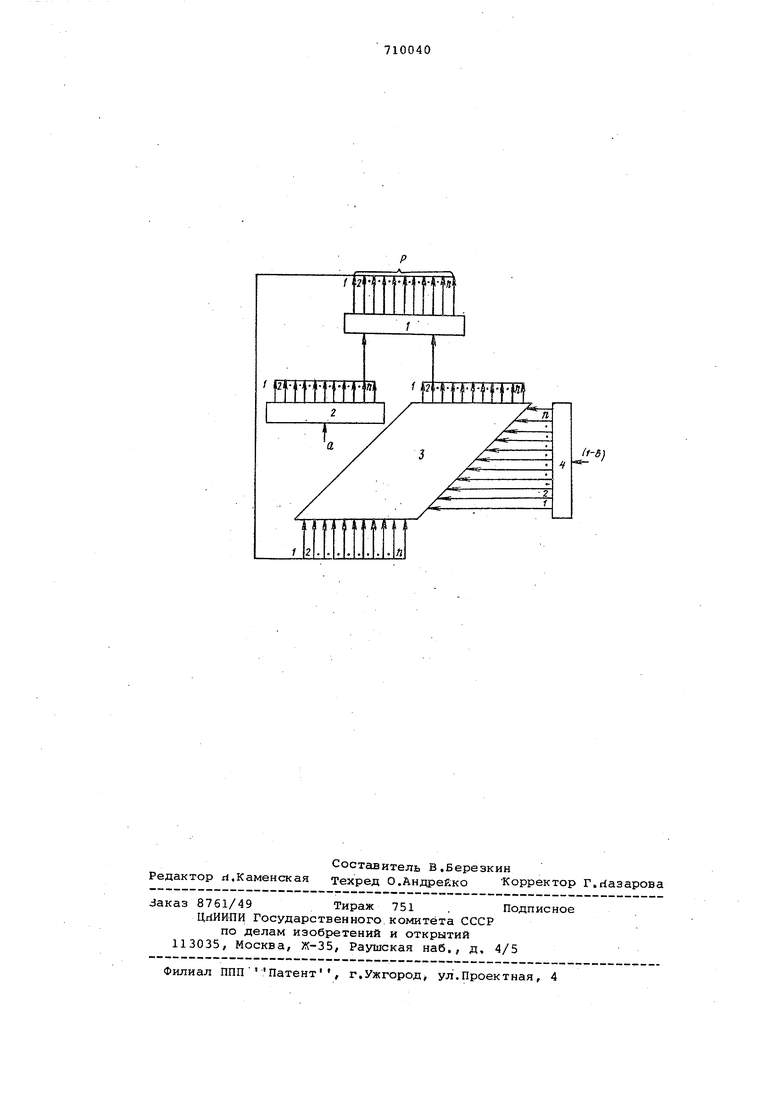

к 2 входам сумматора 1, и выходов которого подключены соответственно к п входам матрицы умпожения 3 (как множимое), к другим и входам матрицы умножения 3 подключены | выходов, регистра делителя 4 (как множитель). В регистре делителя хранится дополнительный код делителя. Делитель предварительно нормализуется.

Процесс деления начинается с момента поступления делимого и дополнительного кода делителя на предварительно обнуленные регистры 2 и-4.

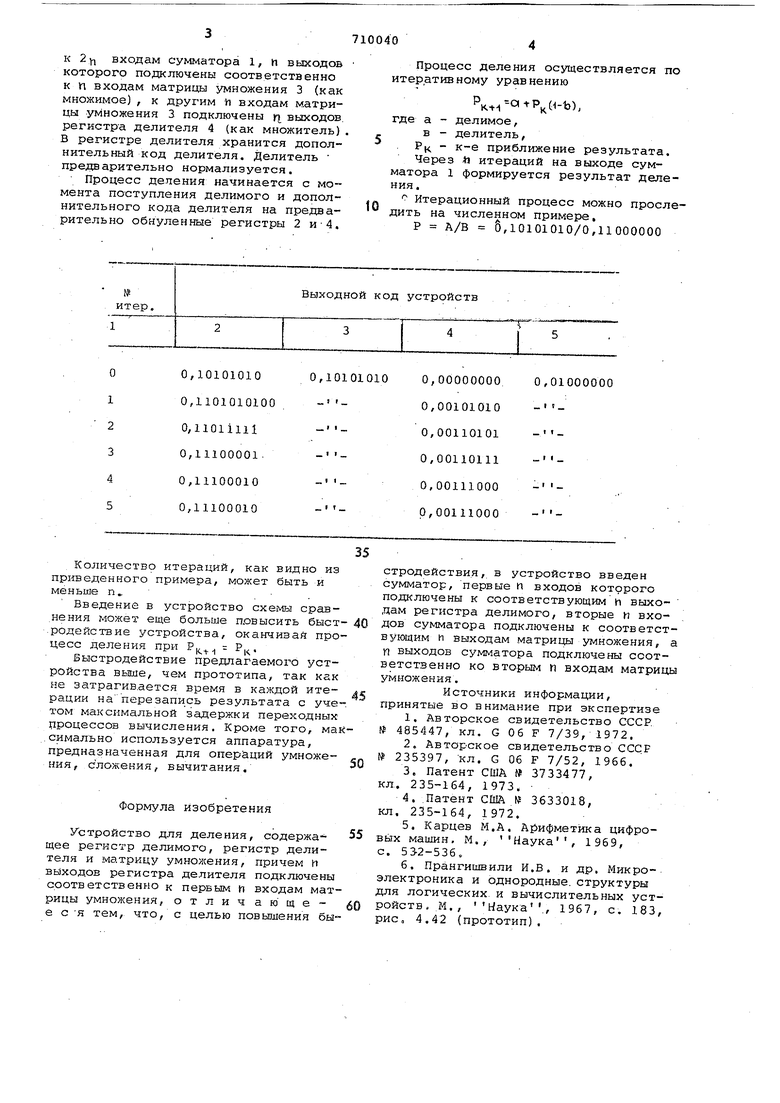

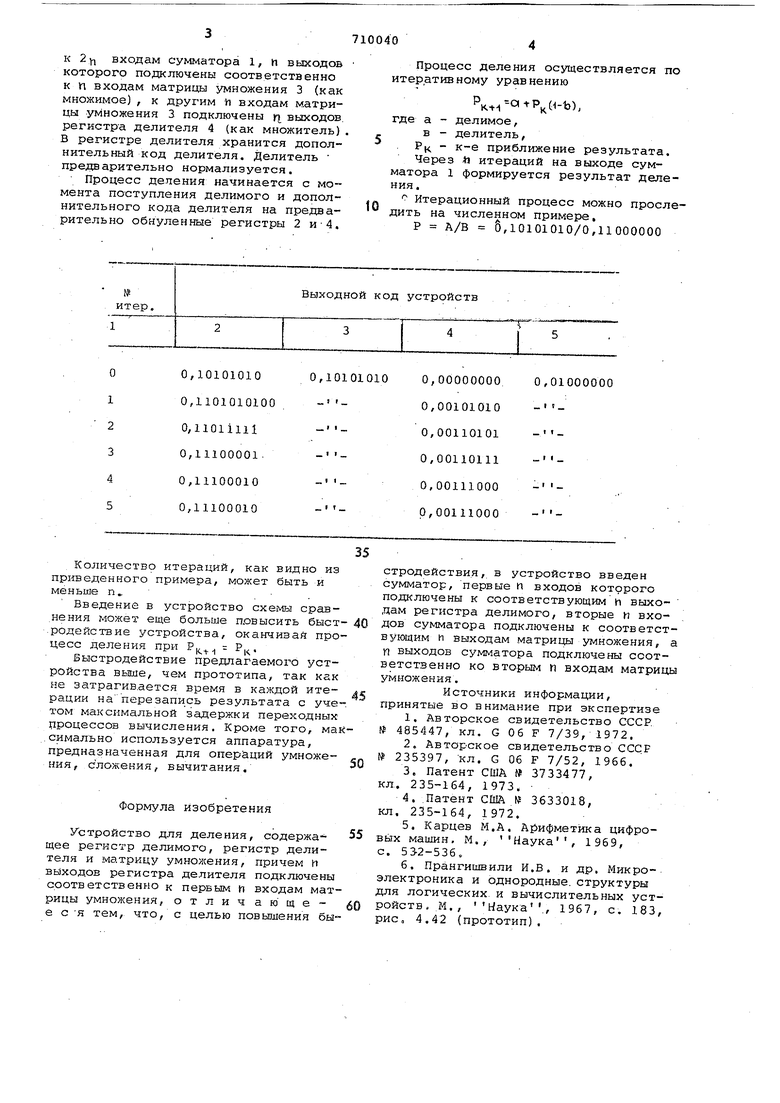

Процесс деления осуществляется по итеративному уравнению

)где а - делимое,

в - делитель,

РК - к-е приближение результата. Через Л итераций на выходе сумматора 1 формируется результат деления .

Итерационный процесс можно проследить на численном примере,

Р А/В 6,10101010/0,11000000

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для операций над матрицами | 1989 |

|

SU1777153A1 |

| Устройство для деления | 1975 |

|

SU579614A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Конвейерное устройство для деления интерационного типа | 1984 |

|

SU1179321A1 |

| Устройство для моделирования биматричных игр | 1986 |

|

SU1388847A1 |

| Устройство для деления | 1979 |

|

SU773618A1 |

| УСТРОЙСТВО ДЛЯ ОСНОВНОГО ДЕЛЕНИЯ МОДУЛЯРНЫХ ЧИСЕЛ | 2013 |

|

RU2559771C2 |

| Устройство для деления чисел | 1981 |

|

SU970356A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

0,10101010

0,10101010

0,1101010100

0,11011111

0,11100001.

0,11100010

0,11100010 Количество итераций, как видно из приведенного примера, может быть и меньше . . Введение в устройство схемы сравнения может еще больше повысить быст родействие устройства, оканчивая про цесс деления при Р - Р|. Быстродействие предлагаемого устройства выше, чем прототипа, так как не затрагивается время в каждой итерации наперезапись результата с уче том максимальной задержки переходных процессов вычисления. Кроме того, ма .симально используется аппаратура, предназначенная для операций умножения, сложения, вычитания. Формула изобретения Устройство для деления, содержащее регистр делимого, регистр делителя и матрицу умножения, причем и выходов регистра делителя подключены соответственно к первым п входам матрицы умножения, отличаю щее сЯ тем, что, с целью повышения бы

0,01000000 стродействия, в устройство введен сумматор, первы-е и входов которого подключены к соответствующим h выходам регистра делимого, вторые и входов сумматора подключены к соответствующим и выходам матрицы умножения, а П выходов сумматора подключены соответственно ко вторым п входам матрицы умножения. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР. № 485447, кл. G 06 F 7/39, 1972. 2.Авторское свидетельство СССР № 235397, кл. G Об F 7/52, 1966. 3. Патент США 3733477, 235-164, 1973. 4..Патент США № 3633018, кл. 235-164, 1972. 5.Карцев М.А. А15ифметика цифровых машин, М., Наука, 1969, с. 53-2-536. 6.Прангишвили И.В. и др. Микроэлектроника и однородные, структуры для логических и вычислительных устройств,.М., Наука., 1967, с. 183, рис, 4.42 (прототип).

Авторы

Даты

1980-01-15—Публикация

1975-03-26—Подача