(54) МУЛЬТИМИКРОПГОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммное устройство управления | 1982 |

|

SU1042017A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256025A1 |

| Микропрограммное устройство управления | 1979 |

|

SU857995A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1104515A1 |

| Микропрограммное устройство управ-лЕНия C КОНТРОлЕМ | 1979 |

|

SU842813A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043653A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных микропрограммных устройств.

Известно микропрограммное устройство управления, содержащее блок памяти, блок проверки условий, триггер управления, элемент И и два регистра адреса 1.

Недостатком данного устройства является низкая производительность, обусловленная недостаточно полным использованием возможностей мультипрограммирования.

Наиболее близким по технической сущности и достигаемому эффекту к предлагаемому является устройство управления с параллельным вьшолнением микропрограмм. Устройство содержит шесть элементов И, два элемента ИЛИ, первый триггер управления, два регистра адреса и блок памяти, первый выход которого соединен с первым выходом усгройства, а второй -- с первым входом блока проверки условий, второй вход которого подключен к .первому входу устройства, а выход -- к первым входам иерного и второго элементов И,

ВЫХОДЫ которых подключены соответственно к первым входам первого и второго регистров адреса, входы которых соединены со вторым и третьим входами устройства соответственно, выход первого регистра адреса подключен к первому входу третьего элемента И, а второй вход первого элемента И соединен с единичным выходом первого триггера управления, единичный вход которого подключен к четвертому входу устройства 2.

10

Недостатком данного устройства является низкая производительность.

Цель изобретения - повышение производительности устройства.

Поставленная цель достигается тем, что

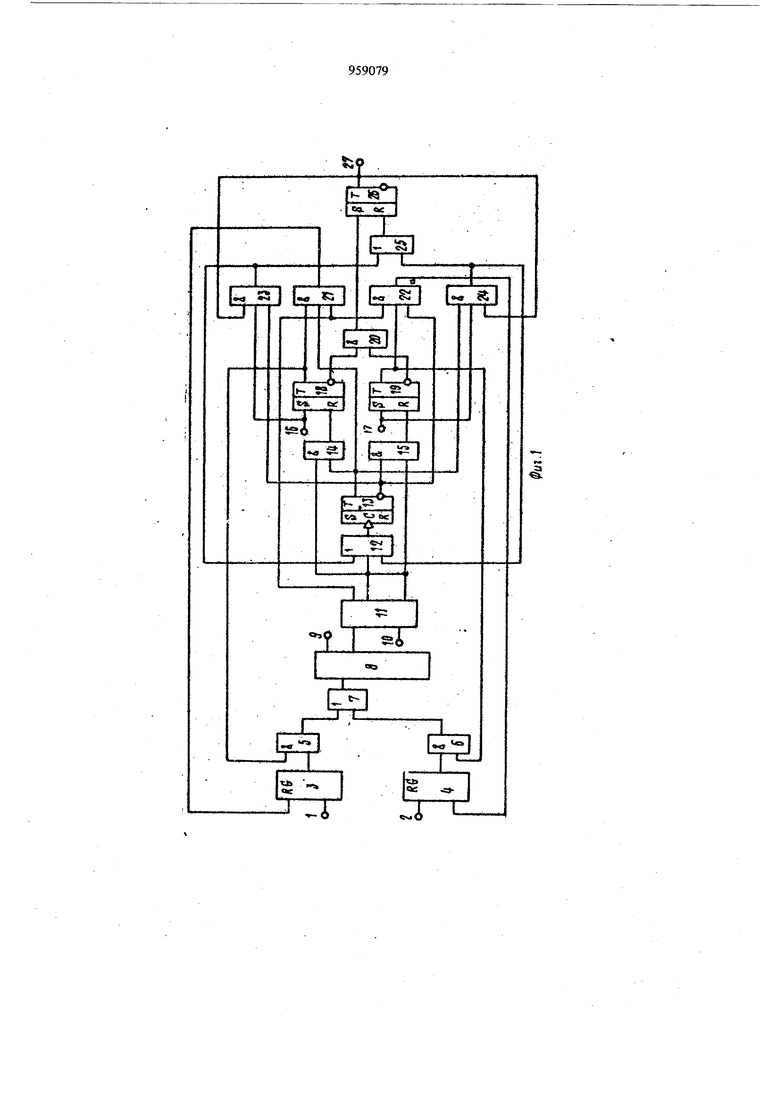

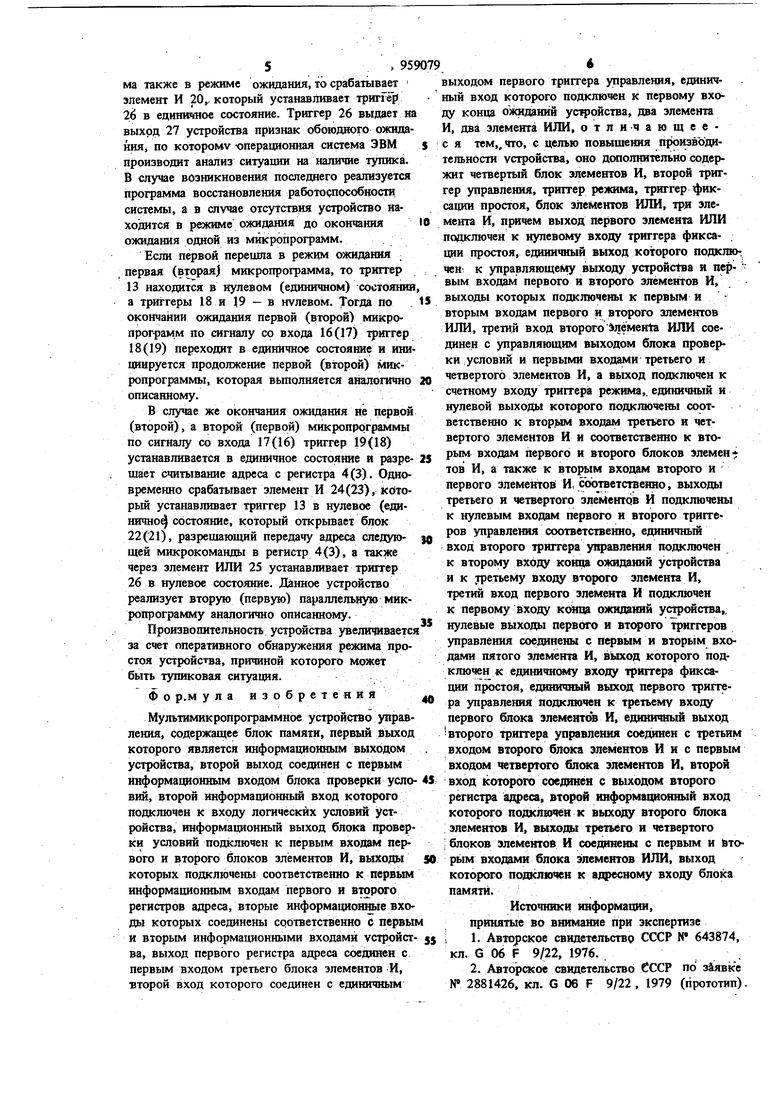

15 в мультимикропрограммное устройство управления, содержащее блок памяти, первый выход которого является информационным выходом устройства, второй выход соедине1Н с первым информационным входом блока провер20ки условий, второй информа1Ь1онньгй вход которого подключен к входу логических условий устройства, информационный выход блока проверки условий подключен в первым вхолам первого и второго блоков элементов И, выхоДы которых подключены соответственно к пер вым информационным входам первого и второ го регистров арреса, вторые информационные входы которых соединены соответственно с .., первым и вторым информационным входакт устройства, выход первого регистра адреса соединен с первым входом третьего блока элементов И, второй вход которого соединен седищ1чнь1м выходом первого триггера управления, едаинчный вход которого подключен к пе вому входу конца ожиданий устройства, два элемента И, два элемента ИЛИ, введены второй триггер управления, четвертый блок элементов И, триггер режима, триггер фиксации простоя, блок элементов ИЛИ, три элемента И, причем выход первого элемента ИЛИ подключен к нулевому входу триггера фиксации простоя, едшошшй выход которого подключен к управлякнцему выходу устройства и первым входам первого и второго элементов И, выходы которых подключены к первым и вторым входам первого и второго элементов ИЛИ, третий вход второго элемента ИЛИ соединен с управляющим выходом блока проверки условий и первыми входами третьего и четвертого элемен тов И, а выход подключен к счетному входу триггера режима, единичный и нулевой выходы которого подключены соответственно к вторым входам третьего и четвертого элементов И и соответственно к вторым входам первого и вто рого блоков элементов И, а также к вторым входам втсфого и первого элементов И соответственно, выхода третьего и четвертого элементов И подключены к нулевым входам первого и второго триггеров управлемЕия соответственно, единтный вход второго триггера управления подключен к второму входу конца ожиданий устройства и к третьему входу второго элемента И, третий вход первого элемента И подключен к первому входу конца ожиданий устройства, нулевые выходы первого и второго триггеров „управления соединены с первым и вторым входами пятого элемента И, выход которого под1 1ючен к единичному входу триггера фиксации простоя, единичный выход первого триггера управления подключен к третьему входу первого блока элементов И, единичный выход второго триггера управления соединен с третьим входом второго блока элементов И и с первым входом четвертого блока элементов И, второй вход которого соединен с выходом второго регистра адреса, второй информационный вход которого подключе к выходу второго блока элементов И, выходы третьего и четвертого блоков элементов И соединены с первьш и вторым входами блока элементов ИЛИ, выход которого подключен к адресному входу блока памяти. На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема блока проверки условий. Устройство содержит первый информационный вход 1 устройства, второй информационный вход 2 устройства, первый и второй регистры 3, 4 адреса, блоки 5, 6 элементов И, блок 7 элементов ИЛИ, блок 8 памяти, информационный выход 9 устройства, вход 10 логических условий устройства, блок 11 проверки условий, элемент ИЛИ 12, триггер 13 режима, элементы И 14, 15, входы 16, 17 конца ожиданий устройства, первый и второй триггеры 18, 19 управления, элемент И 20, блоки 21, 22 элементов И, элементь И 23, 24, элемент ИЛИ 25, триггер 26 фиксации простоя, управляющий выход 27 устройства. Блок проверки условий содержит шифратор 28, дешифратор 29. Устройство работает в режиме мультиплексирования (разделения времени) двух микропрограмм. Адрес очередной микрокоманды первой (второй) параллельной микропрограммы в каждом рабочем такте записан в первом регистре 3 адреса. Если в рассматриваемом рабочем такте функционирует первая (вторая) микропрограмма, то триггер 13 установлен в нулевое (единичное) состояние, триггер 18(19) в единичном состояний, а триггер 19 (18) может быть как в единичном, если вторая (первая) параллельная микропрограмма не находится в режиме ожидания, так и в нулевом состоянии, если вторая (первая) параллельная микропрограмма находится в режиме ожидания. В данном случае адрес очередной микрокоманды первой (второй) микропрограммы через блок 21 (22) поступает в регистр 3(4) и далее через блок 5 (6) и блок 7 в блок 8 памяти, с которого считывается очередная микрокоманда и выполняется аналогишю описанному. Если первая (втор) микропрограмма, выполняющаяся в данном такте, должна перейти в режим ожидания, то в коде очередной микрокоманды содержится npH3ifaK начала ожидания, который индентифицируется блоком 11 проверки условий и через элемент ИЛИ 12 устанавливает триггер 13 в нулевое (еданичное) состояние. При этом открывается элемент И 15, выходным сигналом которого триггер 18(19) устанавливается в нулевое состояние и закрывает блок 5 (6) для передачи адреса очередной микрокоманды на вход блока памяти 8. В этом случае, если триггер 19(18) находится в единичном состоянии, разрешается передача с регистра 4(3) через блок 6(5) адреса очередной микрокоманды второй (первой) микропрограммы, которая функционирует аналогично первой (второй). Если же триггер 19(18) находится в нулевом СОСТОЯН1Ш, вторая (первая) микропрограм5 95 ма также в режиме ожидания, то срабатывает элемент И 20,. который устанавливает триггер 26 в единичное состояние. Триггер 26 выдает на выход 27 устройства признак обоюдного ожидания, по которому операционная система ЭВМ производит анализ ситуации на наличие тупика. В случае возникновения последнего реализуется программа восстановления работоспособности системы, а в случае отсутствия устройство находится в режиме ожидания до окончання ожидания одной из микропрограмм. Если первой перешла в режим ожидания первая (вторая микропрограмма, то триггер 13 находится в нулевом (единичном) состоянии а триггеры 18 и 19 - в нулевом. Jorp по окончании ожидания первой (второй) микропрограмм по сигналу со входа 16(17) триггер 18(19) переходит в единичное состояние и инициируется продолжение первой (второй) микропрограммы, которая вьшолняется аналогично описанному. В случае же окончания ожидания не первой (второй), а второй (первой) микропрограммы по сигналу со входа 17(16) триггер 19(18) устанавливается в единичное состояние и разрешает считывание адреса с регистра 4(3). Одновременно срабатывает элемент И 24(23), который устанавливает триггер 13 в нулевое (единично состояние, который открывает блок 22(21), разрешающий передачу адреса следующей микрокоманды в регистр 4(3), а также через элемент ИЛИ 25 устанавливает триггер 26 в нулевое состояние. Данное устройство реализует вторую (первую) параллельную микропрограмму аналогично описанному. Произнопнтельность устройства увеличивается за счет оперативного обнаружения режима простоя устройства, причиной которого может быть тупиковая ситуация. Ф о р,м у л а изобретения Мультимикропрограммное устройство )равления, содержащее блок памяти, первый выход которого является информациош1ым выходом устройства, второй выход соединен с первым информационным входом блока проверки уелоВИЙ, второй информационный вход которого подключен к входу логических условий устройства, информационный выход блока щюверки условий подключен к первым входам первого и второго блоков элементов И, выходы которых подключены соответственно к первым информационным входам первого и второго регистров адреса, вторые информациоиньте входы которых соединены соответственно с первы и вторым информационнь1ми входами усфойсгва, выход первого регистра адреса соединен с первым входом третьего блока элементов И, второй вход которого соединен с единичным ыходом первого триггера управления, единичый вход которого подключен к первому вхоу конца ояшдаиий устройства, два элемента И, два элемента ИЛИ, отли-чающеес я тем,, что, с целью повышения прризвТэдительности устройства, оно дополнительно содержит четвертый блок элементов И, второй триггер управления, триггер режима, триггер фиксации простоя, блок элементов ИЛИ, три элемента И, причем выход первого элемента ИЛИ подключен к нулевому входу триггера фиксапии простоя, единичный выход которого подклю чен к управляющему выходу устройства и пер- вым входам первого и второго элементов И, выходы которых подключены к первым и вторым входам первого и второго элементов ИЛИ, третий вход второго лемен1а ИЛИ соединен с управляющим выходом блока проверки условий и первыми входами третьего и четвертого элементов И, а выход подключен к счетному входу триггера режима,, единичный и нулевой выходы которого подключены соответственно к вторым входам третьего и четвертого элементов И и соответственно к вторым входам первого и второго блоков элемеН тов И, а также к вторь1м входам второго и первого элементов И, соответственно, выходы третьего и «ктвертого элементов И подключены к нулевым входам первого и второго триггеров управления соответственно, единичный вход второго триггера узфавления подключен к второму входу конца ожиданий устройства и к третьему входу второго элемента И, третий вход Первого элемента И подключен к первому Входу ожиданий устройства, нулевые выхода первого и втсфого триггеров управления соединены с первым и вторь1м входами пятого элемента И, выход которого подключен к едиш1чн лу входу триггера фиксации простоя, единичный выход первого триггера управления подключен к третьему входу первого блока элемента И, единичный выход второго триггера управления соединен с третьим входом второго блока элементов И и с первым входом четвертого блока элементов И, второй вход которого соединен с выходом второго регистра ацфеса, второй информационный вход которого подключен к выходу второго блока элементов И, выходы третьего и четвертого : блоков элементов И соединены с первым и Вторь1м Входами блока элементов ИЛИ, выход которого подключен к адресному входу блока памяти. Источники информации, принятые во вннмание при экспертизе ; 1. Авторское свидетельствр СССР N 643874, кл. G 06 F 9/22, 1976. 2. Авторское свидетельство СССР по зйявке N 2881426, кл. G 06 F 9/22 , 1979 (прототип).

tt

О28

ЛГ

X. 29

Авторы

Даты

1982-09-15—Публикация

1981-01-26—Подача