на

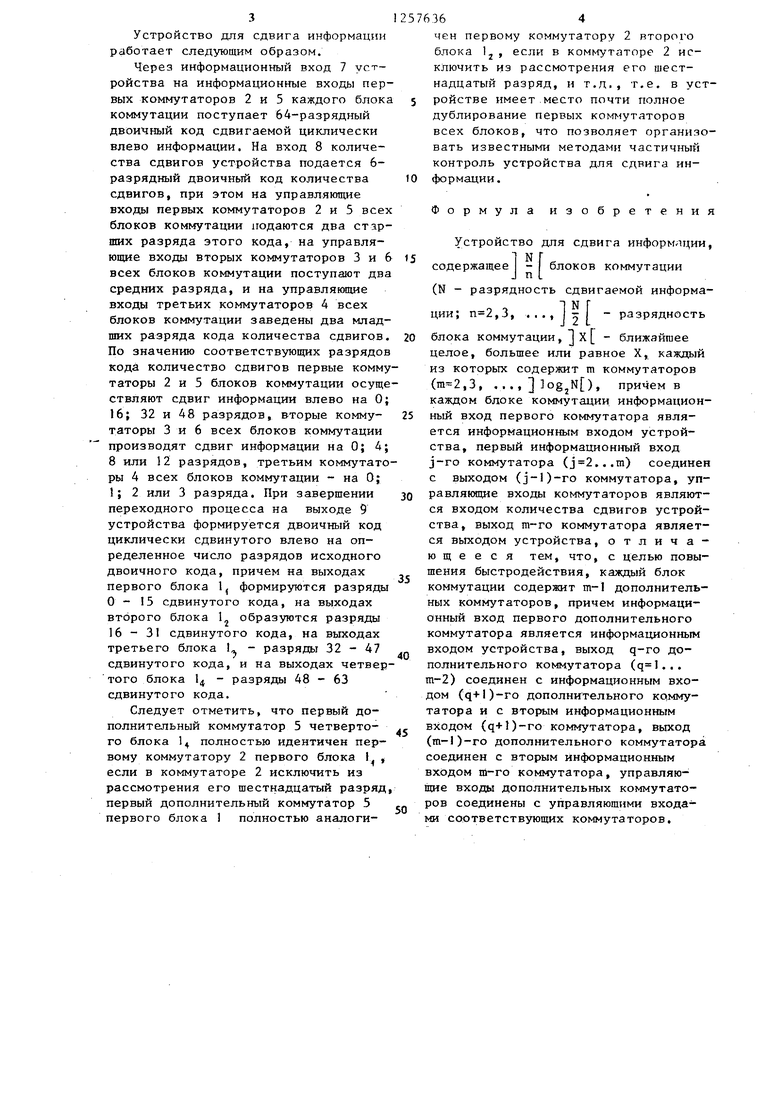

то же, для третьего блока 1 фиг. 2г - то же, для четвертого блока 14 ) I причем слева помещенр диаграммы, относящиеся к первым коммутаторам 2 блоков, а справа размещены диaгpaм гы, относящиеся к первым дополнительным коммутаторам 5 блоков. Цифрами 0-63 внутри диаграмм обозначены номера разрядов сдвигаемой информации, а цифрами 1-31 под диаграммами обозначены номера выходов (разрядов) первых коммутаторов 2 и 5 блоков коммутации. Каждый столбец диаграммы отражает порядок подключения информационных входов одног

разряда коммутатора 2 или 5. I

Управляющие входы первых коммутаторов 2 и 5 блоков коммутации соединены с двумя старшими разрядами 6- разрядного двоичного кода, поступающего на вход 8 количества сдвигов

Изобретение относится к вычиетш- тельной технике, в частности к устройствам коммутации и сдвига, и может быть применено в высокопроизводительных системах обработки информа дни.

Целью изобретения является повышение быстродействия.

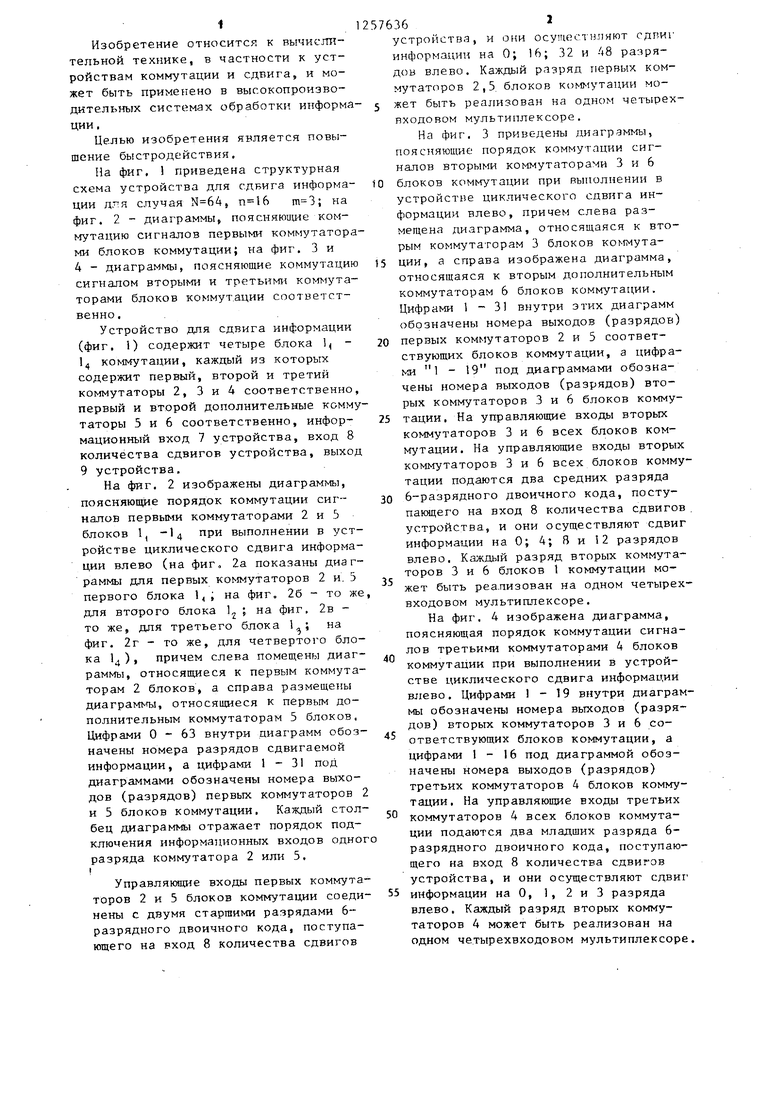

На фиг, 1 приведена структурная схема устройства для сдвига информации для случая , на фиг. 2 - диаграммы, поясняюише коммутацию сигналов первыми коммутаторами блоков коммутации; на фиг. 3 и 4 - диаграммы, поясняющие коммутацию сигналом вторыми и третьими коммутаторами блоков коммутации соответственно t

Устройство для сдвига информации (фиг, 1) содержит четыре блока 1 - Ц коммутации, каждый из которых содержит первы11, второй и третий коммутаторы 2, 3 и 4 соответственно, первый и второй дополнительные коммутаторы 5 и 6 соответственно, информационный вход 7 устройства, вход 8 количества сдвигов устройства, выход 9 устройства.

На фиг. 2 изображены диаграммы, поясняющие порядок коммутации сиг-налов первыми коммутаторами 2 и 5 блоков 1, -l при выполнении в устройстве циклического сдвига информации влево (на фиг, 2а показаны диаграммы для первых коммутаторов 2 и. 5 первого блока 1,; на фиг. 26 - то же для второго блока 1 j на фиг, 2в 10

15

5

20

25

57636J

ycTpoHCTFia, и они осушестнляют сдр,иг информации на 0; 16; 32 и 48 разрядов влево. Каждый разряд первых коммутаторов 2,5, блоков к(.)ммутации может быть реализован на одном четырех- нходовом мультиплексоре.

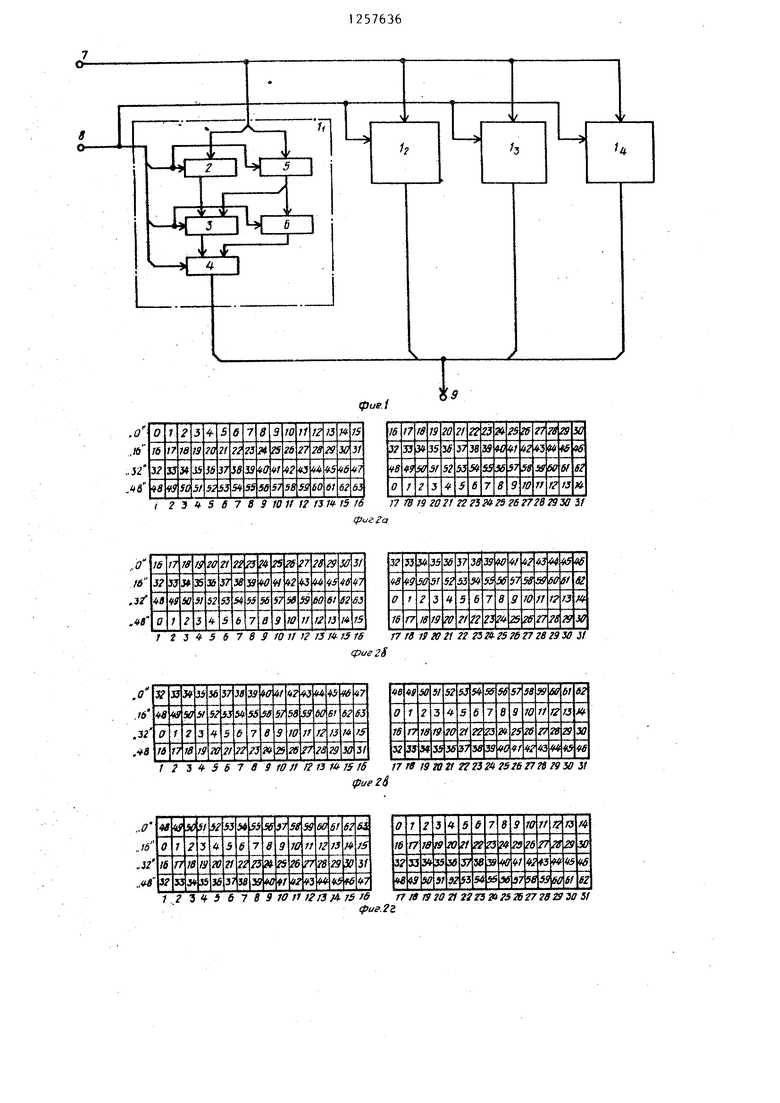

На фиг. 3 приведены диаграммы, поясняющие порядок коммутации сигналов вторыми коммутаторами 3 и 6 блоков коммутации при выполнении в устройстве циклического сдвига информации влево, причем слева размещена диаграмма, относящаяся к вторым коммутаторам 3 блоков коммутации, а справа изображена диаграмма, относящаяся к вторым дополнительным коммутаторам 6 блоков коммутации. Цифрами 1-31 внутри этих диаграмм обозначены номера выходов (разрядов) первых коммутаторов 2 и 5 соответствующих блоков коммутации, а цифрами 1 - 19 под диаграммами обозначены номера выходов (разрядов) вторых коммутаторов 3 и 6 блоков коммутации. На управляющие входы вторых коммутаторов 3 и 6 всех блоков коммутации. На управляющие входы вторых коммутаторов 3 и 6 всех блоков коммутации подаются два средних разряда 6-разрядного двоичного кода, посту- пакмцего на вход 8 количества сдвигов . устройства, и они осуществляют сдвиг информации на 0; 4; Я и 12 разрядов влево. Каждый разряд вторых коммутаторов 3 и 6 блоков 1 коммутации может быть реализован на одном четырех- входовом мультиплексоре.

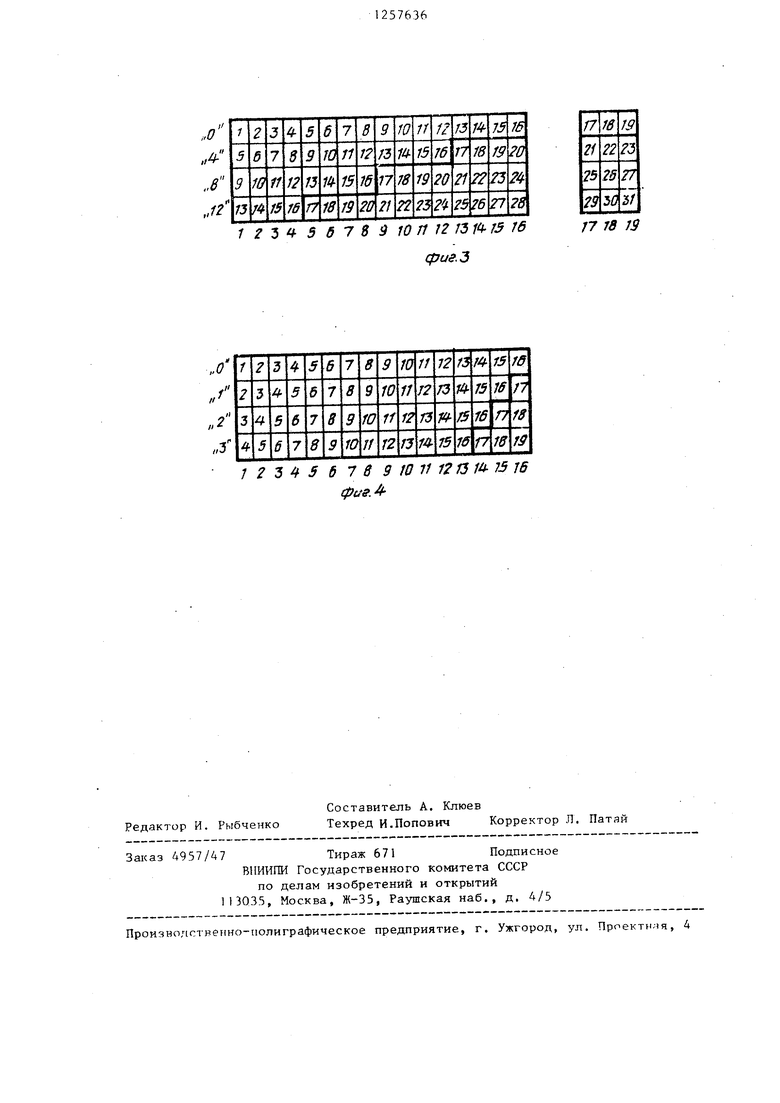

На фиг, 4 изображена диаграмма, поясняющая порядок коммутации сигналов третьими коммутаторами 4 блоков коммутации при выполнении в устройстве циклического сдвига информации влево. Цифрами - 19 внутри диаграммы обозначены номера выходов (разрядов) вторых коммутаторов 3 и 6 соответствующих блоков коммутации, а цифрами 1-16 под диаграммой обозначены номера выходов (разрядов) третьих коммутаторов 4 блоков коммутации. На управляющие входы третьих коммутаторов 4 всех блоков коммутации подаются два младших разряда 6- разрядного двоичного кода, поступающего на вход 8 количества сдвигов устройства, и они осуществляют сдвиг 55 информации на О, 1, 2 и 3 разряда влево. Каждый разряд вторьп коммутаторов 4 может быть реализован на одном четырехвходовом мультиплексоре.

30

35

40

45

50

Устройство для сдвига информации работает следующим образом.

Через информационный вход 7 устройства на информационные входы первых коммутаторов 2 и 5 каждого блока коммутации поступает 64-разрядный двоичный код сдвигаемой циклически влево информации. На вход 8 количества сдвигов устройства подается 6- разрядный двоичный код количества сдвигов, при этом на управляющие входы первых коммутаторов 2 и 5 всех блоков коммутации 11одаются два стар- пшх разряда этого кода, на управляющие входы вторых коммутаторов 3 и 6 всех блоков коммутации поступают два средних разряда, и на управляющие входы третьих коммутаторов 4 всех блоков коммутации заведены два младших разряда кода количества сдвигов. По значению соответствующих разрядов кода количество сдвигов первые коммутаторы 2 и 5 блоков коммутации осуществляют сдвиг информации влево на 0; 16; 32 и 48 разрядов, вторые коммутаторы 3 и 6 всех блоков коммутации производят сдвиг информации на 0; 4; 8 или 12 разрядов, третьим коммутаторы 4 всех блоков коммутации - на 0; 1; 2 или 3 разряда. При завершении переходного процесса на выходе 9 устройства формируется двоичный код циклически сдвинутого влево на определенное число разрядов исходного двоичного кода, причем на выходах первого блока Ц формируются разряды 0-15 сдвинутого кода, на выходах второго блока Ц образуются разряды 16-31 сдвинутого кода, на выходах третьего блока L - разряды 32 - 47 сдвинутого кода, и на выходах четвертого блока 1 - разряды 48 - 63 сдвинутого кода.

Следует отметить, что первый дополнительный коммутатор 5 четвертого блока 1 полностью идентичен первому коммутатору 2 первого блока , если в коммутаторе 2 исключить из рассмотрения его шестнадцатый разряд, первый дополнительный коммутатор 5 первого блока 1 полностью аналоги2576364

чен первому коммутатору 2 второго блока Ij , если в комь{утаторе 2 исключить из рассмотрения его шестнадцатый разряд, и т.д., т.е. в уст- 5 ройстве имеет место почти полное дублирование первых коммутаторов всех блоков, что позволяет организовать известными методами частичный контроль устройства для сдвига ин- 10 формации.

Формула изобретения

15

Устройство для сдвига информлции,

1 N Г « содержащее - блоков коммутации

(N - разрядность сдвигаемой информат 1 1 N Г ции; ,3, . , ,, - I - разрядность

20 блока коммутации, X - ближайшее целое, большее или равное X, каждый из которых содержит m коммутаторов (,3, .... ogjN), причем в каждом блоке коммутации информацион5 ный вход первого коммутатора является информационным входом устройства, первый информационный вход j-ro коммутатора (...m) соединен с выходом (j-l)-ro коммутатора, уп0 равляющие входы коммутаторов являются входом количества сдвигов устройства, выход т-го коммутатора является выходом устройства, отличающееся тем, что, с целью повышения быстродействия, каждый блок коммутации содержит т-1 дополнительных коммутаторов, причем информационный вход первого дополнительного коммутатора является информационным входом устройства, выход q-ro дополнительного коммутатора (... m-2) соединен с информационным входом (q+l)-ro дополнительного крмму- татора и с вторым информационным

, входом (q+1)-го коммутатора, выход (т-I)-го дополнительного коммутатора соединен с вторым информационным входом т-го коммутатора, управляющие входы дополнительных коммутаторов соединены с управляюшими входа

ми соответствующих коммутаторов.

.0

,й

:.32

.43

.16

.32

Ли

f г Ъ 5 6 7 8 3 Wtl ПГв 19JQV 2 2Ъг г52иГтМЪО Ь1

ipueZA

м

м

12 7 8 9 ГО П fft3 о ГГ/в fS 20 21 2 гз гл 516 27 28 гУ ЪО SI

Фие.гг

77 fB tg го 21 кгзг/ гзгб гггвгзза з/

Г7 fs а №21 п гsгt г5 6г72B29зo 31

.0

..6

,.12

1 2 3 5 б 78 9 Ю П 16

фие.З

,.2

„ъ1 2 Ъ 5 б 7 в 9 Ю 11 12131 15 16 фи.

Редактор И. Рыбченко

Составитель А. Клюев

Техред И.Попович Корректор Л, Патай

Заказ 4957/47Тираж 671Подписное

ВИИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проекти;)я, 4

17 78 19

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1325481A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для формирования исполнительных адресов | 1989 |

|

SU1837285A1 |

| Устройство для умножения | 1990 |

|

SU1789981A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

Изобретение относится к вычислительной технике, в частности к устройствам сдвига и коммутации, и может быть применено в высокопроизводительных системах обработки информации. Целью изобретения является повьппение быстродействия. .Поставленная цель достигается тем, что в устройстве для сдвига информации, содержащем М/п блоков коммутации (N - разрядность информации, п - разрядность блока), каждый из которых содержит m коммутаторов ( f Jlog Ы) с соответствующими связями, в каждьй блок коммутации вводится (m-I) коммутатор с соответствующими связями. 4 ил. СП ел Од со О)

| Устройство для сдвига | 1979 |

|

SU864281A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 3610903, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

Авторы

Даты

1986-09-15—Публикация

1985-03-18—Подача