Изобретение относится к вычислительной технике и предназначено для вычисления интегралов.

Цель изобретения - повышение точности.

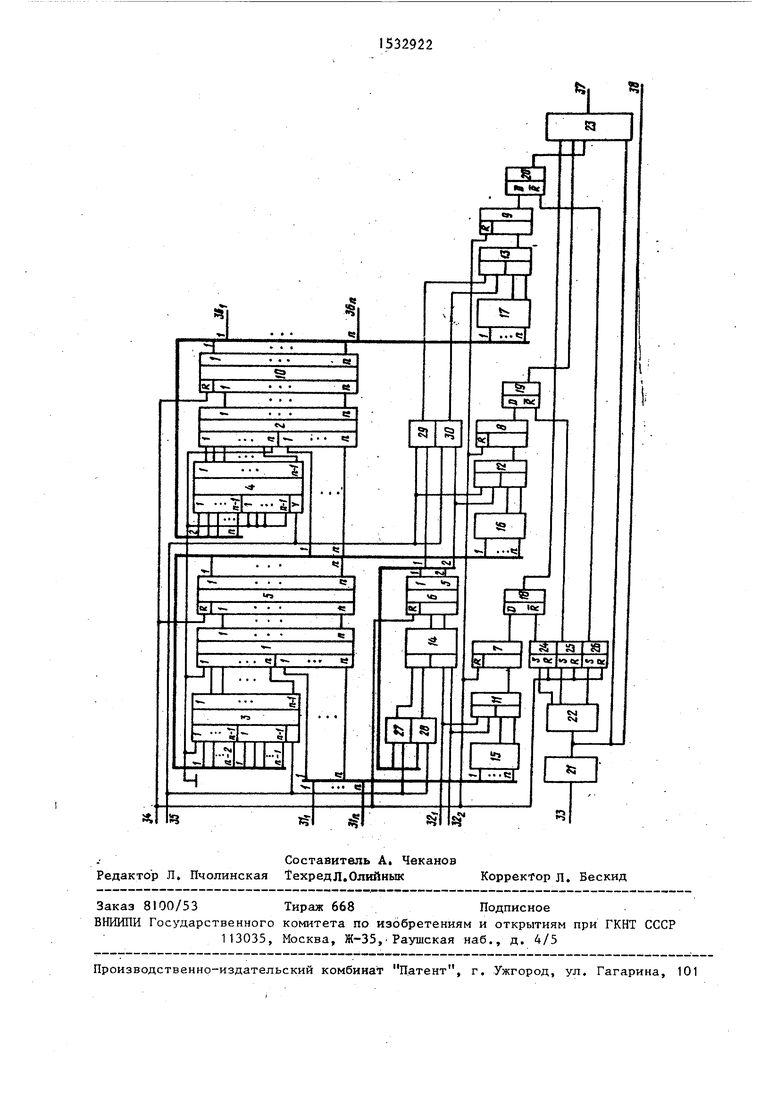

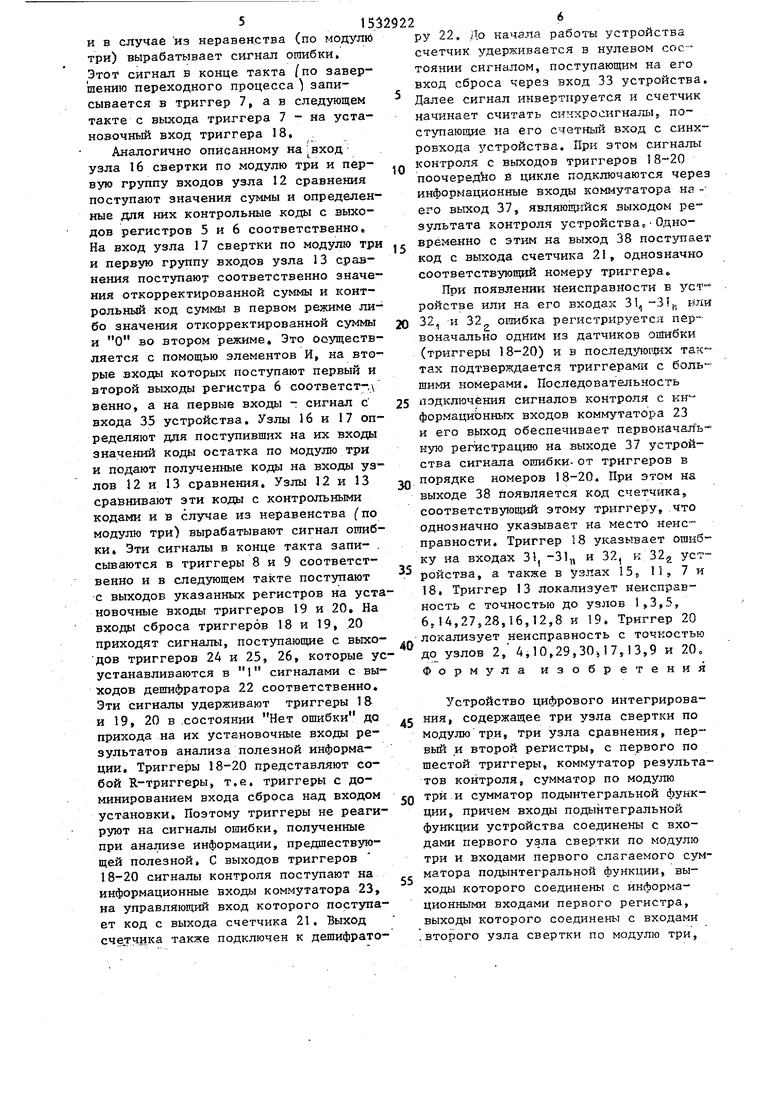

На чертеже представлена схема устройства.

Устройство содержит сумматор 1 подынтегральной функции, сумматор 2 коррекции, первый 3 и второй 4 коммутаторы коррекции, первый 5 и второй 6 регистры, с первого по третий триггеры 7-9, третий регистр 10, с первого по третий узлы 11-13 сравнения, сумматор 14 по модулю три, с первого по третий узлы 15-17 свертки, с четвертого по шестой триггеры 18-20, счетчик 21, дешифратор 22, коммутатор 23 результатов контроля, с седьмого по девятый триггеры 24-26, первый 27 и второй 28 элементы ИСЮГОЧАЮЩЕЕ ИЛИ,первый 29 и второй 30 элемент ты И, входы 31t -31П подынтегральной функции, входы 32,, 32 контрольных разрядов, вход 33 сброса, установочный вход 34, вход 35 задания режима работы, выходы 36,...,36П интеграла, выход 37 результатов контроля и выходы 38 кода типа неисправности.

Устройство работает следующим образом.

3 начале работы импульсом высокого уровня на входе 34 устройства все регистры и триггеры сбрасываются в О. Через входы 31/-31„ устройства на входы сумматора 1 подынтегральной Аункции поступает последовательность значений интегрируемой функции. Работа устройства тактируется путем подачи одних и тех же синхросигналов (для отсчета) на синхровходы всех регистсд

оэ

1C

со

№ №

315

ров, а также на счетный вход счетчика 27.

Интеграл вычисляется за п тактов работы устройства , где k - заданное целое положительное число. Причем интеграл определяется в каждом такте по последним п значениям функции, имеющим различный вес, Весовая характеристика входной величины, пришедшей в первом такте, уменьшается по мере прихода последующих входных величин. Наибольший вес имеет входная величина, пришедшая последней Значение интеграла определяется как взвешенная сумма последних п значений функции, деленная на п,

Устройство может работать в двух режимахс В первом режиме взвешенная сумма вычисляется как:

I M

fi

тг

I где f, - очередное входное значение

функции.

Во втором режиме взвешенная сумма . вычисляется как;

f

4 +fe

п/г

+ . ,+fn/e

3 ZI4

f,Ј- 2

i t

oTTT

4

Первый режим устанавливается высоким уровнем на входе 35 работы устройства, а второй - низким уровнем. При работе устройства в первом режи- ме в каждом последующем такте работы устройства на первую группу входов сумматора 1 подынтегральной функции подается сдвинутая вправо на один разряд сумма, полученная в преды- дущем такте и прошедшая через регистр 5 и вторую группу входов коммутаторов 3. Таким образом, сумматор 1 и регистр 5 образуют накапливающий сумматор. Результат сложения поступае на вторую группу входов сумматора 2 коррекции, в каждом такте складывается с нулем (т.е. остается без изменения) и, пройдя через регистр 10, по

0

0

5

0

35

40

,,

ступает на выходы 36,,--36П интеграла устройства.

При работе устройства во втором режиме в каждом последующем такте работы устройства на первую группу входов сумматора I подынтегральной функции подается сдвинутая вправо на два разряда сумма, полученная в предыдущем такте и прошедшая через регистр 5 и первую группу входов коммутатора 3. Результат сложения поступает на вторую группу входов сумматора 2 коррекции и,, пройдя через регистр 10 и первую группу входов коммутатора 4, поступает сдвинутым на один разряд влево на вторую группу входов сумматора 2. Таким образом, сумматор 2 и регистр 10 образуют накапливающий сумматор, который совместно -с коммутатором 4 осуществляет умножение взвешенной суммы на три. С выходов регистра 10 результат поступает на выходы ,, интеграла устройства. Деление суммы на число п осуществляется путем перенесения весовых функций результата на k раэря- i дов влево.

Одновременно с поступлением на входы устройства значений Функции на входы 324 и 32П устройства подаются соответствующие этим входным значениям контрольные коды, являющиеся остатком по модулю три входных значений функции Последовательность контрольных кодов поступает соответственно на вторую группу входов сумматора 14 по модулю три, который вместе с регистром 6 образует накапливающий сумматор. На первую группу входов сумматора 14 в первом режим поступают инверсные значения с выхода регистра 6, а во втором режиме - прямое значение с выхода регистра 6. Это осуществляется путем прохода значений с выхода регистра 6 через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 27 и 28, на вторые входы которых поступает уровень с входа 35 устройства.

Поступающие через входы 31,,-ЗЦ, 321 и 32г устройства значения функции и их контрольные коды подаются также на входы узла 15 свертки и первую группу входов узла 11 сравнения соответственно. Узел 15 определяет код остатка от деления значения функции на три и подает его на вторую группу входов узла 11 сравнения. Узел 11 сравнивает его с контрольным кодом

и в случае из неравенства (по модули три) вырабатывает сигнал ошибки.

Этот сигнал в конце такта (по завершению переходного процесса } записывается в триггер 7, а в следующем такте с выхода триггера 7 - на установочный вход триггера 18,

Аналогично описанному на вход узла 16 свертки по модулю три и первую группу входов узла 12 сравнения поступают значения суммы и определенные для них контрольные коды с выходов регистров 5 и 6 соответственно На вход узла 17 свертки по модулю три и первую группу входов узла 13 сравнения поступают соответственно значения откорректированной суммы и контрольный код суммы в первом режиме либо значения откорректированной суммы и О во втором режиме. Это осуществляется с помощью элементов И, на вторые входы которых поступают первый и второй выходы регистра 6 соответст-.

венно, а на первые входы - сигнал с

входа 35 устройства. Узлы 16 и 17 определяют дли поступивших на их входы значений коды остатка по модулю три и подают полученные коды на входы узлов 12 и 13 сравнения. Узлы 12 и 13 сравнивают эти коды с контрольными кодами и в случае из неравенства (по модулю три) вырабатывают сигнал ошибки. Эти сигналы в конце такта записываются в триггеры 8 и 9 соответственно и в следующем такте поступают с выходов указанных регистров на установочные входы триггеров 19 и 20. На входы сброса триггеров 18 и 19, 20 приходят сигналы, поступающие с выхо- дов триггеров 24 и 25, 26, которые ус устанавливаются в 1 сигналами с выходов дешифратора 22 соответственно. Эти сигналы удерживают триггеры 18- и 19, 20 в состоянии Нет ошибки до прихода на их установочные входы результатов анализа полезной информации. Триггеры 18-20 представляют собой R-триггеры, т.е. триггеры с доминированием входа сброса над входом установки. Поэтому триггеры не реагируют на сигналы ошибки, полученные при анализе информации, предшествующей полезной, С выходов триггеров 18-20 сигналы контроля поступают на информационные входы коммутатора 23, на управляющий вход которого поступает код с выхода счетчика 21. Выход счетчика также подключен к дешифрато-

to

.,

20

25

30

.

ру 22. До начала работы устройства счетчик удерживается в нулевом сое тоянии сигналом, поступающим на его вход сброса через вход 33 устройства. Далее сигнал инвертируется и счетчик начинает считать сичхросигналы, поступающие на его счетный вход с сннх- ровхоца устройства. При этом сигналы контроля с выходов триггеров 18-20 поочередно в цикле подключаются через информационные входы коммутатора на - его выход 37, являющийся выходом результата контроля устройства,Одновременно с этим на выход 38 поступает код с выхода счетчика 21, однозначно соответствующий номеру триггера

При появлении неисправности в уст1- ройстве или на его входах 31,, пя 321 и 32 ошибка регистрируется первоначально одним из датчиков ошибки (триггеры 18-20) и в последующих тач тах подтверждается триггерами с большими номерами. Последовательность подключения сигналов контроля с информационных входов коммутатора 23 и его выход обеспечивает первоначальную регистрацию на выходе 37 устройства сигнала ошибки- от триггеров в порядке номеров 18-20, При этом на выходе 38 появляется код счетчика, соответствующий этому триггеру, что однозначно указывает на место неисправности. Триггер 18 указывает ошиб5

5

0

ку на входах

31, -31П

и 32, к 32,

5

устройства, а также в узлах 15S 11, 7 и 18. Триггер 13 локализует неисправность с точностью до узлов 1,3,5, 6.14,27,28,16,12,8 и 19. Триггер 20 локализует неисправность с точностью до узлов 2, 4,10,29,30,17,13,9 и 20„ Формула изобретения

Устройство цифрового интегрирования, содержащее три узла свертки по модулю три, три узла сравнения, первый и второй регистры, с первого по шестой триггеры, коммутатор результатов контроля, сумматор по модулю три и сумматор подынтегральной функции, причем входы подынтегральной функции устройства соединены с входами первого узла свертки по модулю три и входами первого слагаемого сумматора подынтегральной функции, выходы которого соединены с информационными входами первого регистра, выходы которого соединены с входами второго узла свертки по модулю три,

7153

входы контрольных разрядов устройс ва соединены с входами первой группы первого узла сравнения и входами первого слагаемого сумматора по модулю три, выходы которого соединены с информационными входами второго регистра, выходы которого соединены с входами первой группы второго узла сравнения, выходы первого, второго и третьего узлов сравнения соединены с информационными входами первого, второго и третьего триггеров соответственно, выходы которых соединены

8

третьего регистра, выходы которого соединены с входами третьего узла свертки по модулю три и выходами ин- теграла устройства, i-й выход (,n) третьего регистра соединен с (i-l)-M входом первой группы информационных входов второго коммутатора коррекции i-й выход (,п-1) которого соединен с i-м входом группы входов второго слагаемого сумматора коррекции, 1-й (,п-1) выход первого регистра соединен с i-м входом второй группы информационных входов первого ком

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифрового интегрирования | 1986 |

|

SU1345192A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Устройство вычисления функции @ @ с исправлением ошибок | 1984 |

|

SU1288690A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1977 |

|

SU732920A1 |

| Устройство для обработки чисел в избыточном последовательном коде | 1985 |

|

SU1330629A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

Изобретение относится к вычислительной технике и предназначено для вычисления интегралов. Цель изобретения - повышение точности. Устройство содержит сумматор подинтегральной функции, сумматор коррекции, коммутаторы коррекции, регистры , триггеры, узлы сравнения, сумматор по модулю три, узлы свертки, счетчик, дешифратор, коммутатор результатов контроля, элементы Исключающее ИЛИ, элементы И. Цель достигнута за счет вычисления интеграла по N последним значениям функции, имеющим различный вес. 1 ил.

20

25

с информационными входами четвертого 15 мутатора коррекции, первый вход первой группы информационных входов первого коммутатора коррекции, первый вход группы входов второго слагаемого сумматора подынтегральной функции, входы второй группы информационных входов второго коммутатора коррекции и i-й вход группы входов второго слагаемого сумматора коррекции соединены с шиной логического нуля устройства, вход задания режима работы устройства соединен с управляющими входами первого и второго коммутаторов коррекции, а также первыми входами элементов И и элементов ИСКЛЮЧАЮЩЕЕ 30 ИЛИ, установочный вход устройства соединен с входами сброса всех регистров и триггеров, кроме четвертого, пятого и шестого, вход синхронизации устройства соединенic входом синхронизации третьего регистра, первый и второй выходы второго регистра соединены с вторыми входами первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно, входами второй группы второго узла сравнения и вторыми входами первого и второго элементов И соответственно, выходы которых соединены с первым и вторым входами второй группы третьего узла сравнения соответственно, выхода первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с первым к вторым входами второй группы первого узла сравнения соответственно, с первого по третий

пятого и шестого триггеров соответственно, выходы которых соединены с информационными входами коммутатора результатов контроля, управляющие которого соединены с выходами сметчика, а выход подключен к выходу результата контроля устройства, выходы первого, второго узлов свертки по модулю три соединены с входами вторых групп первого, второго узлов сравнения соответственно, выходы третьего узла свертки по модулю три соединены с входами первой группы третьего узла сравнения, вход сброса устройства соединен с входом сброса счетчика, выходы которого соединены с выходами кода типа неисправности устройства, входы синхронизации пер- його и второго регистров, счетчика и с первого по шестой триггеров соединены с входом синхронизации устрой Ства, отличающееся тем, что,с целью повышения точности, в йего введены два коммутатора коррекции, третий регистр, сумматор коррекции, дешифратор, с седьмого по девятый триггеры, два элемента И и два Элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, причем 1-й выход первого регистра соединен с (1-Н)-м информационным входом первой д5 группы (,п, где п - разрядность подынтегральной функции) первого коммутатора коррекции, 1-1 (,п-1); выход которого соединен с (1Н)м

ВХОДОМ ГРУППЫ ВХОДОВ ВТОРОГО Слагав- JQ

мого сумматора подынтегральной функции, выходы первого регистра соединены с входами первого слагаемого сумматора коррекции, выходы которого соединены с информационными входами

35

40

выходы дешифратора .соединены с входами установки 1 с седьмого по девятый триггеры, выходы которых соединены с входами установки в О с четвертого по шестой триггеры соответственно.

выходы дешифратора .соединены с входами установки 1 с седьмого по девятый триггеры, выходы которых соединены с входами установки в О с четвертого по шестой триггеры соответственно.

| Каляев А.В | |||

| Микропроцессорные системы с программируемой архитектурой | |||

| М.: Радио и связь, 1984, с010б, рис | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство цифрового интегрирования | 1986 |

|

SU1345192A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Полин, Николенко | |||

Авторы

Даты

1989-12-30—Публикация

1988-05-10—Подача