Изобретение откосится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования цифровых величин в аналоговые.

Цель изобретения - повышение быстродействия и расширение области применения за счет преобразования двоичного кода.

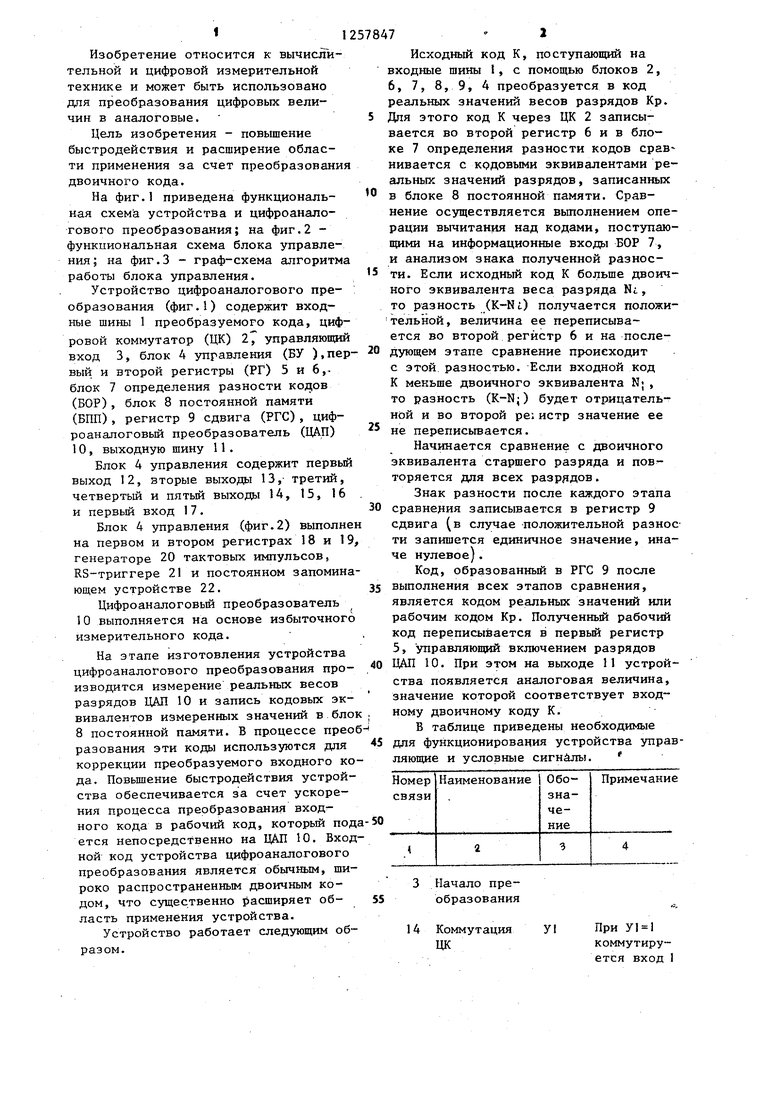

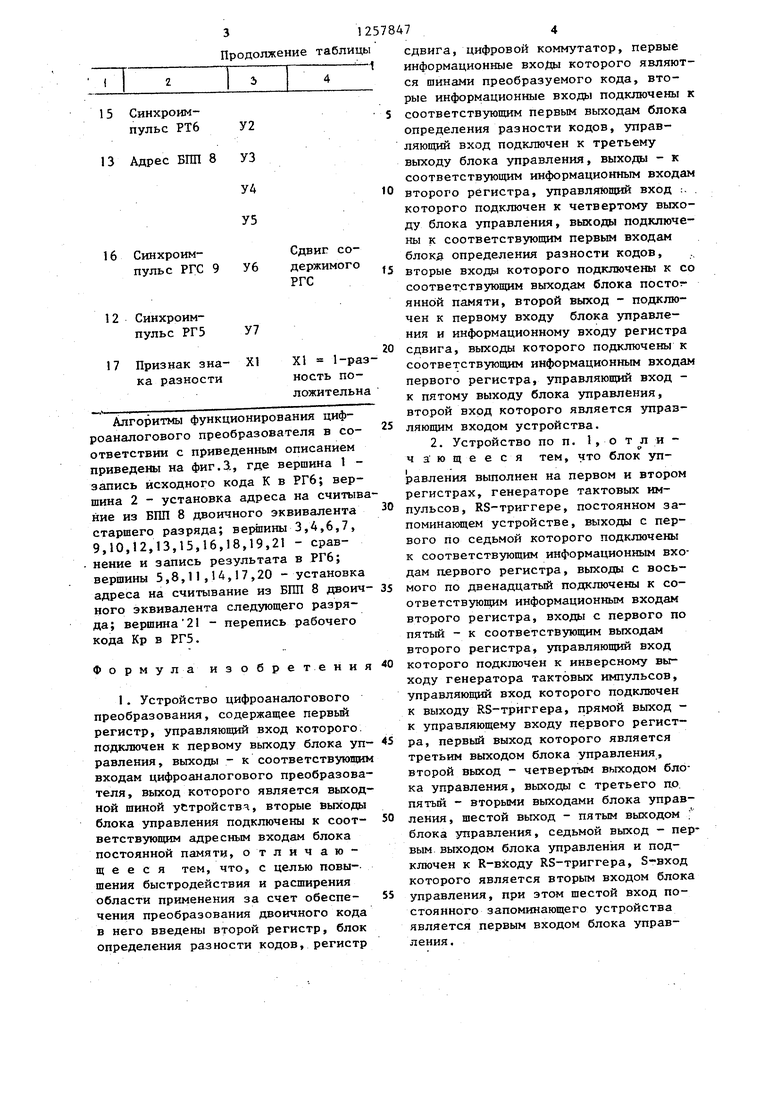

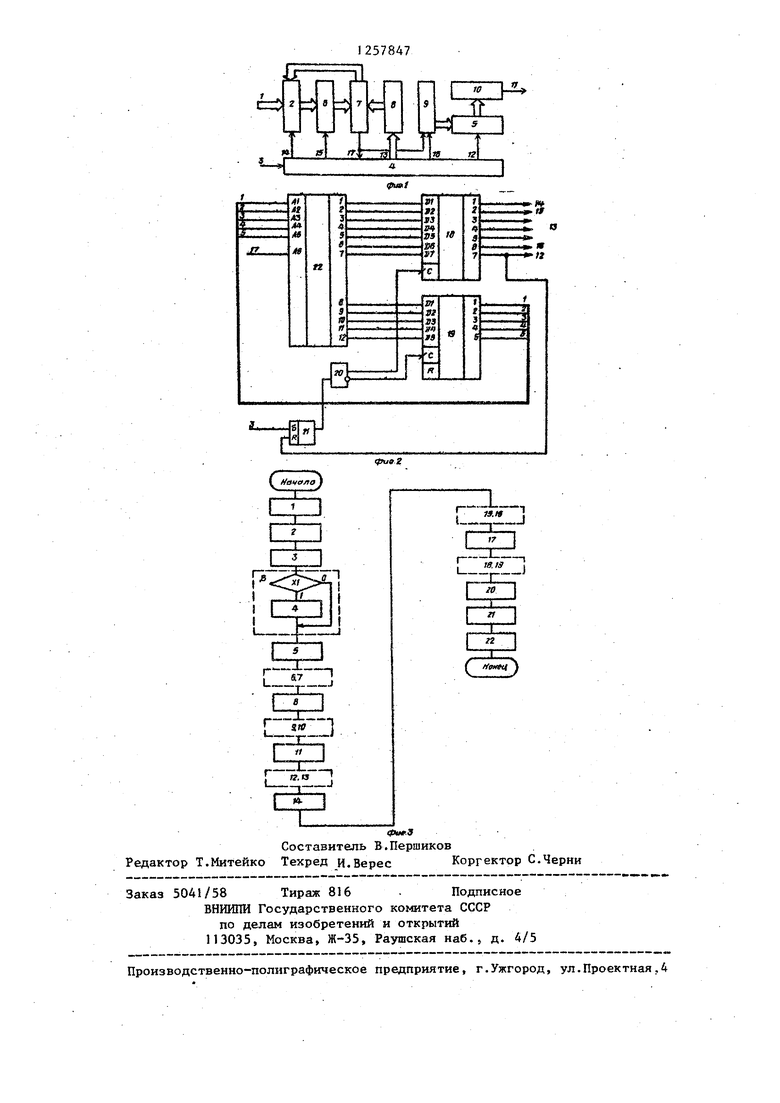

На фиг.1 приведена функциональная схема устройства и цифроанало- гового преобразования; на фиг.2 - функциональная схема блока управления ; на фиг.З - граф-схема алгоритма работы блока управления.

Устройство цифроаналогового преобразования (фиг.1) содержит входные шины 1 преобразуемого кода, цифровой коммутатор (ЦК) 2, управляюш 1Й вход 3, блок 4 управления (БУ ),пер- вый и второй регистры (РГ) 5 и 6,- блок 7 определения разности код;ов (ВОР), блок 8 постоянной памяти (БПП), регистр 9 сдвига (РГС), циф- роанапоговый преобразователь (ЦАП) 10, выходную шину 11.

Блок 4 управления содержит первый выход 12, вторые выходы 13,- третий, четвертьш и пятьм выходы 14, 15, 16 и первый вход 17.

Блок 4 управления (фиг.2) выполне на первом и втором регистрах 18 и 19 генераторе 20 тактовых импульсов, RS-триггере 21 и постоянном запоминающем устройстве 22.

Цифроаналоговый преобразователь 10 выполняется на основе избыточного измерительного кода.

На этапе изготовления устройства цифроаналогового преобразования производится измерение реальных весов разрядов ЦАП 10 и запись кодовых эквивалентов измеренных значений в бло В постоянной памяти. В процессе прео разования эти коды используются для коррекции преобразуемого входного кода. Повышение быстродействия устройства обеспечивается за счет ускорения процесса преобразования входного кода в рабочий код, который под ется непосредственно на ЦАП 10. Входной код устройства цифроаналогового преобразования является обычным, широко распространенным двоичным кодом, что существенно расширяет область применения устройства.

Устройство работает следующим образом.

o

15

25

20

5 50

30

35

40

Исходный код к, поступающий на входные шины 1, с помощью блоков 2, 6, 7, 8, 9, 4 преобразуется в код реальных значений весов разрядов Кр. Для этого код К через ЦК 2 записывается во второй регистр бив блоке 7 определения разности кодов срав нивается с кодовыми эквивалентами реальных значений разрядов, записанных в блоке 8 постоянной памяти. Сравнение осуществляется вьшолнением операции вычитания над кодами, поступающими на информационные входа БОР 7, и анализом знака полученной разности. Если исходный код К больше двоичного эквивалента веса разряда Ni., то разность (K-Ni.) получается положи- тельной, величина ее переписывается во второй регистр 6 и на последующем этапе сравнение происходит с этой разностью. Если входной код К меньше двоичного эквивалента N;, то разность (K-NJ) будет отрицательной и во второй ре; истр значение ее не переписьгоается.

Начинается сравнение с двоичного эквивалента старшего разряда и пов торяется для всех разрядов.

Знак разности после каждого этапа сравнения записывается в регистр 9 сдвига (в случае положительной разнос ти запишется единичное значение, иначе нулевое).

Код, образованный в РГС 9 после выполнения всех этапов сравнения, является кодом реальных значений или рабочим кодом Кр. Полученньй рабочий код переписывается в первый регистр 5, управляющий включением разрядов ЦАП 10. При этом на выходе 11 устройства появляется аналоговая величина, значение которой соответствует входному двоичному коду к.

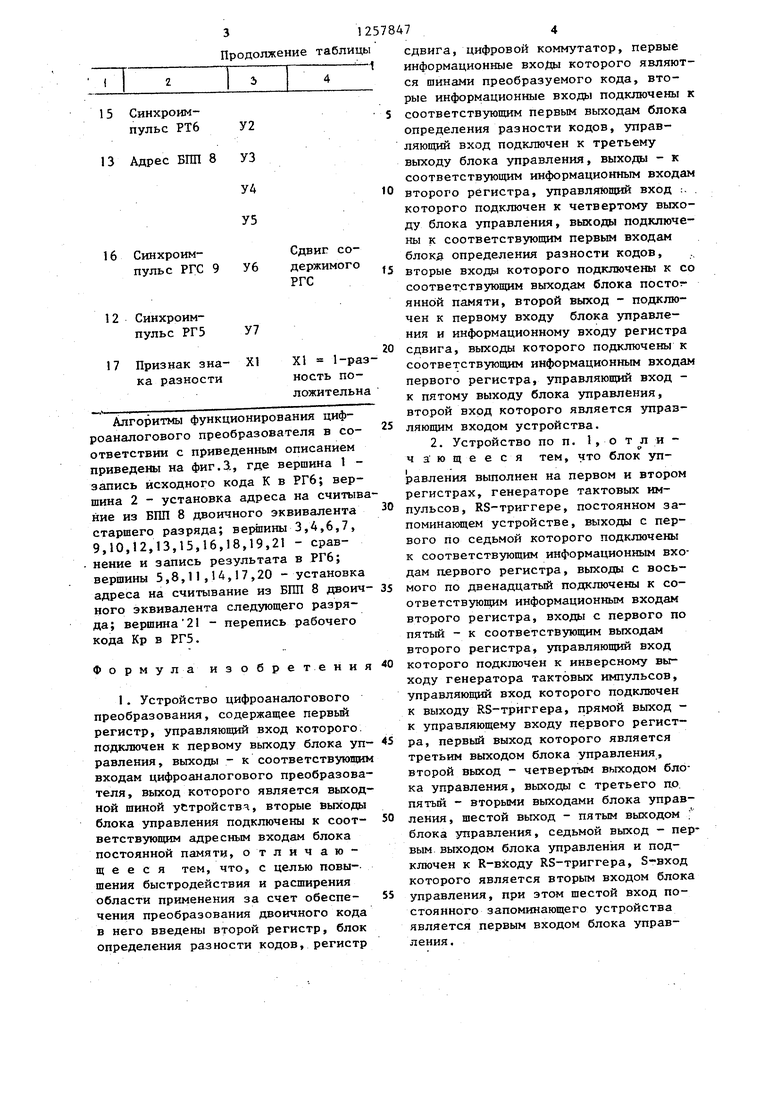

в таблице приведены необходимые для функционирования устройства управляющие и условные СИГНАЛЫ.

14

Начало преобразования

Коммутация ЦК

У1

При

коммутируется вход 1

Продолжение таблицы

15

Синхроимпульс РТ6

У2

13 Адрес БПП 8 УЗ

УА

У5

Синхроимпульс РГС 9

У6

Сдвиг содержимогоРГС

Синхроимпульс РГ5

Признак знака разности

У7

XI

XI 1-разность положительна

Алгоритмы функционирования циф- роаналогового преобразователя в соответствии с приведенным описанием приведены на фиг.З., где вершина 1 - запись исходного кода К в РГ6; вершина 2 - установка адреса на считывние из БПП 8 двоичного эквивалента старшего разряда; вершины 3,4,6,7, 9,10,12,13,15,16,18,19,21 - сравнение и запись результата в РГ6; вершины 5,8,11,14,17,20 - установка адреса на считывание из БПП 8 двоич ного эквивалента следующего разряда; вершина 21 - перепись рабочего кода Кр в РГ5.

Формула изобретения

1. Устройство цифроаналогового преобразования, содержащее первый регистр, управляющий вход которого подключен к первому выходу блока уп- равления, выходы - к соответствующим входам цифроаналогового преобразователя, выход которого является выходной шиной устройства, вторые выходы блока управления подключены к соот- ветствующим адресным входам блока постоянной памяти, отличающееся тем, что, с целью повы-- шения быстродействия и расширения области применения за счет обеспе- чения преобразования двоичного кода в него введены второй регистр, блок определения разности кодов, регистр

0

s

0

5

сдвига, цифровой коммутатор, первые информационные входы которого являются шинами преобразуемого кода, вторые информационные входы подключены к соответствующим первым выходам блока определения разности кодов, управляющий вход подключен к третьему выходу блока управления, выходы - к соответствующим информационным входам второго регистра, управляющий вход :. . которого подключен к четвертому выходу блока управления, выходы подключены к соответствующим первым входам блоки определения разности кодов, вторые входы которого подключены к со соответствующим выходам блока постот- янной памяти, второй выход - подключен к первому входу блока управления и информационному входу регистра сдвига, выходы которого подключены к соответствующим информационным входам первого регистра, управляющий вход - к пятому выходу блока управлення, второй вход которого является управляющим входом устройства.

2. Устройство по п. 1, о т л и - ч зюще е ся тем, что блок управления выполнен на первом и втором регистрах, генераторе тактовых импульсов, RS-триггере, постоянном запоминающем устройстве, выходы с первого по седьмой которого подключены к соответствующим информационным входам первого регистра, выходы с восьмого по двенадцатый подключены к соответствующим информационным входам второго регистра, входы с первого по пятый - к соответствующим выходам второго регистра, управляющий вход которого подключен к инверсному выходу генератора тактовых импульсов, управляющий вход которого подключен к выходу RS-триггера, прямой выход - к управляющему входу первого регистра, первый выход которого является третьим выходом блока управления, второй выход - четвертым выходом блока управления, выходы с третьего п.о. пятый - вторыми выходами блока управления, шестой выход - пятым выходом f блока управления, седьмой выход - первым выходом блока управлення и подключен к R-входу RS-триггера, S-вход которого является вторым входом блока управления, при этом шестой вход постоянного запоминающего устройства является первым входом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифроаналогового преобразования | 1984 |

|

SU1248072A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1231609A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1221750A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1223368A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221754A1 |

Изобретение относится к области вычислительной и цифровой измерительной техники и может быть использовано для преобразования цифровых величин в аналоговые. Изобретение позволяет повысить быстродействие и расширить область применения за счет преобразования обычного двоичного кода устройством, выполненным на базе избыточного измерительного кода , что обеспечивается введением цифрового коммутатора, блока определения разности кодов, второго регистра и регистра сдвига. Измеренные на этапе изготовления коды реальных весов всех разрядов цифроаналогового преобразо- -вания записываются в блок постоянной памяти и затем используются при преобразовании входного двоичного ко- да в рабочий избыточный измерительный код, который поступает на вход цифроаиалогового преобразователя. Повышение быстродействия обеспечивается за счет ускорения процесса преобразования входного кода в рабочий код. 1 з.п. ф-лы, 3 ил. 9

| Цифроаналоговый преобразователь | 1979 |

|

SU864548A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1200422A1 |

Авторы

Даты

1986-09-15—Публикация

1984-10-29—Подача