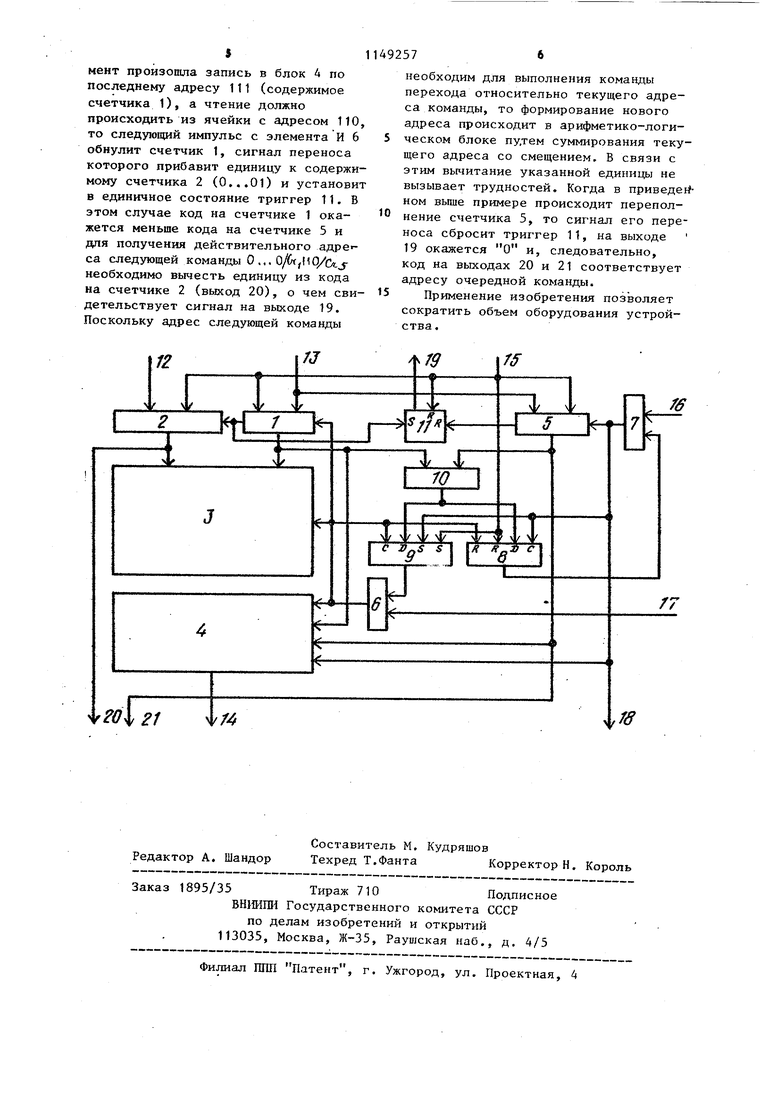

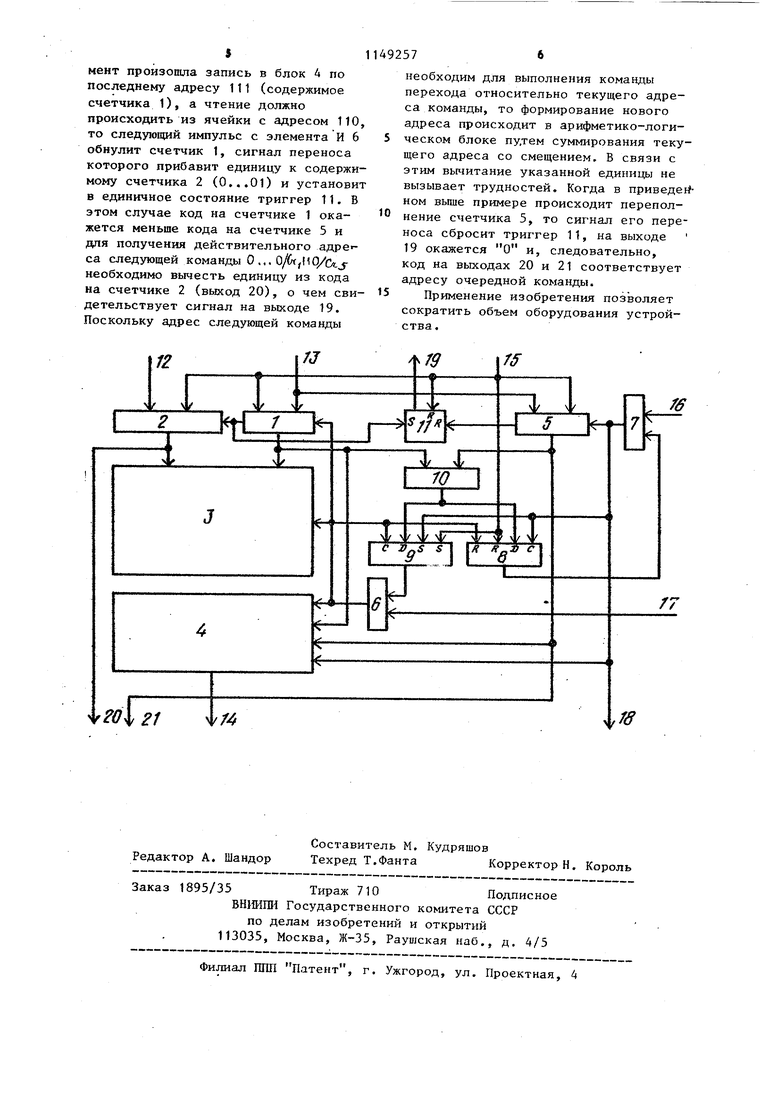

Изобретение относится к вычисли тельной технике. Известно устройство выборки команд, содержащее счетчик адреса команд, блок памяти и регистр команд Недостатком этого устройства явля ется низкое быстродействие. Наиболее близким по технической сущности к изобретению является устройство, содержащее буфер команд, блок памяти и счетчик 2 . Недостатком известного устройства является большой объем оборудования . Цель изобретения - сокращение аппаратурных затрат. Поставленная цель достигается тем что в устройство для выборки команд содержащее два блока памяти, первый и второй счетчики, информационные входы которых являются первым и вторым адресными входами устройства, выходы первого и второго счетчиков соединены с адресными входами первого блока памяти, выход переноса первого счетчика соединен со счетным входом второго счетчика, информационный вход второго блока памяти соединен с выходом первого блока памяти, выход второго блока памяти является информационным выходом устройства, введены первый, второй и третий триггеры, схема сра нения, третий счетчик и два элемента И, выходы которых соединены со счетными входами первого и третьего счетчиков соответственно и с входами чтения и записи второго блока памяти соответственно, выход второг элемента и является первым сигнальны выходом устройства, выход первого элемента И соединен с входом чтения первого блока памяти, выходы первого и третьего счетчиков соединены соответственно с адресными входами запис и чтения второго блока памяти и с первым и вторым входами схемы сравне ния, выход которой соединен с информ ционными входами первого и второго триггеров, первые входы первого и второго элементов И соединены с вьгхо дами первого и второго триггеров, вторые входы первого и второго элементов И соединены с первым и вторым тактовыми входами устройства соответ ственно, запросньй вход устройства соединен с установочными входами всех счетчиков, первый вход сброса и единичный вход третьего триггера соединены с выходами переноса первого и третьего счетчиков соответственно, выход третьего триггера является вторым сигнальным выходом устройства, выходы второго и третьего счетчиков являются первым и вторым адресными выходами устройства соответственно, тактовый вход первого триггера и первый вход сброса второго триггера соединены с выходом первого элемента И, первый единичный вход первого триггера и вторые входы сброса второго и третьего триггеров соединены с запросным входом устройства, первый адресный вход которого соединен с информационным входом третьего счетчика, второй единичный вход первого триггера и тактовый вход второго триггера соединены с выходом второго элемента И. На чертеже приведена структурная схема предлагаемого устройства. Устройство содержит счетчики 1 и 2, блоки 3 и 4 памяти, счетчик 5, элементы И 6 и 7, триггеры 8 и 9, схему 10 сравнения, триггер 11, адресные входы 12 и 13 устройства, информационный выход 14 устройства, запросный вход 15 устройства, тактовые входы 16 и 17 устройства, сигнальные выходы 18 и 19 устройства, а;.рескые выходы 20 it 2} устройства. Счетчики 1 и 2 предназначены для счета младшей и старшей части адреса очередной команды, выбираемой из блока 3 памяти и образуют единый счетчик команд. Блок 3 памяти предназначен для хранения команд. Блок 4 предназначен для промежуточного хранения команд, выбираемых из блока 3 памяти, и представляет собой быстродействующий блок памяти, имеющий раздельные входы записи и считывания. Счетчик 5 предназначен для счета адреса команды, выбираемой из блока 4. Элемент И 6 предназначен для формирования сигналов заполнения блока 4 при наличии тактовых сигналов с входа 16 и отсутствии запрета с триггера 9. Элемент И 7 предназначен для формирования сигнала считыва ния команды при наличии запроса с входа 15 и отсутствии запрета с триггера 8. Триггер 8 предназначен для вьща- ; чи сигнала Запрет считывания, если блок 4 пуст. Триггер 9 предназначен

для выдачи сигнала Запрет записи, если в блоке 4 нет свободного места. Схема 10 сравнения предназначена для вьщачи сигнала при совпадении кодов на счетчике 5 чтения и счетчике 1.

Триггер 11 предназначен для выдачи сигнала на выход 19, если адрес записи в блок 4 на счетчике 1 оказался меньше .адреса чтения на счетчике Входы 12 и 13 предназначены для занесения адреса команды в счетчики 1, 2 и 5 в начале работы и при вьшолнении команд переходов сигнал приводит к исходное состояние триггеры 8,9 и 1

Выход 14 предназначен для выдачи очередной команды,сопровождаемой синхронизирующим сигналом на выходе 18.

С входа 15 поступают сигналы запроса на очередную команду в виде последовательности импульсов, которые прекращаются после вьщачи сигнала с выхода 18. На вход 17 поступает последовательность импульсов от генератора, период которых равен циклу обращения к памяти. Будем считать, что сигналы с входов 16 и 17 сдвинуты друг относительно друга.

На выходы 20 и 21 поступает адрес команды, подлежащий выполнению, причем, если на выходе 19 имеется единичный сигнал, то код на выходе 20 должен быть уменьшен на единицу для получения действительного значения адреса.

Устройство работает следующим образом.

В блоке памяти находятся команды, подлежащие выполнению. Устройство приходит в исходное состояние при подаче на входы 12 и 13 адреса начальной команды, сопровождаемой стробирующим сигналом 15, При этом старшие разряды адреса команды записываются в счетчик 2, а мпадшие в счетчики 1 и 5. Кроме того, сигнал 15 устанавливает в единичное состояние триггер 9, в нулевое состояние триггер 8, в нулевое состояние триггер 11, сигнал с которого поступает на выход 19 и свидетельствует о том, что код на счетчике 5 не больше кода на счетчике 1. Сигналы с входа 16 не проходят через элемент И 7 и удовлетворяются, поскольку блок 4 пуст. Сигнал с входа 17 (от генератора импульсов), пройдя элемент И 6, поступит на вход чтения, прочтет команду из блока 3 п

адресу, хранимому в счетчиках команд 1 и 2 и по заднему фронту, поступив на вход записи блока 4, запишет эту команду по адресу, находящемуся в счетчике 1. Кроме того, сигнал с элемента И 6 увеличит на единицу содержимое счетчика 1 подготавливая адрес следующей команды, а также установит в единицу триггер 8, разрешая чтение из блока 4. Если после окончания очередного чтения из блока 3 памяти оказывается, что код в счетчике 1 совпадает с кодом в счетчике 5, то блок 4 полностью занят. Задний фронт сигнала элемента И 6 поступит на синхронизирующий вход триггера 9, и, поскольку выход схемы 10 в единичном состоянии, триггер 9 установится в нулевое состояние и закроет элемент И 6. Заполнение блока 4 будет прекращено.

Если блок 4 не пуст, то запрос на команду, пройдя через элемент И 7 поступит на вход чтения блока 4, подаст на выход 14 команду по адресу, хранящемуся в счетчике 5 чтения, -и поступит на выход 18 в качестве строба выдачи. Сигнал с элемента И 7 прибавит единицу к счетчику 5 и, сброс триггер 9, разрешит чтение из блока 3 памяти. Если при чтении из блока 4 произойдет совпадение кодов на счетчиках 1 и 5, то блок 4 полностью выбран. Цри этом, по заднему фронту сигнала с элемента И 7 триггер 8 переводится в нулевое положение, а элемент И 7 закрыт - чтение команд запрещено. В результате триггер 9 сбрасывается первой командой чтения из блока 4, а триггер 8 - первой командой записи в блок 4.

Рассмотрим процедуру изменения адресов в счетчиках 1, 2, и 5.

В исходном состоянии в счетчики 1 и 5 заносится один и тот же код и счетчик 5 выполняет функцию счета младшей части адреса следующей команды. Поскольку чтение из ячейки блока 4 происходит только после записи информации в нее, то адрес записи на счетчике 1 должен быть больше адреса чтения на счетчике 5. В этом случае адрес очередной команды, подлежащей выполнению, получается на выходах 20 и 21, т.е. старшие разряды поступают со счетчика 2, а младшие - со счетчика 5. Однако, пусть счетчик 5 обнулен (0...0) и в некоторый мо5мент произошла запись в блок А по последнему адресу 111 (содержимое счетчика 1), а чтение должно происходить из ячейки с адресом 110 то следующий импульс с элемента И 6 обнулит счетчик 1, сигнал переноса которого прибавит единицу к содержи мому счетчика 2 (0...01) и установи в единичное состояние триггер 11, В этом случае код на счетчике 1 окажется меньше кода на счетчике 5 и для получения действительного следующей команды О ... 0/Ct,lQ/Ctjнеобходимо вычесть единицу из кода на счетчике 2 (выход 20), о чем свидетельствует сигнал на выходе 19. Поскольку адрес следующей команды 57 необходим дЛя выполнения команды перехода относительно текущего адреса команды, то формирование нового адреса происходит в арифметико-логическом блоке пу.тем суммирования текущего адреса со смещением, В связи с этим вычитание указанной единицы не вызывает трудностей. Когда в приведенном выше примере происходит переполнение счетчика 5, то сигнал его переноса сбросит триггер 11, на выходе 19 окажется О и, следовательно, код на выходах 20 и 21 соответствует адресу очередной команды. Применение изобретения позволяет сократить объем оборудования устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выборки команд | 1984 |

|

SU1221652A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| Устройство для отладки программ | 1986 |

|

SU1383372A1 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1016782A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

УСТРОЙСТВО ДЛЯ ВЫБОРКИ ,КОМАНД, содержащее два блока памяти, первый и второй счетчики, информационные входы которых являются первым и вторым адресными входами устройства, выходы первого и второго счетчиков соединены с адресными входами первого блока памяти, выход переноса первого счетчика соединен со счетным входом второго счетчика, информационный вход второго блока памяти соединен с выходом первого блока памяти, выход второго блока памяти является информационным выходом устройства, отличающеес я тем, что, с целью сокращения аппаратурных затрат, оно содержит первый, второй и третий триггеры, схему сравнения, третий счетчик и два элемента И, выходы которых соединены со счетными входами первого и третьего счетчиков соответственно и с входами чтения и записи второго блока памяти соответственно, выход второго элемента И является и первым сигнальным выходом устройства, выход первого элемента И соединен с входом чтения первого блока памяти, выходы первого и третьего счетчиков соединены соответственно с адресными входами записи и чтения второго блока памяти и с первым и вторым входами схемы сравнения, выход которой соединен с информационными входами первого и второго триггеров, первые входы первого и второго элементов И соединены с выходами первого и второго триггеров, вторые входы первого и второго элементов И соединены с первым и вторым тактовыми входами устройства соответственно, запасный вход устройства соединен с установочными входами (Л всех счетчиков, первый вход сброса и единичньй вход третьего триггера соединены с выходами переноса первого и третьего счетчиков соответственно, выход третьего триггера является вторым сигнальным выходом устройства, выходы второго и третьего счетчиков являются первьм и вторым адресными выходами устройства соответственно, тактовый вход первого триггера и первый вход сброса второго триггера соединены с выходом первого элемента И, первый единичный вход первого триггера и вторые входы сброса второго и третьего триггеров соединены с запрос ным входом устройства, первый адресный вход которого соединен с информационным входом третьего счетчика, второй единичный вход первого триггера и тактовый вход второго триггера соединены с выходом второго элемента И.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Горелик А.Л | |||

| и др | |||

| Бортовые цифровые вычислительные машины | |||

| М., Машиностроение, 1975, с | |||

| Способ получения нерастворимых лаков основных красителей в субстанции и на волокнах | 1923 |

|

SU132A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Королев Л.Н | |||

| Структуры ЭВМ и их математическое обеспечение | |||

| М., Наука, 1978, с | |||

| Шкив для канатной передачи | 1920 |

|

SU109A1 |

Авторы

Даты

1985-04-07—Публикация

1984-01-27—Подача