&0 Од

эо

CD

S

Изобретение относится к вычислительной -технике и может быть использовано в тех случаях, когда блоки памяти заминающего устройства на цилиндрических маггнитных доменах (ЦМД) имеют последовательно-параллельную накопительную структуру и содержат некоторое количество дефектных накопительных регистров.

Целью изобретения является повышение надежности устройства путем самодиагностики отказов.

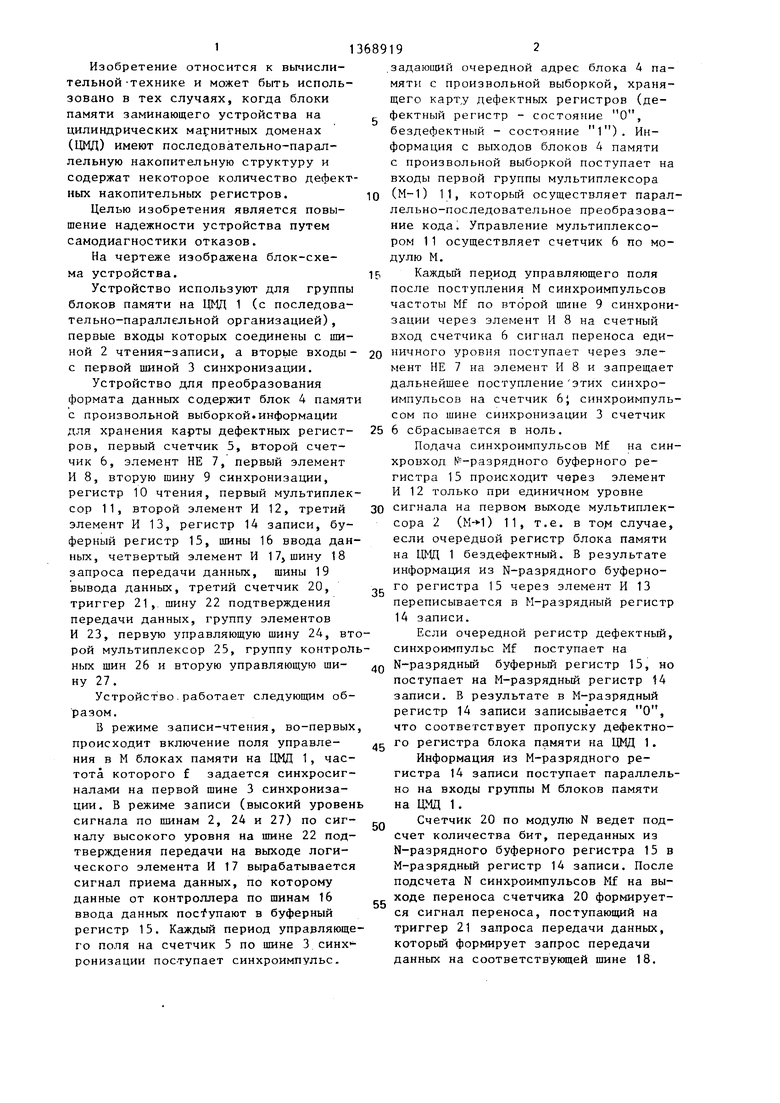

На чертеже изображена блок-схема устройства.

Устройство используют для группы блоков памяти на ЦМД 1 (с последовательно-параллельной организацией), первые входы которых соединены с шиной 2 чтения-записи, а вторые входы- с первой шиной 3 синхронизации.

Устройство для преобразования формата данных содержит блок 4 памят с произвольной выборкой.информации для хранения карты дефектных регистров, первый счетчик 5, второй счетчик 6, элемент НЕ 7, первый элемент И 8, вторую шину 9 синхронизации, регистр 10 чтения, первый мультиплексор 11, второй элемент И 12, третий элемент И 13, регистр 14 записи, буферный регистр 15, шины 16 ввода данных, четвертый элемент И 17jшину 18 запроса передачи данных, шины 19 вывода данных, третий счетчик 20, триггер 21, шину 22 подтверждения передачи данных, группу элементов И 23, первую управляющую шину 24, втрой мультиплексор 25, группу контролных шин 26 и вторую управляющую шину 27.

Устройство,работает следующим образом.

В режиме записи-чтения, во-первых происходит включение поля управления в М блоках памяти на ЦМД 1, частота которого f задается синхросигналами на первой шине 3 синхронизации. В режиме записи (высокий уровен сигнала по шинам 2, 24 и 27) по сигналу высокого уровня на шине 22 подтверждения передачи на выходе логического элемента И 17 вырабатывается сигнал приема данных, по которому данные от контроллера по шинам 16 ввода данных поступают в буферный регистр 15. Каждьй период управляющего поля на счетчик 5 по шине 3 синх- ронизации поступает синхроимпульс.

5

0

задающий очередной адрес блока 4 памяти с произвольной выборкой, хранящего карту дефектных регистров (де- фектный регистр - состояние О, бездефектный - состояние 1). Информация с выходов блоков 4 памяти с произвольной выборкой поступает на входы первой группы мультиплексора (М-1) 11, который осуществляет параллельно-последовательное преобразование кода. Управление мультиплексором 11 осуществляет счетчик 6 по модулю М.

Каждый период управляющего поля после поступления М синхроимпульсов частоты Mf по второй шине 9 синхронизации через элемент И 8 на счетный вход счетчика 6 сигнал переноса единичного уровня поступает через элемент НЕ 7 на элемент И 8 и запрещает дальнейшее поступление этих синхроимпульсов на счетчик 6j синхроимпульсом по шине синхронизации 3 счетчик 5 6 сбрасывается в ноль.

Подача синхроимпульсов Mf на син- хровход -разрядного буферного регистра 15 происходит через элемент И 12 только при единичном уровне сигнала на первом выходе мультиплексора 2 () 11, т.е. в то; случае, если очередной регистр блока памяти на ЦМД 1 бездефектный. В результате информация из N-разрядного буферного регистра 15 через элемент И 13 переписывается в М-разрядный регистр 14 записи.

Если очередной регистр дефектный, синхроимпульс Mf поступает на 0 N-разрядный буферный регистр 15, но поступает на М-разрядный регистр 14 записи. В результате в М-разрядный регистр 14 записи записыв ается О, что соответствует пропуску дефектно- 5 го регистра блока памяти на ЦМД 1. Информация из М-разрядного регистра 14 записи поступает параллельно на входы группы М блоков памяти на ЩЩ 1.

Счетчик 20 по модулю N ведет подсчет количества бит, переданных из N-разрядного буферного регистра 15 в М-разрядный регистр 14 записи. После подсчета N синхроимпульсов Mf на выходе переноса счетчика 20 формируется сигнал переноса, поступающий на триггер 21 запроса передачи данных, которьй формирует запрос передачи данных на соответствующей шине 18.

0

5

0

55

Из контроллера по шинам 16 ввода данных поступает очередное N-разряд ное информационное слово, которое зписывается в М-разрядный буферньш ргистр 15 по высокому уровню сигнала на шине 22 подтверждения передачи данных; при этом триггер 21 запроса передачи данных сбрасывается в ноль

В режиме чтения (низкий уровень сигнала на шинах 2 и 24, высокий уровень по шине 27) каждый период управляющего поля информация с выходов группы из М блоков памяти на ЦМД 1 поступает на М-разрядный регистр 10 чтения. С выхода М-разрядно го регистра 10 чтения информация поступает на входы второй группы мультиплексора () 11, который осуществляет ее параллельно-последовательное преобразование. С второго выхода мультиплексора 2 () 11 информация поступает на второй из входов первой группы мультиплексора 25 и с его выхода - на последовательный вход N-разрядного буферного регистра 15.

В N-разрядном буферном регистре 15 происходит прием данных только от бездефектных регистров блоков памяти на ЦМД 1, так как поступление синхроимпульсов .Mf на синхровход этого регистра происходит только при единичном уровне сигнала на первом

выходе мультиплексора () 11, С выходов N-разрядного буферного регистра 15, после формирования N-разрядного информационного слова по сигналу передачи данных от триггера 21 запроса передачи данных, информация поступает на шины 19 вывода данных. Прием информационного слова подтверждается сигналом подтверждения передачи по шине 22.

В первом режиме теста (низкий уровень сигнала на шинах 2, 24 и 27) на первый вход первой группы входов мультиплексора 25 подается карта дефектов с первого выхода мультиплексора () 11. Информация с выхода

Мультиплексора 25 принимается в буферный регистр 15, Так как поступление синхроимпульсов на синхровход этого регистра происходит только при единичном уровне сигнала на первом выходе мультиплексора (М-)) 11, в буферном регистре 15 формируется код FFf,j,, передаваемый по сигналу от триггера 21 запроса передачи данных

на шины 19 вывода данных. Отличие переданного кода от FF,.,.свидетельствует о неисправности устройства.

Во втором режиме теста (низкий уровень сигнала на шинах 2 и 27 и высокий - на шине 24, код XX.-. .X на контрольных шинах 26) блок памяти с произвольной выборкой 4 отключается и на первом выходе мультиплексора устанавливается высокий уровень. Сигналы с выходов счетчика 6 через группу элементов И 23 поступает на входы второй группы (адресные)-- мультиплексора 25. На выходе мультиплексора 25 формируется код ХХ.,.Х1, записываемый в буферный регистр 15. Отличие переданного на шины 19 вывода данных кода от XX..Х1

свидетельствует о неисправности устройства . , . Формула изобретения

5

0

5

0

5

О

5

Устройство для преобразования формата данных в доменной памяти, содержащее блок памяти с произвольной выборкой информации, счетчики, счетный вход первого из которых является первым входом синхронизации устройства, а информационные выходы соединены с соответствующими адресными входами блока памяти с произвольной выборкой информации, элемент НЕ, вход которого соединен с выходом переполнения второго счетчика, элементы И, первый вход первого из которых соединен с выходом элемента НЕ, второй вход является вторым входом синхронизации устройства, а выход соединен со счетным входом второго счетчика и первым входом второго элемента И, регистр записи, информационный вход которого соединен с выходом третьего элемента И, вход синхрониза11Ии - с выходом первого элемента И, а выходы являются информационными выходами первой группы устройства, регистр чтения, входы которого являются входами данных первой группы устройства, буферный регистр, информационные входы параллельного приема которого являются входами данных второй группы устройства, синхровход, вход приема данных и вход запроса передачи данных буферного регистра соединены соответственно с выходом второго элемента И, выходом четвертого элемента И и с выходом триггера, выходы буферного регистра являются информационными выходами второй группы устройства, причем выход младшего разряда буферного регистра соединен с первым входом третьего элемента И, первы мультиплексор, входы первой группы которого соединены с соответствующими выходами регистра чтения, входы второй группы - с соответствуюсцими выходами блока памяти с произвольной выборкой информации, входы третьей группы - с соответствующими выходами второго счетчика, первый выход первого мультиплексора соединен с вторым входом второго элемента И и вторым входом третьего элемента И, счетный вход третьего счетчика соединен с выходом второго элемент И,первый и второй входы четвертого элемента И являются первым и вторым управляющими входами устройства, триггер, установочный вход которого соединен с выходом переполнения третьего счетчика, вход сброса триггера соединен с вторым входом четвертого элемента И, установочный вход второго счетчика соеди1

68919 нен

со счетным входом первого счетчика, отличающееся тем, что, с целью повышения надежности устройства путем самодиагностики отказов, оно содержит второй мультиплексор и группу элементов И, первые входы группы элементов И подключены к выходам второго счетчика, вторые

10 входы являются управляющими входами устройства и подключены к управляющему входу блока памяти с произвольной выборкой информации, первый и второй информационные входы второго

g мультиплексора подключены соответственно к первому и второму выходам первого мультиплексора, а остальные информационные входы второго мультиплексора являются входами константы

2Q устройства, первый адресный вход второго мультиплексора является управляющим входом устройства, а остальные адресные входы второго мультиплексора подключены к выходам элементов И

25 группы, а выход второго мультиплексора соединен с входом последовательного приема буферного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования формата данных в доменной памяти | 1985 |

|

SU1327183A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1462336A1 |

| Устройство для обнаружения и исправления ошибок в доменной памяти | 1985 |

|

SU1275540A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1991 |

|

SU1837303A1 |

| Буферное устройство для передачи данных | 1987 |

|

SU1418725A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| Патент № 4139886, опублик | |||

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Устройство для преобразования формата данных в доменной памяти | 1985 |

|

SU1327183A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-01-23—Публикация

1985-10-21—Подача