Изобретение относится к вычислител&ной технике, в частности к средствам автоматического контроля цифровых объектов, и может быть использовано для высокочастотной функциональной проверки блоков ЭВМ, построенных на основе микропроцессоров и других схем большой степени интеграции, целых микро- ЭВМ и прочих сложных устройств в процессе их производства.

Известны устройства контроля, обеспечивающие проверку цифровых объектов на .высоких частотах и содержащие блок управления, генератор псевдослучайных последовательностей выход которого связан через входной буферный блок с входами проверяемого и эталонного объектов, и блок сравнения, входы которого через выходной буферный блок соединены с выходами обоих объектов 1 .

Однако известное устройство не допускает использования произвольных тестов, -которые являются индивидуальными для каждого объекта и служат для установки его в изв стное начальное состояние, а также для обеспечения в сочетании с псевдослучайными тестами более эффективной проверки. Это делает устройство по существу, непригодным для контроля объектов высокой функциональной- сложности, таких как микропроцессорные блоки.

Известно устройство, содержащее блок управления, блок памяти программ и произвольных тестов, а также генератор псевдослучайных тестов Выходы указанных блоков через буферный блок связаны с входами проверяемого и эталонного объектов, выходы обоих объектов подключены к блоку сравнения, выход которого связан с блоком управления .2 .

Недостатком указанного устройства является невозможность совмещения в одном и том же такте проверки наборов псевдослучайного и хранимого тестов, что часто необходимо при контроле микропроцессорных блоков, когда, например, на входы управления блока задается определенная последовательность команд, а на входы данных одновременно - последовательность случайных операндов.

Известно также устройство, содержащее выходной регистр и регистр маски, генератор псевдослучайных последовательностей, блок памяти, связанный с его входами преобразующий регистр, входы которого соединены с выходами блока памяти и генератора, а выходы блока памяти подключены ко входам выходного регистра и регистра маски З .

Основные недостатки данного устройства - относительно невысокое

быстродействие и неприспособленность для асинхронного обмена данными с проверяемым объектом.

Наиболее близким по технической сущности к изобретению является 5 устройство, содержащее блок выходных регистров и блок сравнения, связанные с выводами проверяемого и эталонного рбъектов, блок мультиплексорозв со своим контролером, генератор псевдослучайных тестов, блок памяти

произвольных тестов, блоки управления, ввода и вывода. Выходы генератора псевдослучайных тестов и блока памяти тестов связаны со входами

5 блока мультиплексоров, выхсды которого соединены со входами блока регистров . Входы блока памяти тестов, блока управления и контроллера, блока мультиплексоров связаны с выQ ходами блока ввода, другие входел блока управления - с выходами блока сравнения, а выходы блока управления - с управляющими входами всех остальных блоков 4J .

Основным недостатком этого устройства является значительное снижение быстродействия (частоты про-верки) в тех случаях, когда проверяемый объект имеет сложный алгоритм обмена данными,с внешней средой.

0 Так, для организации асинхронного обмена с проверяемым объектом, кроме самих тестов, требуются дополнительные управляющие данные {маски для выделения управляющих выходов

5 .объектов, формирующих запросы на данными; эталонные значения . запросов, данные для переключения каналов устройства, связанных с двунаправленными выводами объекта, на

0 прием или выдачу} данные для форми. рования ответов о выполнении запросов .) которые должны храниться в блоке памяти тестов. Поэтому для передачи одного набора теста на

f. входы объекта требуется несколько {до трех или более) дополнительных обращений к этому блоку за управляющими данными, что снижает частоту проверки в 2-4 раза.

Цель изобретения - повышение быст0 -родействия устройства.

Поставленная цель достигается тем, что в устройство контроля микропроцессорных блоков, содержащее блок регистров, блок сравнения, блок мультиплексоров, генератор псевдослучайных тестов, блok памяти тестов, блок управления, блок ввода, блок вывода, причем перва и вторая группы информационных выходов блока

0 регистров подключены соответственно к входам эталонного и проверяемого микропроцессорных блоков и к первой и второй группам информационных входов блока сравнения, группа управляющих входов которого связана с группой управляющих выходов блока регист ров, группа управляющих входов блока регистров соединена с группой управляющих входов блока мультиплексоров, группой входов генератора псевдослучайных тестов и первой группой управляющих выходов блока управления, вторая группа управляющих выходов которого связана с группой управляющих входов блока памяти тестов, группа информационных входов которого подключена к первой группе информационных входов блока регистров и к группе входов блока вывода, группа управляющих выходов блока памяти тестов соединена с группой управляющих входов блока управления, группа информационных входов которого подключена к группе выходов блока ввода, первая, вторая, третья и четвертая группы информационных входов блока мультиплексоров связаны соответственно с Группой выходов генератора псевдослучайных тестов, группой выходов блока ввода, группой информационных выходов блока памяти тестов и группой выходов блока сравнения, введены блок сверхоперативной памяти и блок обработки информации, причем группы управляющих входов- блока сверхоперативной памяти и блока обработки информации соединены с первой группой управляющих выходов блока управления, группа информационных входов блока сверхоперативной Пс1мяти подключена к первой группе информационных входов блока регистров, вторая группа информационных входов которого связана с группой выходов блока сверхоперативной памяти и первой группой информационных входов блока обработки инIформации, вторая группа информационных входов которого соединена с группой выходов блока мультиплексоров .

Кроме того, блок обработки информации содержит в каждом i-м разряде ЗК -триггер и элемент ИЛИ, причем входы установки, сброса, синхронизации и первые J и К-входы триггера связаны с первым входом элемента ИЛИ и подключены к первой группе входов блока, вторые Л - и К -входы триггера соединены с -м входом второй группы входов блока, третьи J и К -входы триггера связаны с выходом элемента или, второй вход которого подключен к -му входу третьей группы входов блока, выход Л К -триггера является i -м выходом блока.

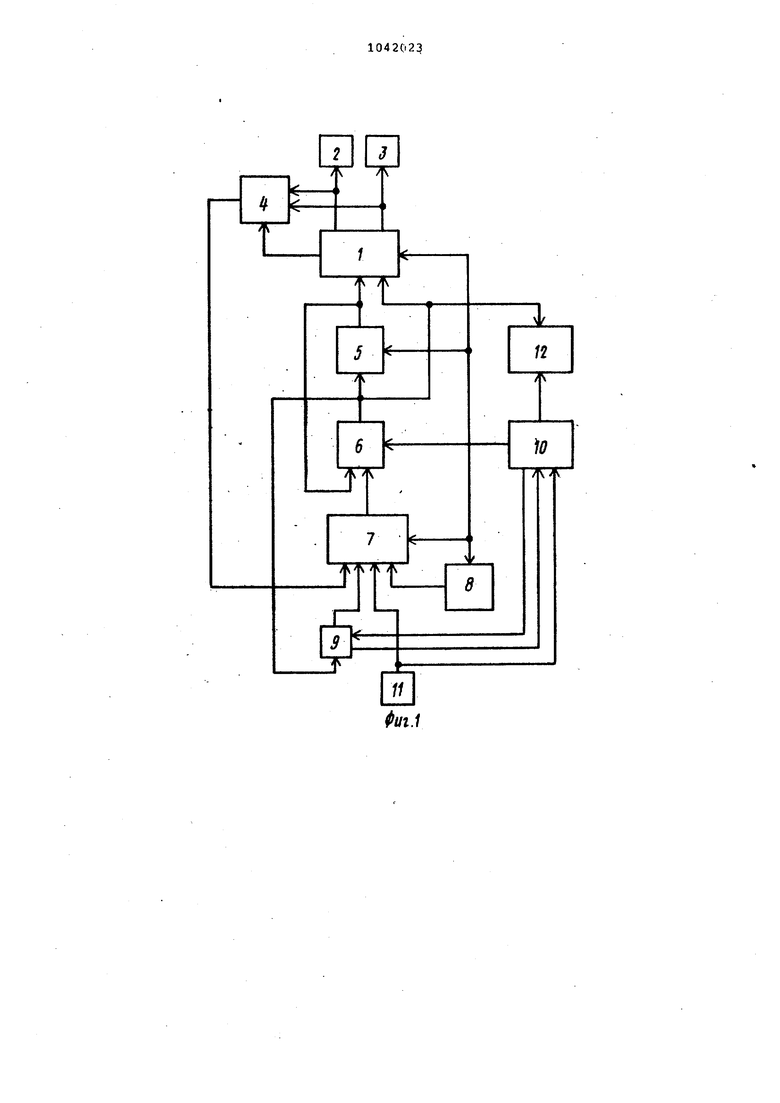

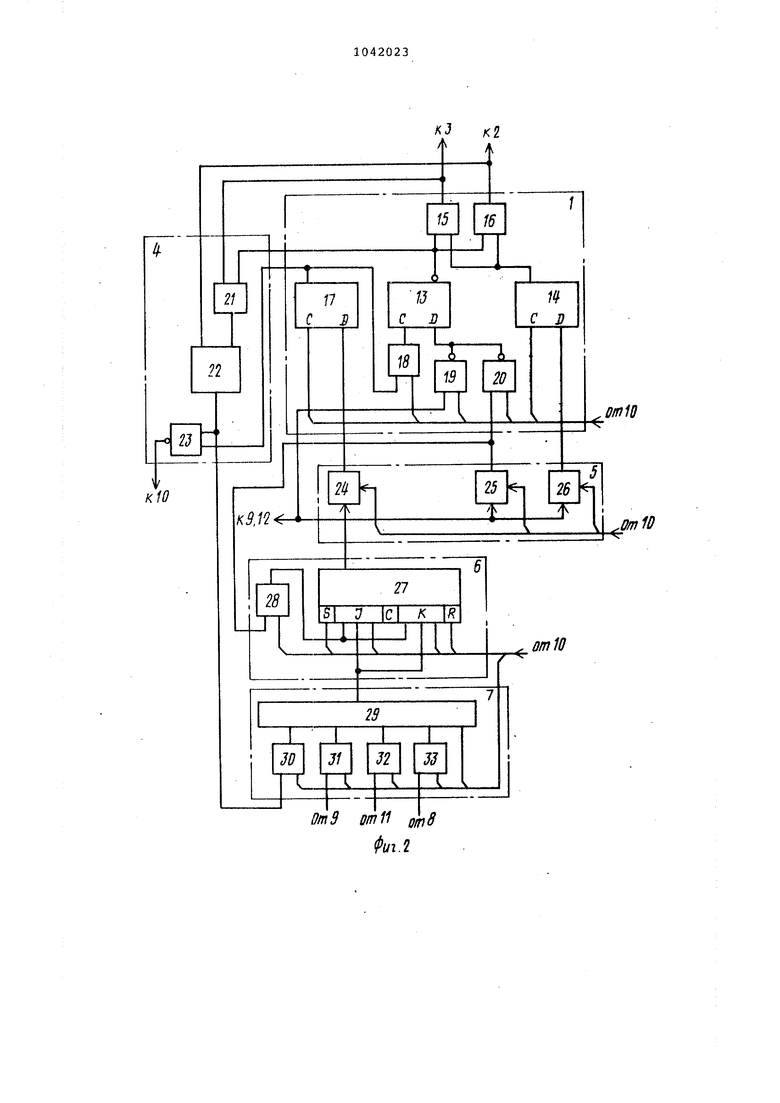

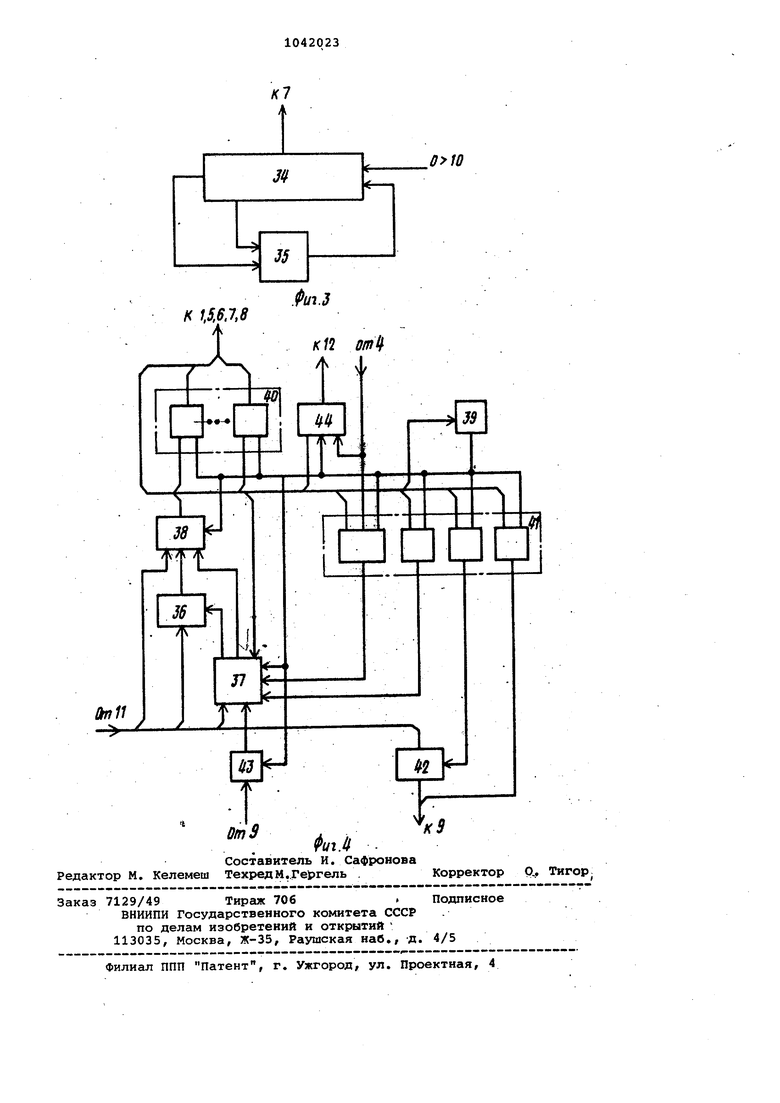

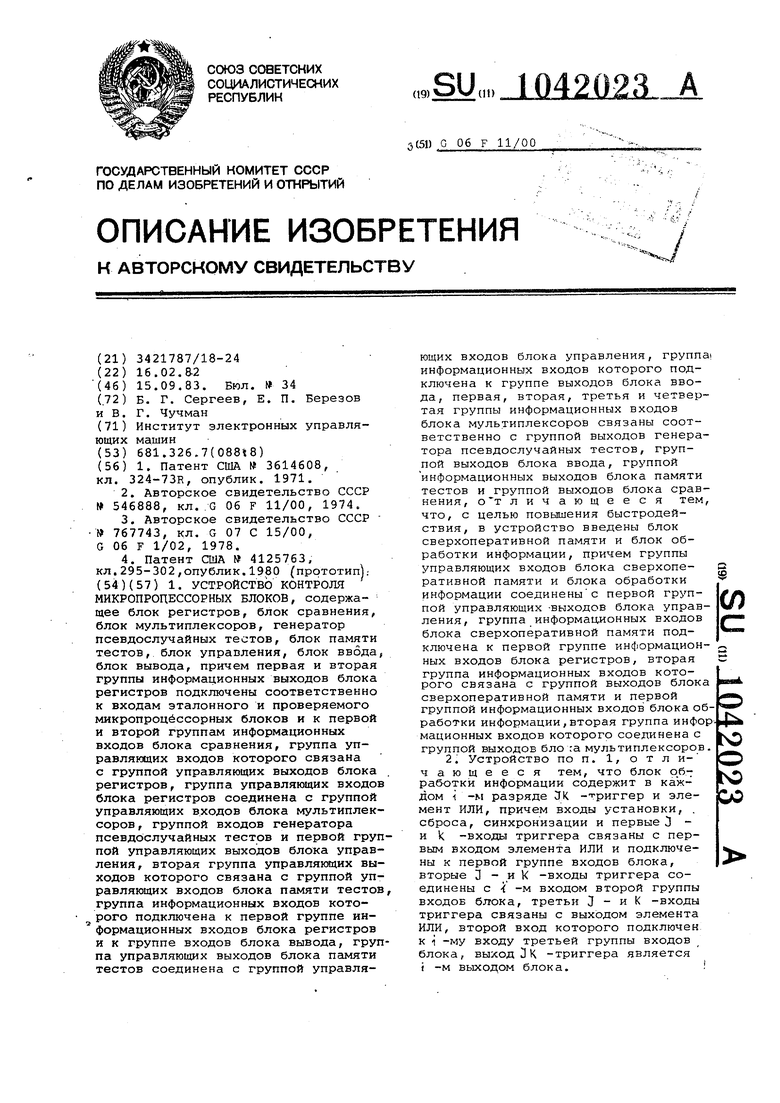

На фиг. 1 представлена структурная схема предлагаемого устройства./ на фиг. 2 - принципиальные схемы разряда блока регистров, блока срав нения, блока сверхоперативной памяти, блока обработки информации и блока мультиплексоров на фиг. 3

схема генератора псевдослучайных тестов; на фиг. 4 - схема блока управления.

В состав устройства входят: блок 1 регистров, эталонный и проверяемый 5 объекты 2 и 3, блок 4 сравнения,

блок 5 сверхоперативной памяти, блок 6 обработки информации, блок 7 мультиплексоров, генератор 8 псевдослучайных тестов, блок 9 памяти тестов,

10 блок 10 управления, блок 11 ввода, блок 12 вывода.

Каждый из блоков 1, 4, 5, б, 7 состоит из N идентичных схем (разрядов ), каждая из которых соответстАг вует одному выводу проверяемого и эталонного объектов. Величина N определяется числом выводов у объектов, для большинства микропроцессорных блоков достаточно N 256.

Схема любого { -го разряда блока

0 1 регистров содержит триггер 13 данных и триггер 14 коммутации связанные с элементами И 15 и 16, триггер 17 маски, элемент И 18 и два элемента И-НЕ 19 и 20.

5 Триггер 13 данных служит для хранения значения сигнала, подаваемого в текущем такте проверки на вход объекта, или эталонного значения выходного сигнала объекта.

0 Триггер 14 коммутации определяет функцию канала в текущем такте: подача сигнала на вход объекта или опрос его выходного сигнала. В последнем случае он переводит элементы И 15 и 16 в высокоимпедансное состояние выхода. Триггер 17 маски вместе с элементом И 18 разрешает или запрещает прием информации в триггер 13 данных, а также позволя- ет исключить из проверки соответствующий вывод объекта при сравнении реакций. Элементы И-НЕ 19 и 20 служат для выбора источника данных при установке триггера 13.

В i -и разряд блока 4 сравнения 5 входят последовательно соединенные элемент И 21, сумматор 22 по модулю два,и элемент И-ЯЕ 23.

Элемент И 21 cлvжит для выбора

П способа проверки состояния i -го вывода проверяемого объекта (сравнение с состоянием .вывода эталонноfo объекта или с состоянием триггера 13 данных). Сама проверка состо.-. яния осуществляется сумматором 22.

Элемент И-НЕ 23 обеспечивает передачу в -блок 10 управления результата сравнения или его блокировку в -зависимости от состояния триггера 17 маски.

0 В состав 1 -го разряда блока 5 сверхоперативной памяти входят три .одноразрядных ЗУ 24-26 с независимым управлением.

ЗУ 24 служит для хранения масок

5 сравнения и масок приема в триггеры 13 данных , 39 25 - для хранения сигналов синхронизации объектов, эталонных значений управляющих выходных сигналов объектов, данных, .определяющих тип теста для каж;5ого входа объекта и др,, ЗУ 26 - для хранения данных, обеспечивающих опе ративное переключение каналов связи С объектами на прием или выдачу сиг налов. Объем каждого из ЗУ 24, 25 н 26 составляет 128-256 бит.. Любой 1 -и разряд блока 6 обработки информации в простейшем случае содержит О К-триггер 27, совмеща ющий функции одноразрядного регистра-накопителя и схемы логического преобразования данны с, и элемент ИЛИ 28, с помощью которого в некоторых операциях обеспечивается отключение выхода ЗУ 25 от входов триггера 27. В каждый -и разряд блока 7 мультиплексоров входит элемент ИЛИ и связанные с ним четыре элемента И 30-33, с помощью которых производится выбор источника данных для блока 6 обработки информации. Генератор 8 псевдослучайных тестов служит для формирования последо вательностей N-разрядных псевдослучайных чисел. Он реализуется на сдв говых регистрах с обратными связями В зависимости от величины N в сост.ав генератора может входить один или несколько регистров. На фиг. 3 показан вариант генератора,,в котором используется сдвиговый регистр 34 и один сумматор 35 по модулю два Блок 9 памяти тестов предназначен для Хранения тестов, задаваемых всеми наборами, эталонных реакций (если при проверке отсутствует эталонный объект) и, при необходимости, фактических реакций объекта, которые записываются в него в процессе проверки и затем анализируются для диагностики неисправности Блок 9 представляет собой ЗУ с про извольным доступом, имеющее объем 4-8 тысяч N -г К )-разрядных слов, где К - число дополнительных разря дов в слове, необходимых для обеспе чения работы блока 10 управления. Блок 10 управления содержит память 36 команд и связанные с ней счетчик 37 и регистр 38 команд, так товый генератор 39, первую группу элементов И 40, обеспечивающую формирование управляющих сигналов, которые через первую группу выходов блока 10 поступают во все блоки ус ройства, вторую группу элементов И 41, формирующую управляющие сигналы для внутренних узлов блока, счетчи 42 гщресов блока 9 памяти тестов, регистр 43 управления, предназначе ный для запоминания управляющих ра рядов читаемого из блока 9 слова, регистр 44 состояния, который фиксирует результат проверки реакций объекта, получаемый от блока 4 сравнения, и другие особые ситуации, требующие останова процесса проверки. Блок 11 ввода служит для загрузки тестов в блок 9 памяти, управляющих данных в блок 5 сверхоперативной памяти и команд в память. 36 блока 1-0 управления. В простейшем случае блок 11 содержит переключатели и кнопки, с помощью которых обеспечивается ручной выбор приемника данных, набор . данных и их ввод, В более сложных вариантах построения этот блок может содержать устройства ввода информации с машинных носителей и устройства внешней памяти типа магнитных дисков и т.п. . Блок 12 вывода в наиболее простом исполнении имеет лишь средства индикации регистра 44 состояния и триггеров 27 блока 6 обработки информации. В более сложных случаях в него могут входить устройства вывода на экран, на машинные носители информации, а также средства сопряжения с ЭВМ. Устройство работает следующим образом. Перед началом проверки с помощью блока 3.1 ввода производится загрузка тестов и других данных. Приемник данных определяется управляющей информацией, засылаемой из блока II в регистр 38 команды. Хранимые тесты загружаются в блок 9 памяти через блок 7 мультиплексоров и блок 6 об51аботки инфор-. мации. При этом адреса ячеек блока 9 принимаются от блока 11 в счетчик 42 адресов. Последовательности сигналов синхронизации , маски и другие управляющие данные поступают от-блока 11 в блок 5 сверхоперативной памяти (также через блоки 6 и 7), причем адреса ячеек блока 5 задаются непосредственно из регистра 38 команды. Программа, определяющая последовательность операций устройства в каждом такте проверки объекта, загружается из блока 11 в память 36 коланд с использованием для задания адресов счетчика 37 команд, После завершения ввода начинается сам процесс высокочастотной проверки. Для этого S регистр 38 вводится команда пуска, которая засылает в счетчик 37 команд адрес начала программы в памяти 36, приводит в исходное состояние генератор 8 Фестон, сбрасывает счетчик 42 адресов блока 9 памяти тестов и включает тактовый генератор 39, При синхронной организации обмена с проверяемым объектом работа

устройства в каждом такте t высокочастотной проверки сводится к следующей последовательности шагов, задаваемых командами программы, хранимой в памяти 36 блока 10 управления. Для определенности далее 5 считывается, что последовательность синхронизации объекта состоит из двух наборов.

Шаг 1. При этом происходит: чтение данных из блока 5 сверхоператив- Ю ной памяти; объединение очередного тестового набора X, получаемого из блока 9 памяти, с псевдослучайным набором от генератора 8, введенным в триггеры 27 блока б обработки в 15 такте t-1, осуществляемое огтерацией XAK;,VR- R /где К констан-. та из 34 25 блока 5, определяющая входы йроверяемого и эталонного объектов, на которые должны прикла- дываться соответствующие разряды набора X (в этих разрядах К содержатся единицы)., R - состояние триггеров 27 блока б, передача маски входов синхронизации объектов из ЗУ с 24 блока 3 в триггеры 17 блока 1 регистров, передача R в незамаскированные триггеры 13 данных блока 1, передача из ЗУ 26 блока 5 в триггеры 14 коммутации блока 1 данных для включения каналов блока 1, связанных с двунаправленными выводами объектов, на выдачу состояния триггеров 13 на объекты.

Шаг 2, Происходит: чтение данных из блока 5 сверхоперативной памяти, 35 передача маски информационных входов объектов из зу 24 блока 5 в триггеры 17 блока 1, передача первого набора синхронизации из ЗУ 25 блока 5 в незамаскирован|1ые тригге- 40 ры 13 данных блока 1 и соответствен-. но на входы объектов} сдвиг в регистре 34 генератора 8 тестов для получения очередного псевдослучайного тестового набора для такта t + 1, подготовка следующего адреса в счетчике 42 и запуск чтения тестового набора из блока 9 памяти для такта t + 1.

Шаг 3. Осуществляется чтение данных из блока 5 сверхоперативной паяти, передача второго набора синронизации из за 25 блока 5 в неамаскированные триггеры 13 данных лока 1 и соответственно на входы бъектов, передача из ЗУ 26 блока 5 55 в триггеры 14 блока 1 данных для включения каналов блока 1, связанных с двунаправленными выводами объек- тов на прием их реакции.

Шаг 4. Осуществляется также чтениебО анных из блока 5 сверхоперативной амяти; прием в блок б обработки севдослучайного набора для такта t + 1 от генератора 8 тестов и выполнение операции У AKi - R , где j

К2 - константа из ЗУ 2, определяющая входы объектов, на которые долны подаваться соответствующие разряды набора У (в этих разрядах К содержатся единицы-) J передача из 3 У 24 блока 5 маски сравнения в триггеры 17 блока 1, сравнение состояния незамаскированных выходов проверяемго и эталонного объектов в блоке 4 (при равенстве - переход к шагу 1, при неравенстве сигналов хотя бы одной пары выходов - установка разряда ошибки регистра состояния 44 и останов).

Каждый из указанных шагов задает ся соответствующей ему одной командой программы внутритактного управления, читаемой блоком 10 из памяти 36. Прочитанная команда принимается в регистр 38, а в счетчике 37 одновременно формируется адрес следующей команды, т.е. выполнение текущей команды совмещается по времени с чтением следующей.

Каждая команда содержит адресное поле, в котором размещаются адреса 3Vj 24, 25 и 26 блока 5 сверхоперативной памяти, поле кода операции блока 6 обработки, поле управления блоком 7 мультиплексоров и управляющие разряды, с помощью которых задается выдача стробирующих сигналов в блоки 5 и 6, в блок 1 регистров и генератор 8 псевдослучайных тестов. Эти сигналы вырабатываются первой группой элементов И 40 под действием импульсов тактового генератора 39 . Сигналы управления счетчиком 37 команд, счетчиком 42 адресов регистром 43 управления и блоком 9 ;памятй тестов формируются аналогичным образом второй группой элемен тов И 41.

В регистр 43 управления записываются управляющие разряды слов, читаемых из бпока 9. При соответствующем признаке в команде, находящейся в регистре 38, содержимое регистра 43 передается в счетчик 37 команд. Таким образом, при выборке теста из блока 9 можно передавать управление разным программам,.хра-. нимым в памяти 36, что позволяет изменять последовательность и состав операций устройства на разных этапах проверки объекта. Последовательность команд в пределах одной программы может изменяться с помощью команд условных переходов по результату сравнения, полученному от блока 4, что необходимо, например, при асинхронной ораганизации обмена с проверяемым объектом,когда в каждом такте Проверки добавляются шаги, связанные с анализом состояния управляющих выходов объекта. При выполнении команд условных и безусловных переходов новое состояние счетчика 37 формируется не увеличением его предыдущего состояния на единицу, а путем передачи в него адреса из регистра 38.

Дополнительные шаги и соответственно команды в программе вводятся и тогда, когда требуется модифицировать тестовый набор в блоке 6 об работки информации перед передачей его на входы объекта, при записи реакций объекта в блок 9 памяти тестов и в некоторых других случаях. При описанном ранее построении блок 6 обработки информации позволяет выполнять следующие операции

об А р (t А /г - R

(0() (o:Af) (od А fi)®R ,

где d, - операнд блока 5 сверхоперативной памяти или вектор из всех единиц, 3 - операнд из блока 9 памяти тестов, от генератора 8, от блока 4 сравнения или вектор из всех единиц.

Состояние R триггеров 27 блока 6 обработки информации может быть записано в блок памяти тестов или в блок сверхоперативной памяти и использоваться в качестве операндов оС и PI в последующих операциях..

При показанном на фиг. 2 построении блока 1 регистров и блока 4 сравнения можно изменять вид данных получаемых от блока 4, в зависимости от состояния тех триггеров 13 блка 1, которые соответствуют выходам проверяемого объекта.

Если в эти триггеры записаны эталонные значения выходных сигналов, то блок 4 выдает вектор ошибок, в

котором единицы соответствуют выходам объекта, на которых обнаружена ошибка, если в триггеры 13 записана константа Нуль, то на выходы блока 4 передается фактическое состояние выходов объектов, если константа Единица, то инверсия этого состояния.

Главным технико-экономическим преимуществом предлагаемого устройства по сравнению с прототипом является более высокое быстродействие и соответственно более высокая частота проверки объектов, достигаемая

введением блока сверхоперативной

памяти и блока обработки информации, которые обеспечивают совмещение во времени выборки и генерирования тестов с операциями управления каналами связи с объектом.

Приведенная типовая программа (Проверки синхронного объекта состоит для предлагаемого устройства из четырех шагов (команд). Аналогичная программа для устройства-прототипа

0 содержит шесть шагов, каждый из которых включает одно обращение к блоку памяти тестов. Таким образом, при одинаковых скоростях элементов обоих устройств быстродействие предлагаемого устройства оказывается в 1,5 раза выше, чем прототипа.

Dm 9 Ofnil gffjS Фиг.2

К12 0/nif

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство микропрограммного управления | 1981 |

|

SU1003086A1 |

| Генератор испытательных последовательностей | 1987 |

|

SU1543396A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

1. УСТРОЙСТВО КОНТРОЛЯ МИКРОПРОЦЕССОРНЫХ БЛОКОВ, содержащее блок регистров, блок сравнения, блок мультиплексоров, генератор псевдослучайных тестов, блок памяти тестов, блок управления, блок ввода, блок вывода, причем первая и вторая группы информационных выходов блока регистров подключены соответственно к входам эталонного и проверяемого микропроцессорных блоков и к первой и второй группам информационных входов блока сравнения, группа управляющих входов которого связана с группой управляющих выходов блока регистров, группа управляющих входов блока регистров соединена с группой управляющих входов блока мультиплексоров , группой входов генератора псевдо случайных тестов и первой группой управляющих выходов блока управления, вторая группа управляющих выходов которого связана с группой управлякяцих входов блока памяти тестов, группа информационных входов кото рого подключена к первой группе информационных входов блока регистров и к группе входов блока вывода, группа управляющих выходов блока памяти тестов соединена с группой управляющих входов блока управления, группа: информационных входов которого подключена к группе выходов блока ввода, первая, вторая, третья и четвертая группы информационных входов блока мультиплексоров связаны соответственно с группой выходов генератора псевдослучайных тестов, группой выходов блока ввода, группой информационных выходов блока памяти тестов и группой выходов блока сравнения, личающееся тем, что, с целью повьЕиения быстродействия, в устройство введены блок сверхоперативной памяти и блок обработки информации, причем группы управляющих входов блока сверхопеS ративной памяти и блока обработки информации соединеныс первой груп(Л пой управляющих -выходов блока управления, группа информационных входов блока сверхоперативной памяти подключена к первой группе информацион- V, ных входов блока регистров, вторая группа информационных входов которого связана с группой выходов блока сверхоперативной памяти и первой группой информационных входов блока обработки информации, вторая группа инфор. 4« мационных входов которого соединена с группой выходов бло :а мультиплексоров. 2. Устройство по п. 1, о т л ич ающееся тем, что блок обЮ работки информации содержит в каждом i -м разряде ЛК -триггер и эле:о мент ИЛИ, причем входы установки, . сброса, синхронизации и первые 3 и 1( -входы триггера связаны с первым входом элемента ИЛИ и подключены к первой группе входов блока, вторые 3 - и К -входы триггера соединены с -{ -м входом второй группы входов блока, третьи J - и К -входы триггера связаны с выходом элемента ИЛИ, второй вход которого подключен к i -му входу третьей группы входов блока, выход DК -триггера является i -м выходом блока.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3614608, кл | |||

| Телефонный аппарат, отзывающийся только на входящие токи | 1921 |

|

SU324A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1983-09-15—Публикация

1982-02-16—Подача