1

Изобретение относится к области электронной вычислительной техники и автоматики, в частности к устройствам тестового контроля электронных логических схем, построенных на цифровых элементах. Оно может быть использовано как для контроля в процессе производства, так и для профилактического контроля конструктивно съемных узлов ЦВМ, специализированных управляющих систем и средств промьшшенной автоматики.

Известно устройство для тестового контроля цифровых узлов ЦВМ, содержащее блок памяти, регистры входной и выходной тестовой информации, подключенные через блок ввода тестов к блоку памяти, блок сопряжения, соединяющий регистр входной тестовой информации со входами контролируемог узла, блок сравнения, первые входы которого соединены с регистром выходной тестовой информации, а вторые - с выходами контролируемого узла l .

Известное устройство реализует . принцип формиррвания входной и выходной тестовой информации в автономных регистрах. При этом назначение,ячеек памяти регистров однозначно опреде-,

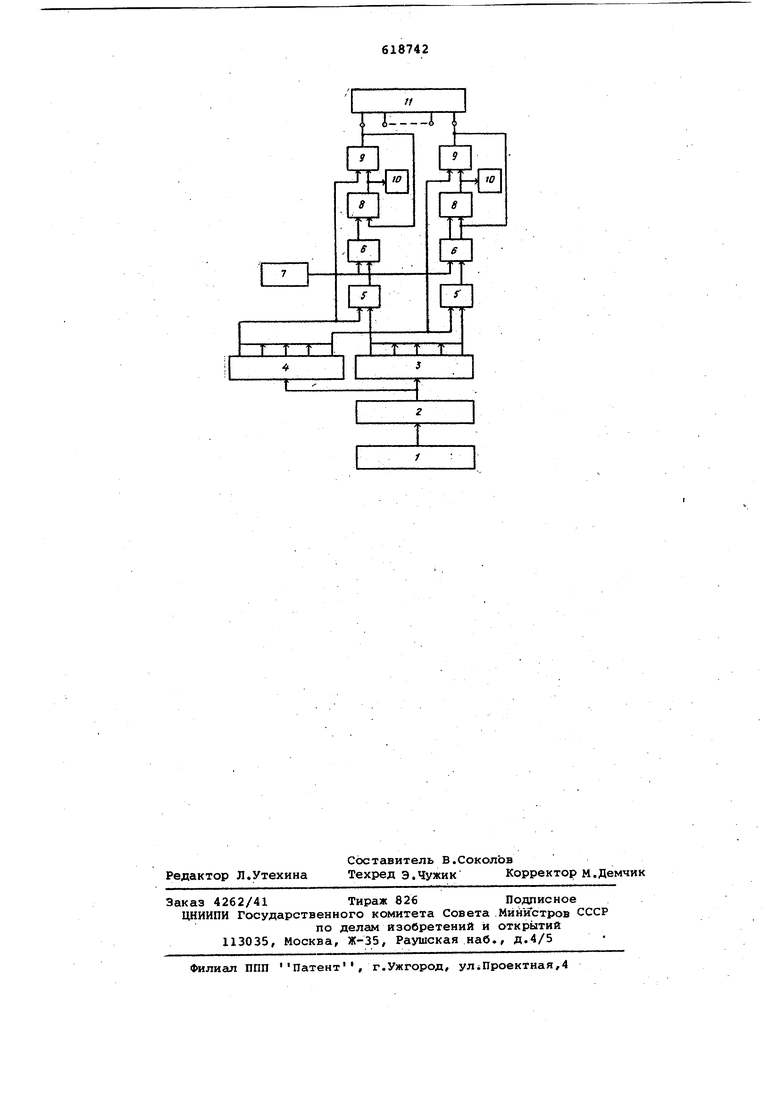

лено системой;, их связей с другими операционными элементами устройства. В результате этого ячейки памяти одного регистра используются для хранения только входных тестовых сигналов, другого - для хранения только выходных тестовых сигналов. Область применения устройства контроля,построенного по такому принципу, ограничена цифровыми узлами, у которых входы и выходы распрложены на заранее отведенных контактах контактного пол для внешних связей, т.е. узлами с упорядоченным расположением входов и выходов. При подключении к устррйству контроля узла такого типа его входы; соединяются с регистром входной информации , а выходы - с блоком сравнения. Для того чтобы с помощью этого устройства проверить узел с неупорядоч енньм расположением входов и выходов, нужно иметь соединительное устройство, которое за счет специальной раскладки проводов, соединяющих устройство контроля и узел упорядочивает внешние связи узла. Так как для каждого узла характерен индивидуальный вариант расположения входов и выходов, в состав устройства контроля должно быть включено столько соединительных устройств, .сколько узлов оно проверяв. Наиболее близким техническим решением к Изобретению является .устройство для тестового контроля цифровых у 3лрв ЦВМ, с бдержащеа. блок пам я ти, блок. ввода регистр тестов, схемы сравнения, индикаторы-и форошрозатели входных сигналов J, Выходы блока памяти через блок ввода соединены со входами регистра тестов, а выходы. схем сравнения - со входами соответствуклцих индикаторов. Устройство реализует принцип формирования входной и выходной инфо а;Ции в одном регистре. Каждая ячейка памяти регистра тестов может выполнять две функции: а)хранить код входного тестового сигнала,. б)хранить код выходного тестового сигна;ла,.. При этом входная и выходная тесто вая информация в регистре не упорядочивается в две группы, а распреде ляется в cqqjBетствиия ic функциональ ными режимами каналов, подключенных к ячейкам памяти. Функциональный режим канала задается переключателем. Бели при стыковке цифрового узла с устройством контроля,например,к перBoiiiy каналу подключается входной кон такт,то переключателем задается такой режим работы,при которся« канал посыпает на вход контролируемого уэ ла т сигнал,код которого записан в ячейку памяти регистра тестов, подключенную к первому каналу. Если к первому каналу подключается выходной контакт цифрового узла, то переключа телем задается режим, при котором канал принимает сигнал с выхода циф рового узла на схему сравнения и сравнивает его с выходным тестовым сигналом, КОТОРЫЙ поступает из той же ячейки памяти. Остальные каналы работают аналогично. Таким образом,в этом устройстве можно осуществлять привязку как вход ной, так и гвыходной; тестовой информации к любому контакту внешнего контактного поля контролируёмЪгЪ узла. В техническом отношении вместо ,пеее| сммутации проводов, соединяющих устройство контроля и контролируемый узел, это Делается перестановкой кодов в тестовых программах, что позво ляет исключить из состава устройства спехи1альное соединительное oбoj yдoвa ние и расширить область ёго.;ПРименения в тва раза по сравнению с устрой ством l . .., Устройство PJ может быть использрвано для контроля цифровых узлов,электрические схемы которых построены на элементах только родственных серий, т.е. по одному принципу, напр мер по принципу транзиа5 3р;но-транзисторной логики(ТТЛ). Элементы серий, построенных по принципу ра.зчсэ;орно -.ТРанзисторной или диоднотранзисторной логики, из-за большого различия электрических параметров, не родственны э лементам ттаи не родственны между собой. Использование известного устройства для контроля узлов, схемы которых построены на элементах неродственных серий, невозможно, так как это требует изменения уровней сигналов, вырабатываемых формирователями входных и выходных сигналов, регулирования нагрузочной способности этих формирователей и изменения порогов срабатывания у схем сравнения. Целью изобретения является расширение области применения устройства. Поставленная цель достигается тем, что в предложенное устройство введены регистр управления, блок опбрны) напряжений, дешифраторы и переключа- : тели. Выходы блока ввода соединены со входами регистра управления, выходы которого соединены с первьми входами соответствующих формирователей Входных сигналов и дешифраторов. Выходы регистра тестов соединены со втоуалля входами соответствующих, дешифраторов, выходы которых соединены с первьвми входами соответствующих переключателей. Выходы блока опорных напряжений соединены со вторьдми входами, переключателей, выходы которых соединены с первыми входами соответствующих схем сравнения.Выходы формирователей входных сигналов соединены со входами и выходами контролируемых узлов и со вторыми входами соответствующих схем сравнения, выходы которых соединены со вторыми входами соответствующих формирователей входных сигналов. Такое устройство позволяет контролировать цифровые узлы ЦВМ, построенные на основе микросхем любой серии. При этом расположение входов и выходов на контактнсчи поле для внешних связей у каЛдого узла может быть ПРОИЗВОЛЬНЫМ. На чертеже представлена функциональная Схема устройства для тестового контроля цифровых узлов ЦВМ. Устройство содержит блок памяти 1, предназначенный для хранения f&C-. товой программы, блок ввода 2, через который передается информация из блока памяти в регистр тестов 3 или регистр управления 4, дешифраторы 5,управляющие работой переключателей 6,которые служат для подключения напряжений, вырабатываемых блоком опорных напряжений 7, к схемам сравнения 8, формирователи входных сигналов 9 и индикаторы 10. Выходы формирователей входных сигналов соединены с контролируемым узлом 11. Один разряд регистра тестов 3 и один разряд регистра управления 4, выходы которых подключены ко вхо дам дешифратора 5,соединенного через переключатель 6 со входом схем сравнения 8, выходы которой подключены к формирователю 9 и индикатору 10, образуют один канал. Устпойствр содержит Vc каналов. Перед контролем из блока памяти 1 через блок ввода 2 одно информационное слово поступает в регистр управления 4 и запоминается в нем. Затем из блока памяти 1 тестовое слово поступает в регистр тестов 3 запоминается в нем. Рассмотрим работу устройства на примере одного канала, например первого, так как все каналы устройства функционируют аналогично. Если первый внешний контакт конт ролируемого узла-входной, то в процессе контроля первый канал устройства контроля функционирует как источник входных тестовых сигналов. Этот режим работы канала задается кодом, который записывается в первый разряд регистра.4. Сигнал из первого разряда регистра 4, который соответствует данному режиму канала переключает формирователь 9 в режим линейного усилителя напря жения. Выходной сигнал формирователя 9 ступает на вход контролируемого уз ла и по цепиiобратной связи на один из входов схемы сравнения 8. В этом режиме формирователь входных сигна лов совместно со схемой сравнения превращаются в стабилизатор напряже ния, опорное напряжение на который поступает с выхода переключателя 6 на второй вход схемы сравнения 8. Опорное напряжение задается следующим образом. Из блока 7 на одну группу входов переключателя 6 поступ ют четыре опорных напряжения, соответствующих уровням входных и выход ных сигналов цифровых элементов (н чертеже не показаны) ,на базе которы построен контролируемый узел. На вторую группу входов переключателя б поступают сигналы с выходов дешиф ратора 5. Ко входам Дешифратора 5 подключены два разряда: один - из регистра 3 второй - из регистра 4. Разряды регистров 3 и 4 в зависимо ти от хранящейся в них информации, могут формировать на входах дешифра тора четыре кодовых комбинации 00 01, 10, 11. В старшем разряде каждой комбинаций-закодиров на информация о том, к. какой относится сигнал, закодированный в младшем разряде. В младшем разряде закодировано логическое значение тестового сигнала. Сочетание кодов в обоих разрядах, например означает входной О комбинация 01« -йходную 1, сочетание 10 - выходной О , сочетание 11 .-выходную 1... Кодовые комбинации расшифровь1вает дешифратор 5. Выходной дешифратора включает на выходе переключателя 6 опорное напряжение в соответствии с кодовой комбинацией на входах дешифратора. При работе канала и режиме источника входных тестовых сигналов на вход дешифратора 5 поступают только две кодовых комбинации оо и 01 . Соответственно на выходе переключателя б появляются опорные напряжения входной О входная 1 ные напряжения, усиленные по мощности, повторяются на выходе формирователя 9 и передаются на вход контролируемого узла. Если первый внешний контакт .контролируемого узла-выходной, то в процессе контроля первый канал выполняет функцию проверки выходных сигналов узла и работает следующим образом. Сигнал из первого разряда регистра 4 переключает формирователь 9 в режим, при котором его передаточная функция становится равной 0. В результате прекращается обратная связь через формирователь 9 выхода схемы сравнения 8 с ее входом,и прекращается стабилизация напряжения на выходе формирователя. При этом выход формирователя становится электрически нейтральньвъ1 и не оказывает искажающего влияния на выходной сигнал контролируемого узла, поступающий в канал. По цепи обратной связи выходной сигнал контролируемого узла поступает на вход схемы сравнения 8, где сравнивается с опорным напряжением, поступающим с переключателя 6. Переключатель б в зависимости от кодовой комбинации на входах дешифратора подает на второй вход схемы сравнения одно из двух напряжений, соответствующих выходному О или выходной . Выходной сигнал схемы сравнения используется для управления индикатором 10. Если выходной сигнал контролируемого узла не совпадает с тестовым выходньм сигналом, который поступает из регистра 3, то схема сравнения вк.лючает индикатор. Схема сравнения 8 управляет индикатором и в случае, когда канал работает в режиме источника входных тестовых сигналов. При этом на обоих входах схемы сравнения присутствуют одинаковые сигналы, поэтому она регистрирует совпадение сигналов и индикатор находится в выключенном состоянии. BKjno4eHHe индикатора возможно только при наличии неисправности в самом канале. Это позволяет использовать такой режим для самоконтроля канала. Поступление в регистр 3 следующих тестов .приводит к переключению опорных напряжений на выходе переключателя 6. В результате тестовые сигналы, которыкй оперирует канал, превращаются в сигналы с нормированными уровнями напряжений. Так как все опорные напряжения регулируются, то тестовые сигналы можно получать с любыми уровнями напряжений и, следовательно, охватить весь спектр уровней тестовых сигналов, который необходимо формировать устройству для контроля цифровых узлов, построенных на элементах различных серий.

Описанный принцип позврляет постЕюить универсальное устройство, которое может быть использовано для контроля цифровьЕХ .узлов, построенных на люб элементах транзисторно-тран зисторной, резисторно-транзисторной и диодно-транзисторной логики. Настройка устройства на конкретный тип элементов занимает не более 2 мин. Таким образом, область применения предлагаемого устройства зна чительно расширена.

Возможность регулирования уровней напряжений тестовых сигналов позволяет проводить граничный контроль ««цифровых узлов, т.е. контроль с имитацией наихудших допустимых уровней входных сигналов В условиях реальной эксплуатации цифровых узлов уровни входных сигналов, как правило, соответствуют средним значениям, поэтому, если в результате контроля узлы оказываются работоспособными при наихудаоих входных сигналах, это гарантирует их работоспособность во всем диапазоне уровней входных сигналов.

Формула изобретения Устройство для тестового контроля цифровых узлов цифровой вычислительной машины (ЦВМ), содержащее блок памяти, блок ввода, регистр тестов, схемы сравнения, индикаторы и формирователи входных сигналов, причем выходы блока памяти через блок ввода соединены со входами регистра тестов выходы схем сравнения соединены со входами соответствующих индикаторов отличающееся тем, что, с целыю расширения области применения, в устройство введены регистр управления, блок опорных напряжений, дешифраторы и переключатели, выходы блока ввода соединены со входами регистра управления, выходы которого соединен с первыми входами соответствующих формирователей входных сигналов и дешифраторов выходы регистра тестов соединены со вторыми входами соответ ств)щих. дешифраторов, выходы которы соединены с первыми входами соответствующих, переключателей; выходы блок опорных напряжений соединены со siOf рыми входами переключателей, выходы которых соединены с первыми входами соответствуюищх схем сравнения; выходы формирователей входных сигналов соединены со, входами и выходами контролируемых злов и со вторыми входами соответствующих схем сравнения, выходы которых соединены со вторыми входами соответствующих формирователей входных сигналов.

Источники информации, принятые во внимание при экспертизе s

1.Диагностика неисправностей вычислительных машин. М., Наука, 1965, cai5-132.

2.Авторское свидетельство СССР № 330526, кл. Q06F 11/04, 1971

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

Авторы

Даты

1978-08-05—Публикация

1975-04-08—Подача