Изобретение относится к вычислительной технике, в частности к процессу обмена информацией между ппо- цессорами, и может быть использовано для организации параллельной рабо ть, по каналам с повышенной помехозащищенностью нескольких процессоров Цел-ъ изобретения - повышение быстродействия.

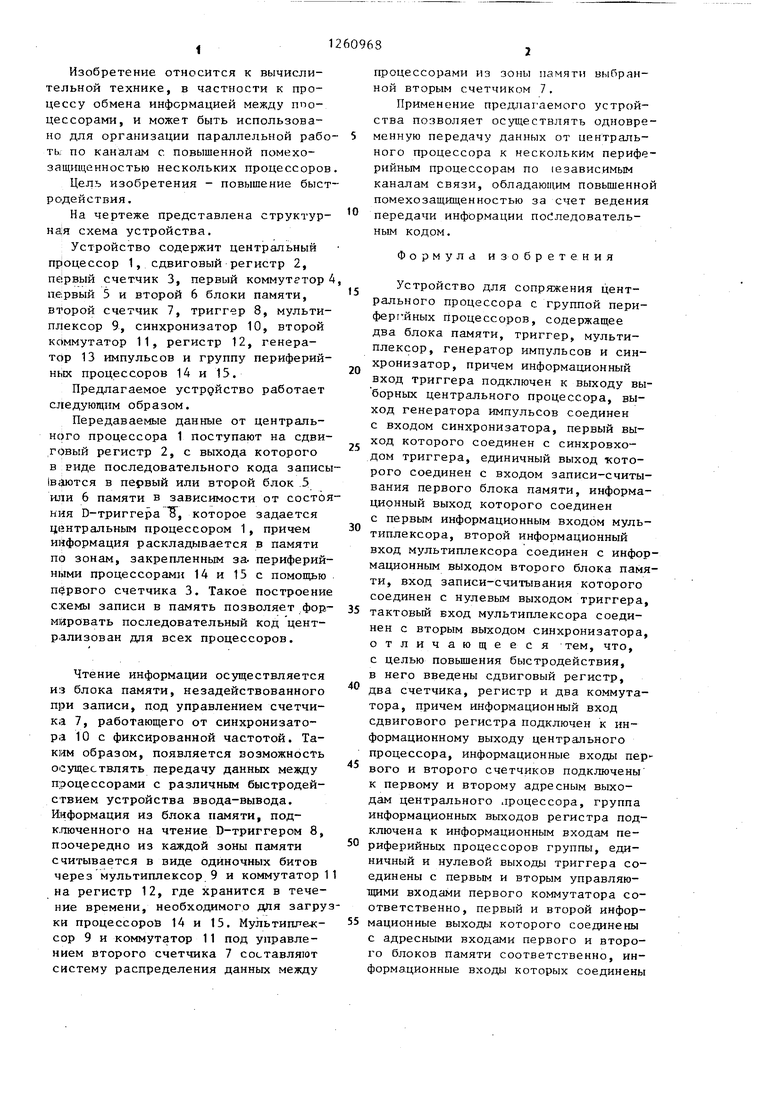

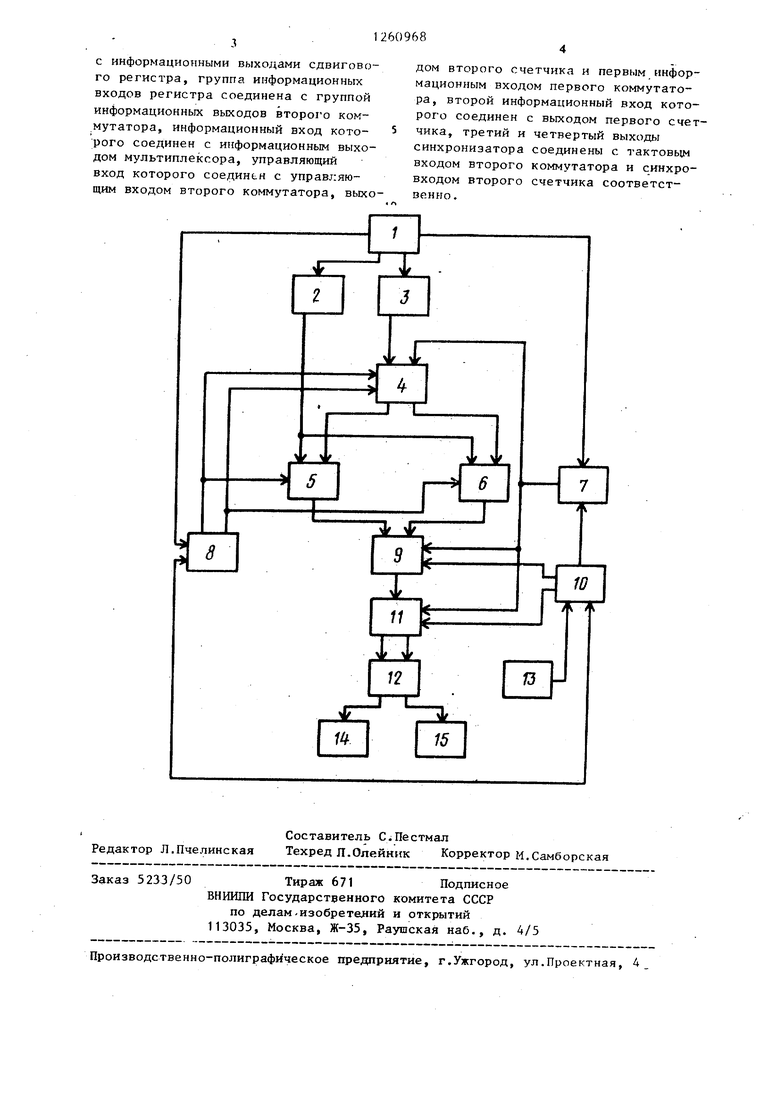

На чертеже представлена структур- ная схема устройства.

Устройство содержит центральный процессор 1, сдвиговый регистр 2, первый счетчик 3, первый коммутетор 4 первый 5 и второй 6 блоки памяти, второй счетчик 7, триггер 8, мультиплексор 9, синхронизатор 10, второй коммутатор 11, регистр 12, генератор 13 импульсов и группу периферийных процессоров 14 и 15.

Предлагаемое устройство работает следующим образом.

Передаваемые данные от центрального процессора 1 поступают на сдвиговый регистр 2, с выхода которого в виде последовательного кода записы lBi-иотся в первый или второй блок .5 или 6 памяти в зависимости от состояния D-триггера 15, которое задается центральным процессором 1, причем информация раскладывается в памяти по зонам, закрепленным за- периферийными процессорами 14 и 15 с помощью первого счетчика 3. Такое построение схемы записи в память позволяет фор- мировать последовательный код централизован для всех процессоров.

Чтение информации осуществляется

и:з блока памяти, незадействованного при записи, под управлением счетчика 7, работающего от синхронизатора 10 с фиксированной частотой. Таким образом, появляется возможность осуществлять передачу данных между процессорами с различным быстродействием устройства ввода-вывода. Информация из блока памяти, под- к.шоченного на чтение D-триггером 8, поочередно из каждой зоны памяти считывается в виде одиночных битов через мультиплексор 9 и коммутатор на регистр 12, где хранится в течение времени, необходимого дпя загруки процессоров 14 и 15. Мультипле с- сор 9 и коммутатор 11 под управлением второго счетчика 7 составляют систему распределения данных между

0 5

0

5

0

5

5

0

гфоцессорами из зоны памяти выбранной вторым счетчиком 7,

Применение предлагаемого устройства позволяет осуществлять одновременную передачу данных от центрального процессора к нескольким периферийным процессорам по 1езависимым каналам связи, обладающим повышенной помехозащищенностью за счет ведения передачи информации пойледователь- ным кодом.

Формула изобретения

Устройство для сопряжения центрального процессора с группой пери- ферг йных процессоров, содержащее два блока памяти, триггер, мультиплексор, генератор импульсов и синхронизатор, причем информационный вход триггера подключен к выходу выборных центрального процессора, выход генератора импульсов соединен с входом синхронизатора, первый выход которого соединен с синхровхо- дом триггера, единичный выход которого соединен с входом записи-считывания первого блока памяти, информационный выход которого соединен с первым информационным входом мультиплексора, второй информационный вход мультиплексора соединен с информационным выходом второго блока памяти, вход записи-считывания которого соединен с нулевым выходом триггера, тактовый вход мультиплексора соединен с вторым выходом синхронизатора, отличающее ся тем, что, с целью повьш1ения быстродействия, в него введены сдвиговый регистр, два счетчика, регистр и два коммутатора, причем информационный вход сдвигового регистра подключен к информационному выходу центрального процессора, информационные входы первого и второго счетчиков подключены к первому и второму адресным выходам центрального лроцессора, группа информационных выходов регистра подключена к информационным входам периферийных процессоров группы, единичный и нулевой выходы триггера соединены с первым и вторым управляющими входами первого коммутатора соответственно, первый и второй информационные выходы которого соединены с адресными входами первого и второго блоков памяти соответственно, информационные входы которых соединены

3

с информациотшыми выходами сдвигового регистра, группа информационных входов регистра соединена с группой информационных выходов второго ком- .мутатора, информационный вход которого соединен с информационным выходом мультиплексора, управляющий вход которого соединен с управляющим входом второго коммутатора, выхоРедактор Л.Пчелинская

Составитель С.Пестмал

Техред л.Олейник Корректор м.Самборская

Заказ 5233/50Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам.изобретелий и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

1260968

дом второго счетчика и первым информационным входом первого коммутатора, второй информационный вход которого соединен с выходом первого счетчика, третий и четвертый выходы синхронизатора соединены с тактовь входом второго коммутатора и синхро- входом второго счетчика соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Процессор для мультипроцессорной системы | 1987 |

|

SU1517035A1 |

| Устройство для сопряжения процессора с К периферийными устройствами | 1984 |

|

SU1244668A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Периферийный процессор для обработки сигналов | 1985 |

|

SU1368889A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

Изобретение относится к вычислительной технике, в частности к процессу обмена информацией между процессорами, и может быть использовано для организации параллельной работы по каналам с повышенной помехозащищенностью нескольких процессоров. Основным назначением изобретения является повьппение надежности за счет обмена информацией с несколькими удаленными процессорами. Устройство содержит центральный процессор, группу периферийных процессоров, сдвиговый регистр, регистр, два блока памяти, два счетчика, два коммутатора, мультиплексор, триггер, синхронизатор, генератор импульсов. 1 ил. N9 О) О. ;о Од 00

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1129599A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-30—Публикация

1985-03-11—Подача