ю

О5

to ел

s|

4i

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с контролем информации при записи | 1986 |

|

SU1343444A2 |

| Запоминающее устройство с контролем информации при записи | 1981 |

|

SU1003151A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Логическое запоминающее устройство | 1977 |

|

SU661609A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для ввода-вывода информации при обработке физических величин | 1981 |

|

SU966683A1 |

| Логическое запоминающее устройство | 1983 |

|

SU1124384A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств. Целью изобретения является повышение быстродействия и надежности устройства. Запоминающее устройство содержит накопитель, блок местного управления, блок контроля, регистр числа, распределитель импульсов, формирователь сигналов записи, элемент И и регистр адреса, дешифратор адреса, одновибрАтЪр, . формирователь выходнбйс сигназГов и с S5 триггер. Повышение быстродействия . (/) и надежности устройства обеспечивается за счет селекции информации при передаче и исключения останова при сбоях. 1 ил.

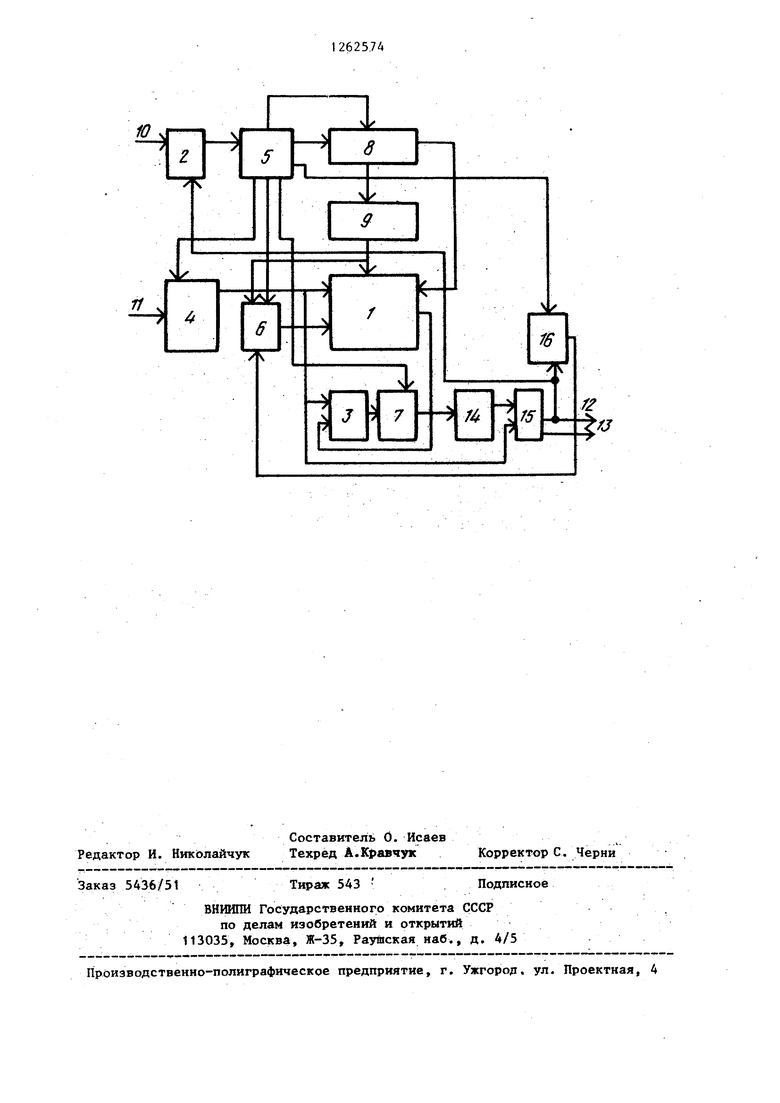

14) Изобретение относится к вычислительной технике и может быть исполь зовано при построении запоминающих устройств. Целью изобретения является повышение быстродействия и надежности устройства. На чертеже представлена схема sanoNAmarauiero устройства с контроле информации при записи. Запоминающее устройство содержит накопитель 1, блок 2 местного управ ления, блок 3 контроля, регистр 4 числа, распределитель 5 импульсов, формирователь 6 сигналов записи, элемент И 7, регистр 8 адреса, деши ратор 9 адреса, входы 10 и 11, упра ляющий выход 12 (результата .сравнения), информационные выходы 13, одновибратор 14, формирователь 15 вьтходных сигналов и триггер 16. Устройство работает следуюшдм образом. Установка в исходное состояние при подаче питания производится выходным сигналом элемента И распре делителя 5, устанавливающего в Процессе заряда КС-цепи начальное состояние на счетчике и дешифраторе распределителя 5 и регистра 8 адреса. Управляющие импульсы с входа 10 через блок 2 местного управления поступают на вход распределителя 5, работающего в режиме повторяющихся циклов-. В течение каждого цикла распределитель 5 формирует сигнал переключения адреса и последователь ность команд анализа поступившей инфорации. В начале цикла формируется сигна переключения а;дреса, поступающий ка импульс отсчета на вход регистра 8 адреса, младшие разряды с выхода которого поступают на адресные вход накопителя 1, а старшие - на вход дешифратора 9, формирующего сигналы обра щения к конкретному блоку памят накопителя 1. Во втором такте цикла производит ся запись входной информации в регистр 4 числа и ее трансляция на ин формационные входы накопителя 1 и входы блока 3 контроля. При этом На выходе накопителя 1 присутствует информация, ранее записанная по адресу, поступившему из регистра 8. Сравнение вновь поступившей (входной) информации и предыдущей (выход4 . 2 ной) информации накопителя 1 производится в блоке 3 контроля в течение этого же второго цикла. Третьим тактом цикла разрешается трансля1и1я результата сравнения через элемент И 7 на вход одновибратора 14 и далее через формирователь 15 выходных сигналов на выход 12 устройства. Если входная, информация не совпадает с выходной, сигнал с выхода блока 3 контроля, транслируемый элементом И 7, запускает одновибратор 14, сигнал с выхода которого разрешает трансляцию информации с выходов регистра 4 числа на вьпсоды 13 устройства. Таким образом, осуществляется передача не всей информации, записанной в накопителе 1, а только ее изменение. Результат сравнения (сигнал о несовпадении информации) поступает на инверсный вход блока 2 местного управления, запрещая поступления управляющих импульсов в распределитель 5. Таким образом, обеспечивается его остановка и прекращается анализ на время передачи. Помимо этого сигнал о несовпадении информации поступает.на управляющий вход триггера 16, которьй, срабатывая формирует сигнал на вход формирователя 6 сигналов записи и разрешает прием импульса соответствующей команды из распределителя 5. Результат сравнения, поступающий на вход 12. устройства, может использоваться как сигнал контроля или как сигнал, управляющими работой запоминающего устройства с источником передачи и приема информации. Четвертым тактом цикла формируется команда записи, йоступающая на информационньй вход формирователя 6 сигналов записи, транслируемая входным элементом И на выходные элементы И формирователя 6 сигналов записи. При совпадении .информации о наличии команды записи с сигналом обращения к блоку памяти накопителя Т, посту- . пающим с выходов дешифратора 9, на выходе одного из .оконечных элементо з И формирователя 6 появляется команда записи входной информации в блок накопителя 1, т.е. входная информация, 55 отличная от ран.ее записанной в ОЗУ по данному адресу и переданная на j выходы 13 устройства, записывается в накопитель 1 и появляется на его

выходах, что воспринимается блоком 3 контроля как совпадение информации. Сигнал с выхода блока 3 снимается.

По окончании работы одновибратора 14 запрещается выдача информации на выходы 12 и 13 устройства, снимаются запрет с инверсного входа блока 2 местного управления и сигнал с управляющего входа триггера 16,

В результате под воздействием управляющего из-тульса формируется пятоШ такт цикла работы распределителя 5, устанавливающий триггер 16 в исходное состояние.

Следующий управляющий импульс фор мирует следующий цикл работы распределителя 5 с анализом сигналов, поступающих по новому адресу, сформированному как двоичное число, большее предыдущего на единицу.

В случае возникновения сбоя по передаче информации, когда при несовпадении входной и выходной информации накопителя 1 информации на вы- . кодах 13 и сигнал на выходе 12 устройства не появляются, триггер 16 . остается в исходном состоянии, запись изменения информации в накопитель 1 не состоялась. Таким образом, в случае сбоя останова всего устройства не происходит, а информация передается при повторных обращениях к данному адресу.

Если при проведенном анализе входная и вьпсодная информации накопителя 1 совпадают, сигнал на выходе блока 3 контроля не появляется, передача информации на выходы 13 устройства и запись информации в накопитель 1 не производятся, так как на входе формирователя 6 сигналов записи отсутствует разрешающий сигнал с выхода триггера 16.

После 5-го такта поступающим управляющим импульсов открывается новый цикл работы, регистр 8 адреса переводится в новую адресную позицию, в которой устройство .работает по описанному алгоритму.

Формул а изобретения

Запоминающее устройство с контролем информации при записи, по авт.св. № 1003151, отличающееся тем, что, с целью повьщ1ения быстродействия и надежности устройства, в него введены одновибратор, формирователь выходных сигналов и триггер, причем информационные выходы формирователя выходных сигналов являются информационными выходами устройства, управляющий выход указанного формирователя соединен с вторым входом блока местного управления, сннхровходом триггера и я зnяется управляющи - выходом устройства, информационные входы формирователя выходных сигналов подключены к выходам регистра числа, а синх|)овхсд соединен с выходом однавибратора, вход которого подключен к выходу элемента И, адресные и управляющие входы накопителя соединены соответственно с выхода ш младших разрядов регистра адреса и выходами формирователя сигналов записи, вход разрещения которого подключен к выходу триггера, установочные входы регистра адреса и триггера с соответствующими выходами распредели- теля импульсов.

| Запоминающее устройство с контролем информации при записи | 1981 |

|

SU1003151A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-10-07—Публикация

1985-01-03—Подача