(Л

сг

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1988 |

|

SU1557680A2 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| Устройство для умножения двоичныхчиСЕл B дОпОлНиТЕльНыХ КОдАХ | 1979 |

|

SU813420A1 |

| Устройство для деления двоичных чисел | 1982 |

|

SU1103224A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| Преобразователь двоично-десятичных чисел в коде 4,2,2,1 в двоичные | 1979 |

|

SU860055A1 |

Изобретение относится к области вычислительной техники и может Пыть использовано в спе1и1ализироваиных и универсальных вьгчиcлитeльFIыx устройствах. Цель изобретения - расширение класса решаемьк задач за счет возможности преобразования в восьмеричный избыточный код. Указанная цель достигается за счет дополнительного введения в преобразователь сумматора, Двух регистров, двух триггеров, трех злементов задержки, двух элементов И-ИЛИ, двух -элементов ШИ, трех элементов И и трех элементов НЕ. Изобретение является дополнительным к авт. св. № 742924. 1 ил.

ю

О5

ьо VI

оо оо

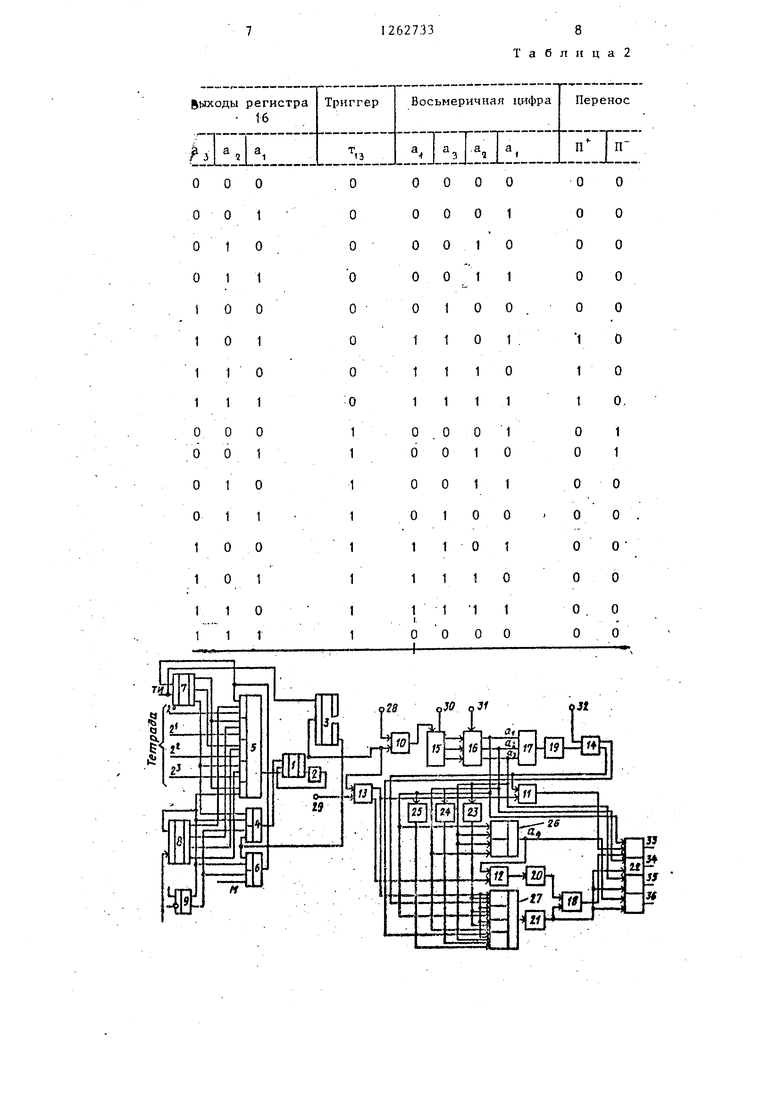

NJ Изобретение относится к вьпислитель ой технике, может быть нспольз вано в специализированных и универсальных вычислительных устройствах к является усовершенствованием уст ройства цо авт. св. № 742924. Цель изобретения - расширение класса решаемых задач за счет возможности преобразования в восьнерич НЬЙ избыточный код. На чертеже представлена схема предлагаемого преобразователя Схема содержит первый сумматор 1, элемент 2 задержки, сдвиговый регистр 3, элементы И-ИЛИ 4-6, трехразрядный регистр 7 сдвига, четырех разрядньй регистр 8. сдвига, одновиб ратор 9, элементы И 10-12, триггеры 13 и 14, регистры 15 и 16, элементы ИЛИ 17 и 18, элементы 19-21 задержки, второй сумматор 22, элементы НЕ 23-25, элементы И-ШШ 26 и 27, входы 28-32, выходы 33-36 преобразо вателя. Выход суммы сумматора 1 преобразователя двоично- чесятичных чисел в двоичные соединен с входом элемен та И 10 и D-входом триггера 13. Вто рой вход элемента И и С-вход тригге ра 13 соединены с входами 28 и 29 Устройства соответственно. Выход Элемента И 10 соединен с информацио ным входом трехразрядного регистра 15. Вход управления сдвигом в регис ре 15 соединен с входом 30 устройства. Выходы разрядов регистра 15 соединяются с входами трехразрядног регистра 16. Вход управления записью регистра 16 соединен с входом 31 устройства. Выходы разрядов регистра 16 через элемент ИЛИ 17 и элемент 19 задержки соединены с S-входом RS-триггера 14. R-вход триггера 14 соединен с входом 32 устройства. Первый (младший), второй и трети разряды регистра 16 соединены с входами первого, второго и третьего разрядов четырехразрядного сумматор

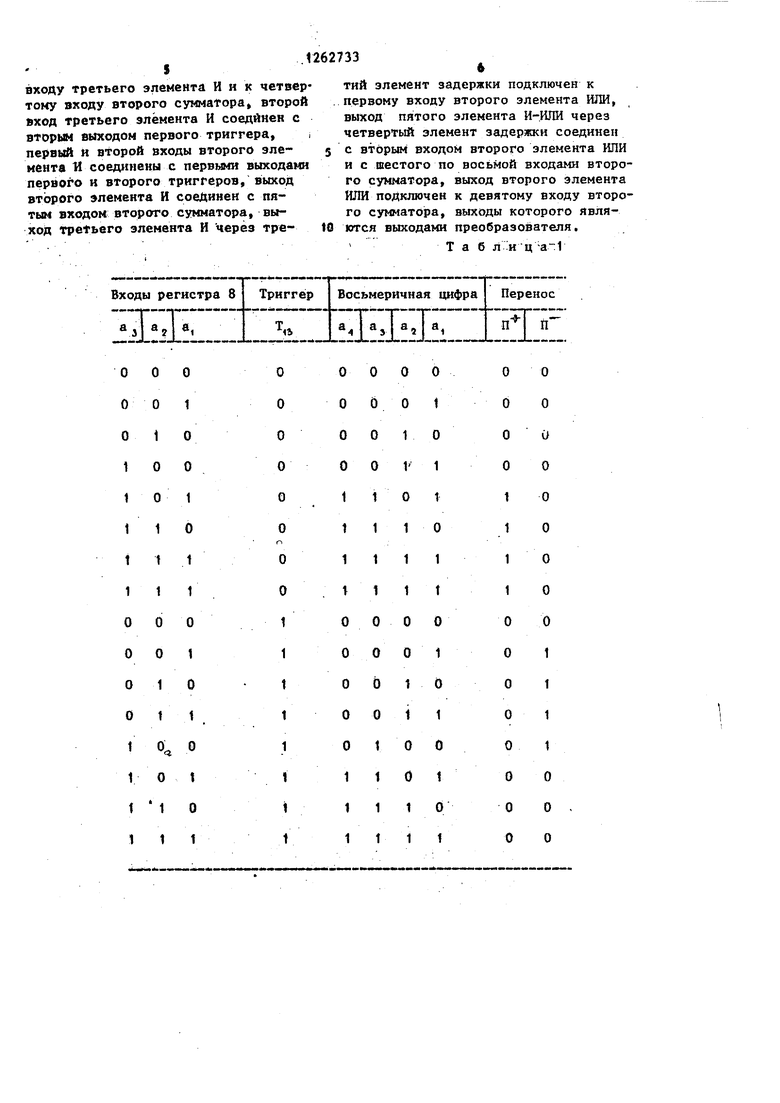

+5 +10 -1-2 -3 -4 0101 01000011 0010 0001-0000 1111 1110 1101 1100 В вспомогательной коде:

1-4 +3 2 -1-1 О -1 -2 .-3 0100 0011 0010 0001 0000 1111 1110 1101 22 и входами элементов НЕ 23-25. выходов регистра 16 считываются ри младших разряда(а , а и а,) неоткорректированной восьмеричной цифры. Четвертьй старший разряд ее а формируется в элементе И-ИЛИ 26 по алгоритму; а. а ,. С выхода элемента И-ШШ 26 а поступает на вход четвертого разряда сумматора 22. Конъюнкция единичных выходов триггеров 13 и 14 сформированная элементом И 11, поступает на второй вход младшего разряда сумматора 22. В элементе И 12 и элементе И-ИЛИ 27 формируются соответственно положительный перенос П и отрицательиьй перенос П в. старший восьмеричньй разряд, причем: П ,; ,3tT ga3Va3 a,T,,VT,,y ,( где.Т,з , ly , Т и Т - единичный и инверсный . выходы триггеров 13 и 14; сформированные переносы задерживаются в элементах 20 и 21 задержки на три такта (на один восьмеричный разряд) и через элемент РШИ 18 поступают на третий вход младшего разряда сумматора 22. Отрицательный перенос из элемента 21 задержки поступает на вторые входы второго, третьего и четвертого разрядов сумматора 22. Выходы разрядов 22 являются выходами 33-36 устройства. Устройство работает следующим образом. В преобразователе формируется дополнительный двоггчньй код масштабированной величины младшими разрядами вперед. С помощью дополнительных элементов он преобразуется в избыточный восьмеричный код. В по следнем используется основное и вспомогательное кодирование, Б основном коде восьмеричные цифры представляются следующим образом: В преобразователь двоично-десяти ные цифры поступают последовательно После поступления каждой цифры на вход -29 в такте, отведенном для передачи знака, подается сигнал записи, поступающий на D-вход триггера 13, поэтому в триггер запишется знак преобразуемого числа еще до завершения преобразования. После завершения преобразования на вход 28 поступает сигнал разрешения выда чи восьмеричного кода длительностью в один цикл. По этому сигналу элемент И 10 открывается не меняясь, К моменту прихода триады, следущей за первой, отличной от нуля, триггер 14 переходит в единичное состояние. Алгоритм формирования восьмеричной цифры не меняется. Оче редная восьмеричная цифра складывается с переносом И или П в сумматоре 22, Если преобразуемое число ее имеет знак -, сумма цифры и переноса увеличивается на единицу младшего разряда, формируемзто элементом И 11, В результате формирова ние восьмеричной. 11ИФРЫ на выходах (S , Sj, 3,2, S ) и двоичньп код числа поступает на вход регистр 15, на вход управления сдвигом кото рого поступает непрерывная тактовая серия, В первом, втором и третьем такта цикла в регисгр 15 запишутся три младших разряда двоичного числа, которые затем по сигналу зиписи, поступающему на вход 31, перепишутся в регистр 16, В дальнейшем в регистр 16 записывается 4-6 разряды двоичного числа, которые опять перепишутся в регистр 16, и так далее В результате на выходах регистра 16 формируется последоватёльно-парал-. лельньй код, и котором триады передаются последовательно друг за другом, а разряды каждой триады - парал лельно Время передачи одной,триады составляет три такта. Если младшие триады числа нулевые, триггер 12 (предварительно сброшенный в ноль |по входу 32) остается в нуле, а. : П п- О, С вЬпсодов сумматоров считьшается восьмеричный ноль 0000. Пусть в регистр 16 поступила первая триада, отличная от нуля. Благодаря трехтакт ному элементу 19 задержки триггер 14 перейдет в единичное состояние лишь к приходу следующей триады. На выходах регистра 16 и элемента И-ИЛИ 26 будет формироваться восьмеричная цифра, на выходах элементов И 12 и И-Ш1И 27 - переносы в соответствии с табл. 1, При поступлении на входы сумматора 22 первой восьмеричной цифры, отличной от нуля, переносы II П на входах сумматора 22 отсутствуют и цифра проходит на входы устройства происходит в соответствии с табл, 2, Фбрмула изобретения Преобразователь двоично-десятичных чисел в двоичные по авт, ев, № 742924, отличающийся тем, что, с целью расширения класса решаемых задач за счет возможности преобразования в восьмеричный избыточный код, в него введены сумматор, два регистра, дна триггера, три элемента задержки, два элемента Н-ИПИ, два элемента ИЛИ, три элемента И, три элемента НЕ, причем выход суммы первого сумматора соединен с первыми входами первого триггера и первого элемента И, вторые входы которых соединены собтветственно с информационным входом и входом разрешения вьщачи восьмеричного кода преобразователя, выход первого элемента И подключен к информационному входу первого регистра, вход управления сдвигом которого соединен с тактовым входом преобраз.ователя, выходы разрядов первого регистра соединены с соответствующими информационными входами второго регистра, выходы которого через первый элемент ШШ подюпочены к входу второго элемента задержки, выходом соединенного с первым входом второго триггера, второй вход которого пб цключен к установочному входу преобразователя, выходы второго регистра соединены с первым, вторым и третьим входами второго сумматора, входами первого, второго и третьего элементов НЕ, с соответствующими входами четвертого и пятого элементов И-ИЛИ, выходы первого, второго н третьего элементов liE подключены к входам пятого элемента И-ИЛИ, выход четвертого элемента И-ИЛИ подключен к первому входу третьего элемента Инк четвертому входу второго сумматора второй вход третьего элемента И соединен с вторым выходом первого триггера, ; первый и второй входы второго элемента И соединены с первыми выходами первого и второго триггеров, выход второго элемента И соединен с пятым входом второго сумматора, выхоД третьего элемента И через тре- 10

о о о о о о

о

1

О О 1

О

1 1 О

1

1 1 10

п

о о 1 1 1 1 1

1 1

1111 1 1

1

1

о

О О О 1 О

1

о

1 1

о

о;, О

01

1t

1

i

О

t 1

1

о

о о о о 1 1 1 1 о о о о о о о о

о о о о о о о о о 1 1 1 1 о о о

о 1

о

1 1

1

1 о

о 1 1 о о

1

1 1

1111 тиЙ элемент задержки подключен к первому входу второго элемента ИЛИ, выход пятого элемента И-ИЛИ через четвертый элемент задержки соединен с вторым входом второго элемента ИЛИ и с шестого по восьмой входами второго сумматора, выход второго элемента ИЛИ подключен к девятому входу второго сумматора, выходы которого являются выходами преобразователя, Т а б ji :и ц

Т а 6 л II ц а 2

| Преобразователь двоично-десятичных чисел в двоичные | 1978 |

|

SU742924A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1984-10-09—Подача