1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей. j

Известен преобразователь двоичнодесятичных чисел в двоичные, содержащий двоично-десятичный регистр, элементы И и ИЛИ, сумматоры, выходы которых соединены со. входами двоично-де-|д сятичного регистра 13 .

Недостаток известного преобразователя бостоит в низком быстродействии.

Наиболее близким к предлагаемому по технической сущности и схемному . S решению является преобразователь двоично-десятичных чисел в коде 4, 2, 2, 1 в двоичные, содержащий двоичнодесятичный регистр, состоящий ив трех тетрад, первый и второй сумиаторы, 20 выход первого разряда младшей тетрада двоично-десятичного регистра и выходы второго сумматора являются разрядными выходс1ми преобразователя 2j . „

Недостаток этого преобразователя также состоит в низкой скорости преобразования, связанной с большим числом циклов сдвига, суммирования и перезаписи преобразуемого числа в двоично-десятичный регистр. 30

Цель изобретения - увеличение скорости преобразования.

Поставленная цель достигается тем, что в преобразователь двоично-десятичных чисел в коде 4, 2, 2, 1 в двоичные, содержащий двоично-десятичный регистр, состоящий из трех тетргщ, первый г второй сумматоры, выход первого разряда млещшей тетрады двоично-десятичного регистра и выходы второго сумматора являются разрядными выходами преобразователя-, введен преобразователь кода 4, 2, 2, 1 в код 8, 4, 2, 1, входы которого соединены с соответствующими выходами старшей тетрады двоично-десятичного регистра, а выход 1-го разряда (1-1-4) преобразователя кода 4, 2, 2, 1 в код 8, 4, 2, 1 соединен с входами 1-го и (|+2)-ого разрядов первого сумматора, выход j-oro () разряда которого соеда{мен со входами (J+l)-ro и (J+ +3)-ого разрядов второго сумматора, выход первого разряда средней тетрадол двоично-яесятичиого регистра соединен со входа ю первого и третьего разрядов втсфого суАматора, выход второго разряда средней тетрады двоичио-десятичиого регистра соединен со входом переноса первого сумматора, а выходы

третьего и четвертого разрядов средней тетрады двоично-десятичного регистра соединены соответственно со входами первого и второго разрядов первого сумматора, выходы второго, третьего и четвертого разрядов младшей тетрады двоично-десятичного регистра соединены соответственно со ззходами переноса, первого и второго саэрядов второго сумматора.

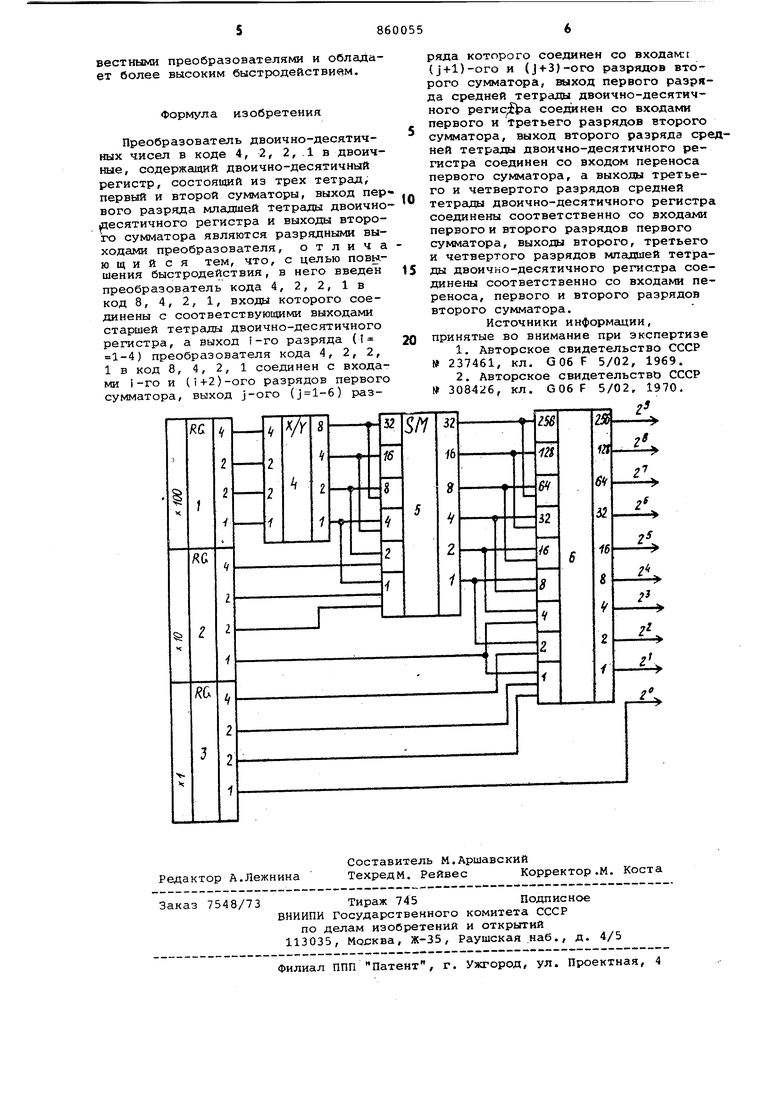

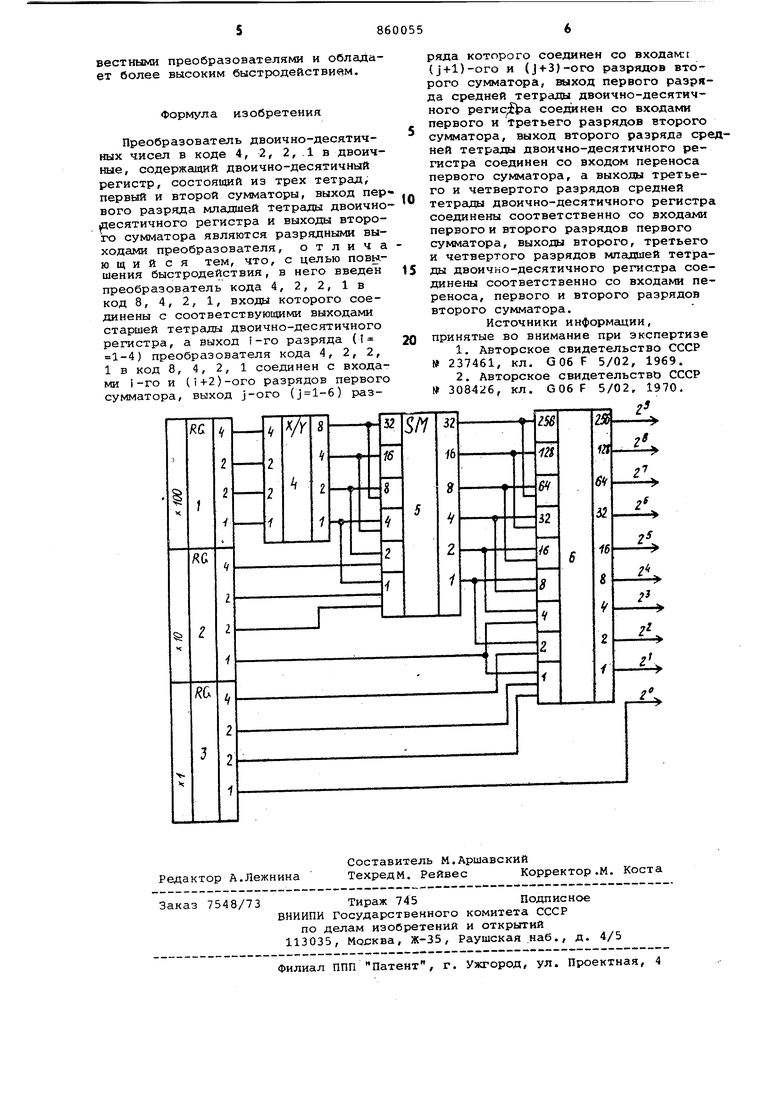

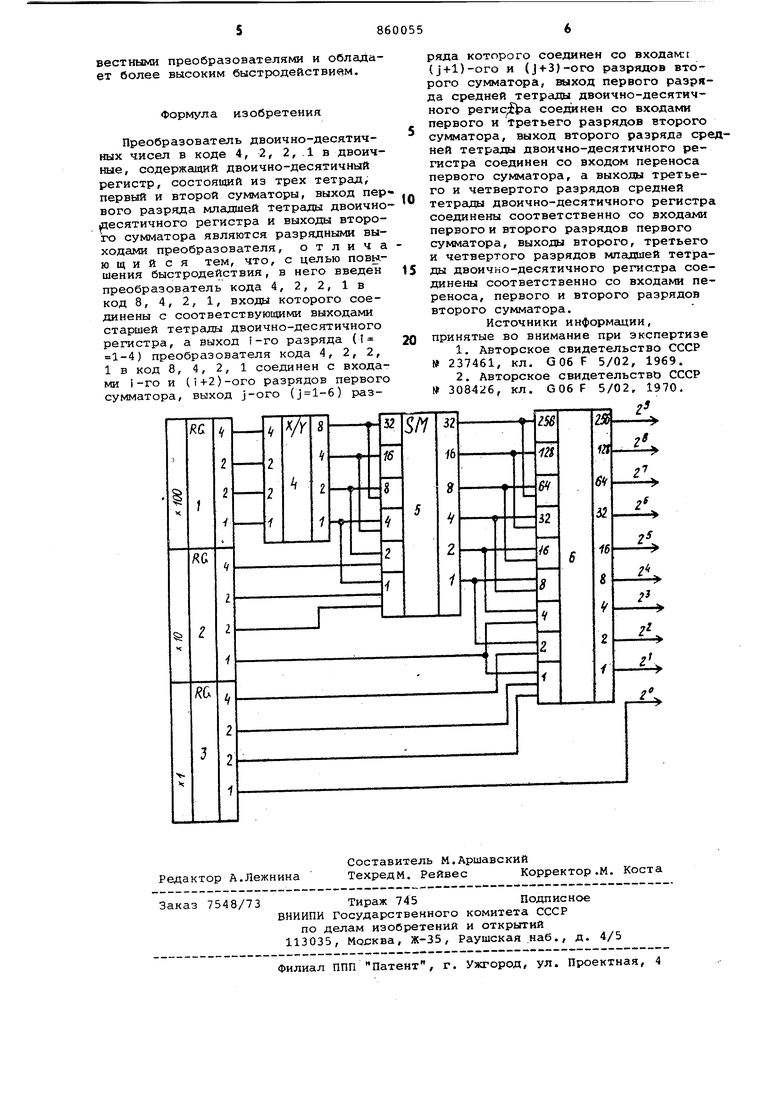

На чертеже изображена функциональная схема предлагаемого преобразователя . .

Схема содержит тетрады 1-3 входного двоично-десятичного регистра, преобразователь 4 кода 4, 2, 2, 1 в код 8, 4, 2, 1, сумматоры 5 и 6. Разряды двоично-десятичного числа представлены в коде 4, 2, 2, 1.

Выходы разрядов тетрады 1 подключены на входы преобразователя 4 кода выходы которого подключены ко входам сумматора 5, имеющим тот же вес, а также ко входам со сдвигом на два разряда в сторону старших разрядов. Выходы разрядов с весами 2, 2, 4 тетрады 2 подключены ко входЕим младших разрядов сумматора 5, выход с весом 4 - ко входу с весом 2, выходы с весами 2 - ко входу с весом 1. Выходы сумматора 5 подключены ко входам сумматора б, имеющим удвоенный вес, а также со сдвигом ко входам, имеющим восьмикратный вес, Выхс тетрады 2 с весом 1 подключен ко входам йумматора 6 с весом 1, а выходы тетрады 3 с весами 2 подключены ко входам сумматора 6 с весом 1. Выход тетрады 3 с весом 4 подключен ко входу сумматора 6 с весом 2. Выходы сумматора б и выход с весом 1 тетрады 3 являются выходами устройства.

Устройство работает следующим образом.

На преобразователь 4 поступает цифра старшего десятичного разряда преобразуемого числа в коде 4, 2, 2, 1 На выходы преобразователя 4 цифра старшего десятичного разряда преобразуемого числа поступает в коде 8, 4, 2, 1. Этот код поступает на входы сумматора 5 с весами 8, 4, 2, 1 и со сдвигом на два разряда в сторону старших разрядов на входы с весами 32, 16, 8, 4, т.е. значение цифры старшего разряда суммируется с этим значением, умноженным на четыре.

Таким образом, значение цифйы старшего разряда преобразуемого числа умножается на сумматоре 5 на пять. На разряды сумматора 5 с весом 2 и 1 подключены также выходы разрядов тетрады 2 с весами 4, 2, 2 так, что на сумматор 5 поступает значение цифры второго десятичного разряда исходного числа, деленное на два.

Код на выходах сумматора 5 представляет сумму цифры старшего разряда исходного числа, умноженной на пять, с половиной цифры следующего десятичного разряда, выходам разрядов сумматора 5 присваивается удвoeffный вес (т.е. выход с весом 32 считаемся имеющим вес 64, выход с весом 16 - имеющим вес 32 и т.д.) . В этом случае код на выходах сумматоjpa представляет собой сумму цифры Старшего разряда, умноженной на десять, со значением цифры следующего десятичного разр5вда исходного числа. Код с выходов сумматора 5 с учетом присвоенных весов поступает на входы сумматора 6, имеющие те же веса (64 32 и т.д.), а также со сдвигом на два разряда в сторону старших разрядов на входы с весами 256, 128 и т.д., т.е. значение кода суммируется со .своим значением, умноженным на четыре. Таким образом значение кода умножается на сумматоре 6 на пять. На разряды сумматора 6 с весами 2 и 1 подключены также выходы разрядой тетрады 3 с весами 4, 2, 2, т.е на сумматор б поступает значение цифры третьего десятичного разряда исходного числа, деленное на дв&. Коду на выходах сумматора 6 также присвоен удвоенный вес, т.е. он представляет сумму кода, поступающего с сумматора 5, умноженного на десять, и кода цифры третьего разряда исходного числа. Таким образом устройство реализует алгоритм преобразования двоично-десятичного числа в двоичное. После записи исходного числа в регист 3 через время, необходимое для срабатывания преобразователя 4 и сумматоров, на выходах сумматора 6 фиксируется двоичный код преобразуемого числа.

В случае, если исходное число представлено в коде 8, 4, 2, 1, необходимо исключить из устройства преобразователь кода 4, 2, 2, 1 в код 8, 4, 2, 1 старшего разряда и ввести преобразователи кода 8, 4, 2, 1 в код 4, 2, 2, 1 в остальных разрядах, при этом выходы разрядов тетрады 1 подключаются непосредственно На входы последних, выходы которых подключаются на входы сумматоров 5 и 6 аналогично. Быстродействие устройства при этом не меняется.

По сравнению с известными устройствами, работающими по методу сдвига, суммирования и перезаписи кода преобразуемого числа в регистр или устройствами преобразования методом поразрядного сдвига кода каждой тетрады и суммирования на последовательных сумматорах, предлагаемое устройство является существенно более быстродействующим.

Использование предлагаемого устройства позволяет уменьшить число каскадов сумматоров по сравнению с известными преобразователями и обладает более высоким быстродействи м. Формула кзобретения Преобразователь двоично-десятичных чисел в коде 4, 2, 2, 1 в двоичные, содержащий двоично-десятичный регистр, состоящий из трех тетрад, первый и второй сумматоры, выход пер вого разр5ада младшей тетрады двоично десятичного регистра и выходы второго сумматора являются разрядными выходами преобразователя, о т л и ч а ю щ и и с я тем, что, с целью повышения быстродействия, в него введен преобразователь кода 4, 2, 2, 1 в код 8, 4, 2, 1, входы которого соединены с соответствующими выходами старшей тетрады двоично-десятичного регистра, а выход i-ro разряда ( 1-4) преобразователя кода 4, 2, 2, 1 в код 8, 4, 2, 1 соединен с входами i-ro и (i+2)-oro разрядов первого сумматора, выход j-oro () разW

S/V

2Х

156 ряда которого соединен со входамп (j+l)-oro и (j+3)-oro разрядов второго сумматора, выход первого разряда средней тетрады двоично-десятичного регисДЬа соеданен со входами первого и третьего разрядов второго сумматора, выход второго разряда средней тетрады двоично-десятичного регистра соединен со входом переноса первого сумматора, а выходы третьего и четвертого разрядов средней тетрады двоично-десятичного регистра соединены соответственно со входами первого и второго разрядов первого сумматора, выходы второго, третьего и четвертого разрядов младшей тетрады двоично-десятичного регистра соединены соответственно со входами переноса, первого и второго разрядов второго сумматора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 237461, кл. Q06 F 5/02, 1969. 2.Авторское свидетельство СССР № 308426, кл. G06F 5/02, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU723567A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1979 |

|

SU877521A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1973 |

|

SU517890A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ИЗ ДЕСЯТИЧНОЙ СИСТЕМЫ СЧИСЛЕНИЯ В ДВОИЧНУЮ | 2003 |

|

RU2248094C2 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

«G

2

/«.

Авторы

Даты

1981-08-30—Публикация

1979-10-10—Подача