Изобретение относится к средствам измерительной, техники и может быть использовано для измерения скорости непрерывных и квазинепрерывных потоков, в частности газовых и жидкостных потоков.

Цель изобретения - обеспечение возможности измерения скорости квазиНепрерывного потока и уменьшение погрешности измерения.

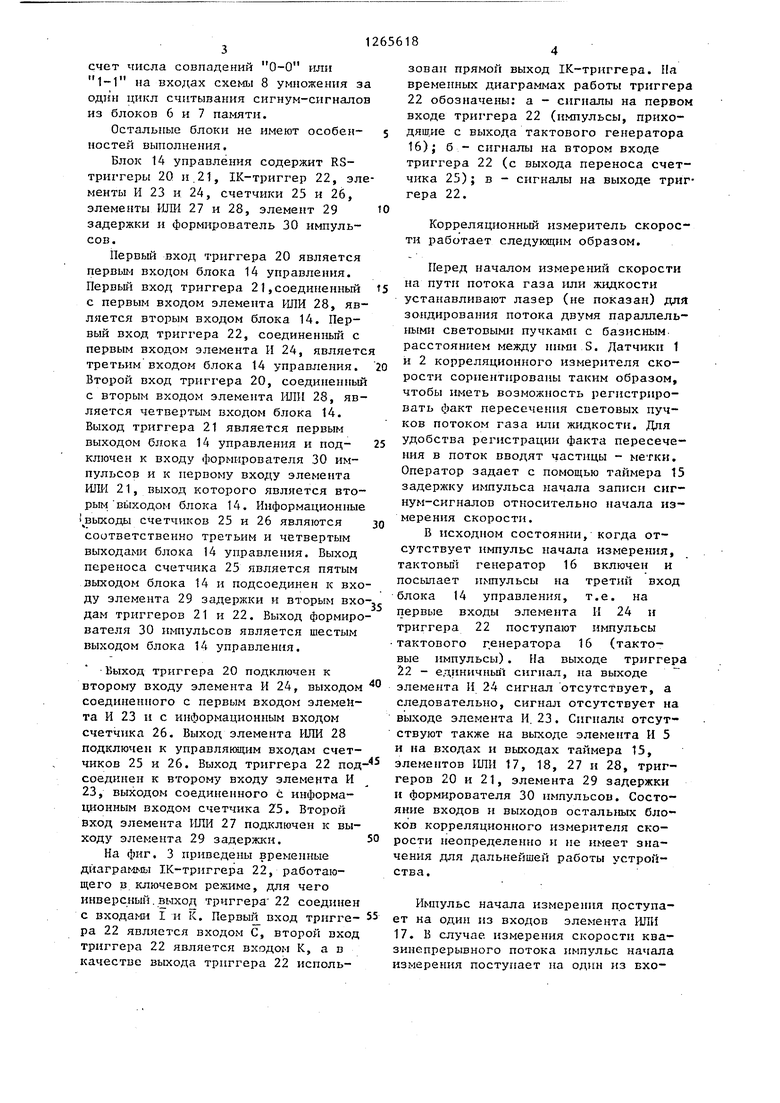

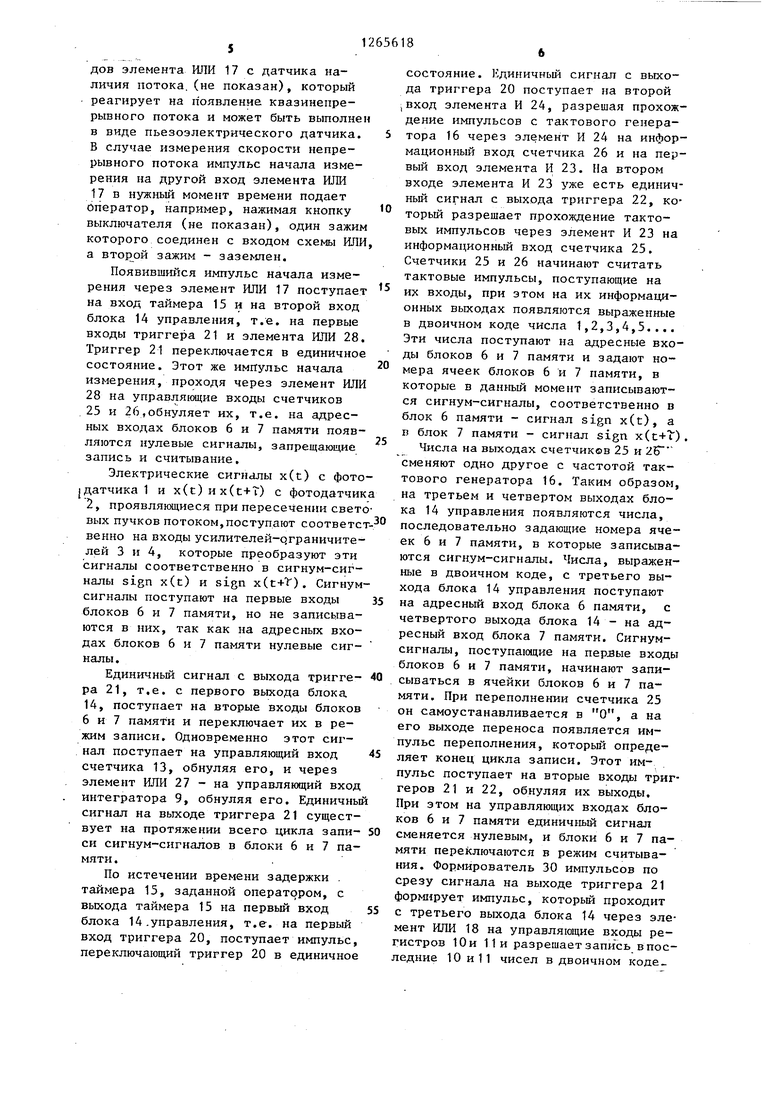

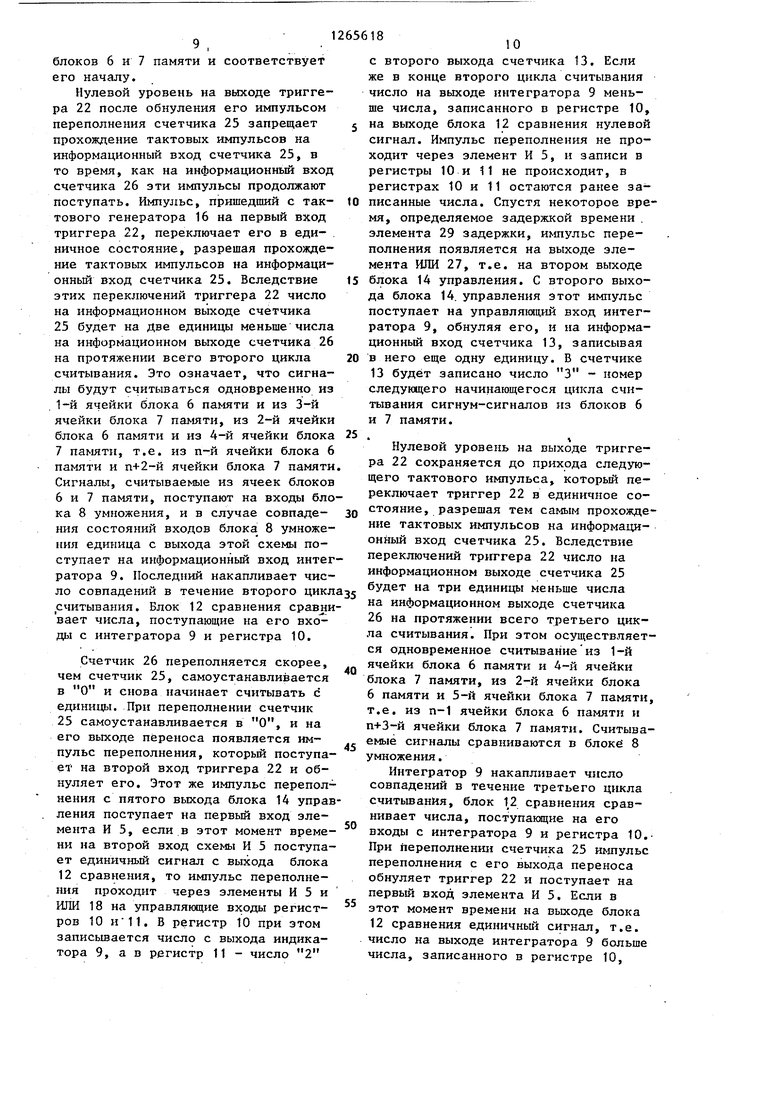

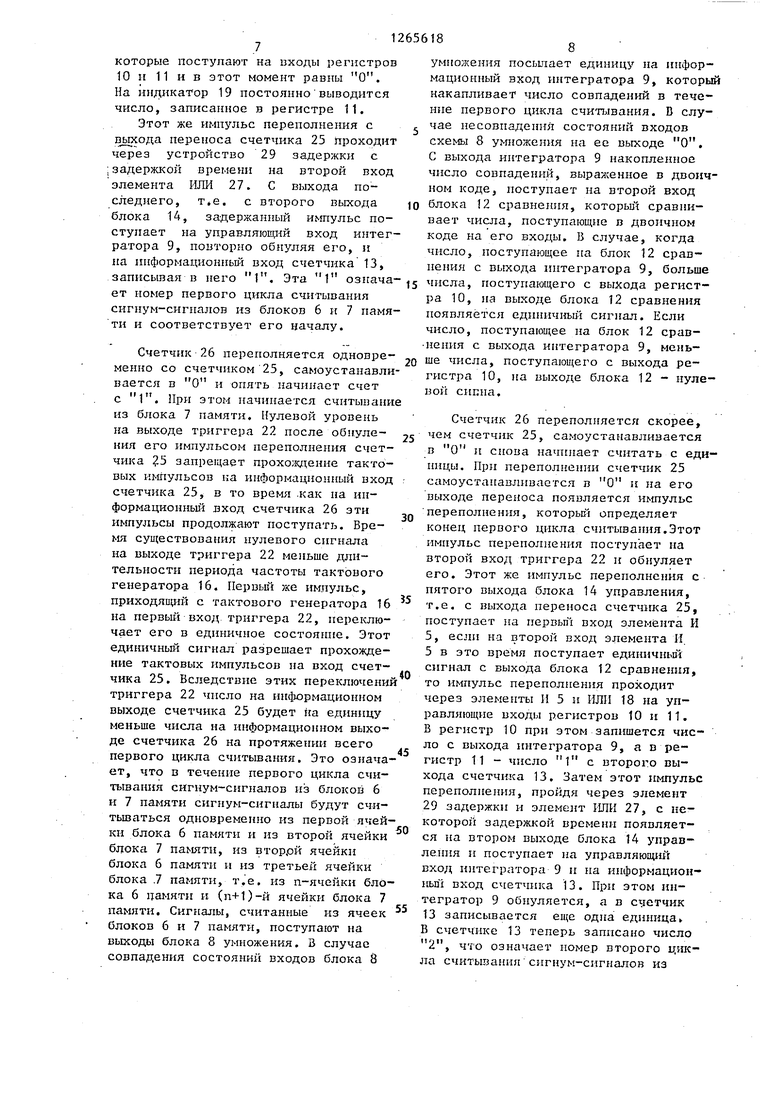

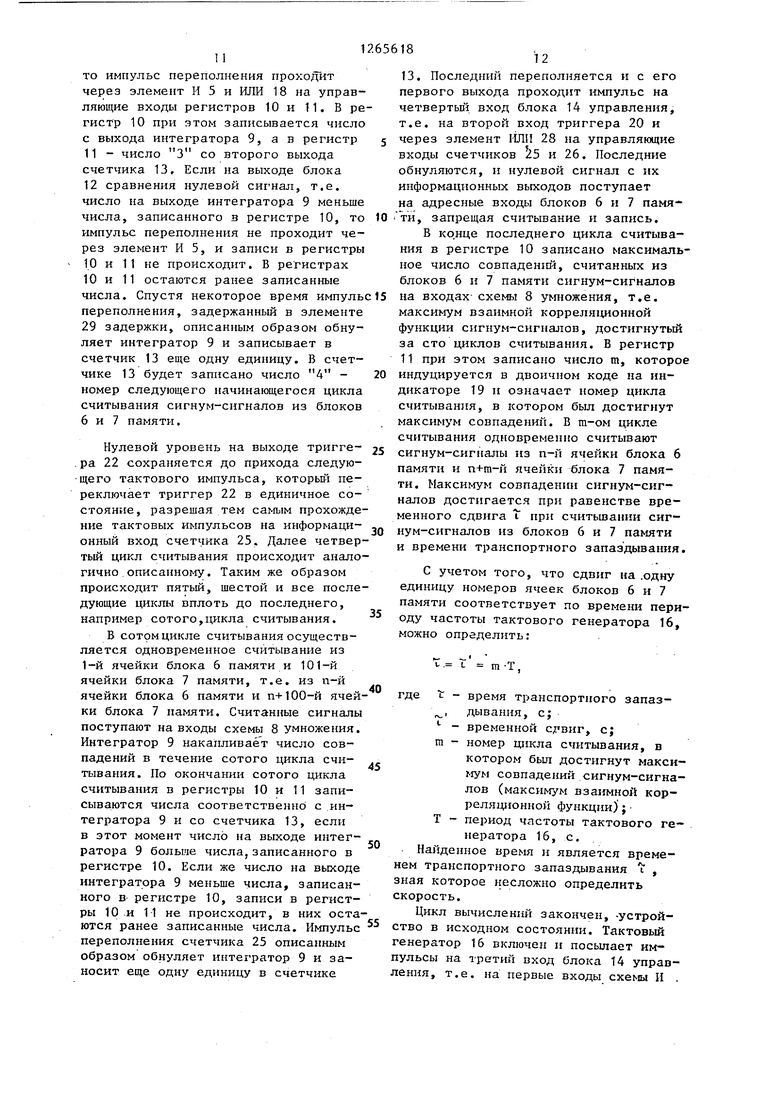

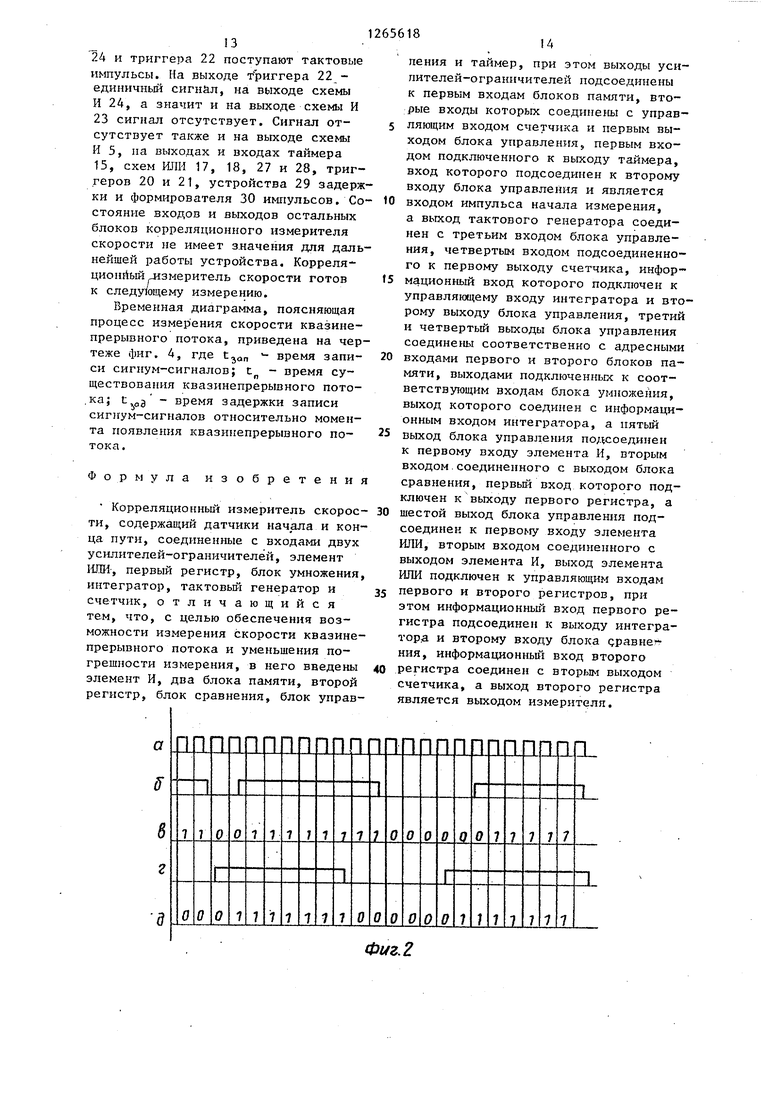

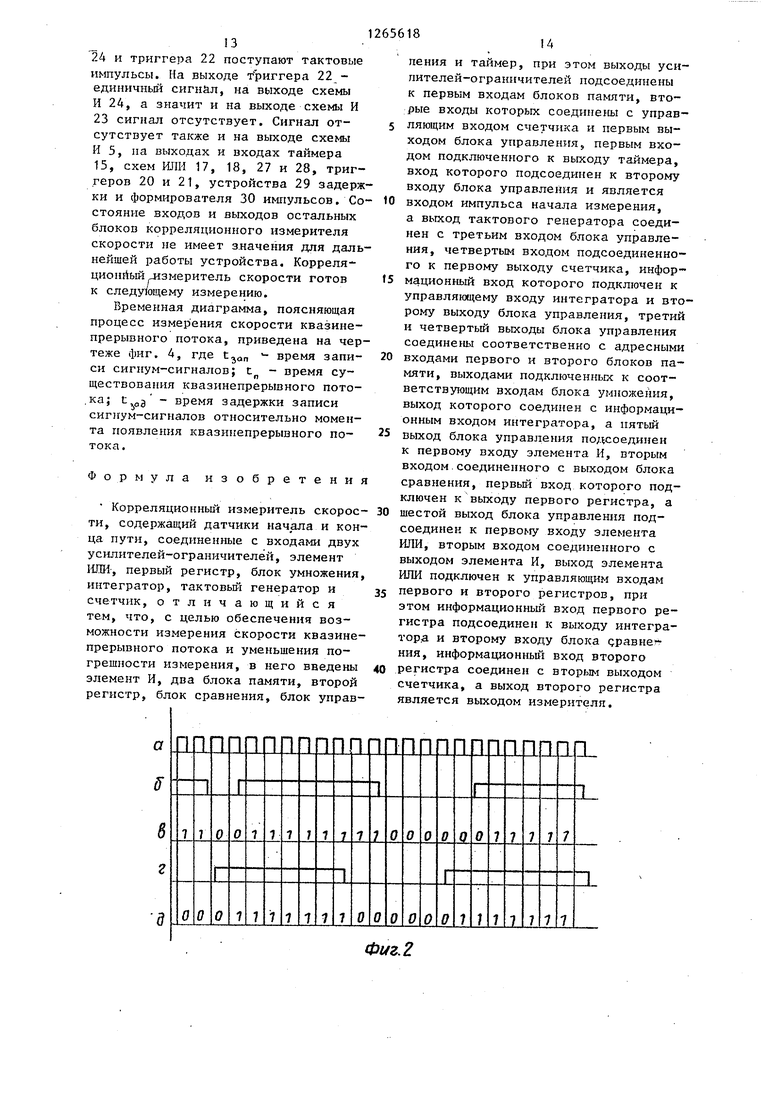

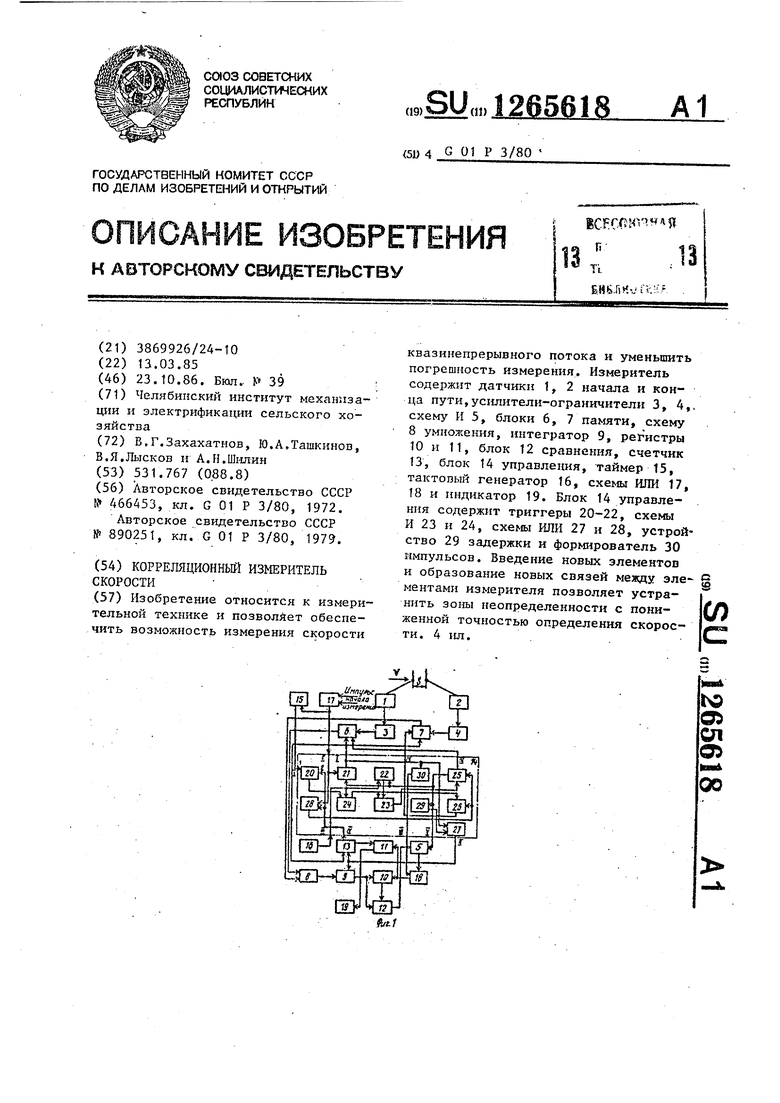

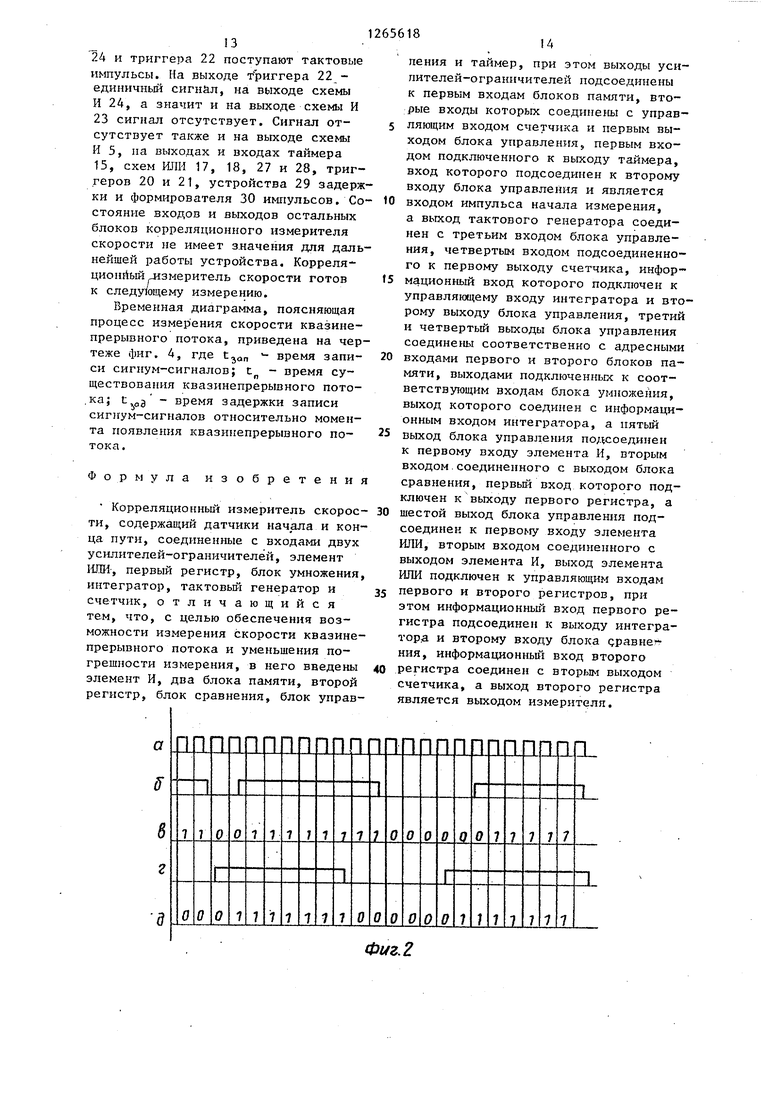

На фиг. 1 представлена функциональная схема корреляционного измерителя скорости; на фиг. 2 - временные диаграммы, поясняющие работу блоков памяти; на фиг. 3 - временные диаграммы, поясняющие работу ключевого генератора; на фиг. 4 - временная диаграмма, поясняющая процесс измерения скорости квазинепрерывного потока.

Корреляционный измеритель скорости (фиг. 1) содержит датчики 1 и 2 (Начала и конЦа пути, усилители-огра(ничители 3 и 4, элемент И 5, блоки и и 7 памяти, блок 8 умножения, интегратор 9, регистры 10 и 11, блок l2 сравнения, счетчик .13, блок 14 управления, таймер 15, тактовый генератор 16, схемы Ш1И 17 и 18 и индикатор 19.

Выходы датчиков 1 и 2 .начала и

конца пути соответственно подключены к входам усилителей-ограничителей 3 и 4, выходами подсоединенных соответственно к первым входам блоков 6 и 7 памяти. Вторые входы последних соединены с управляющим входом счетчика 13 и первым выходом блока 14 управления, первым входом подключенного к выходу таймера 15, вход которого, являющийся входом импульса начала измерения, подсое-динен к второму входу блока 14 управления и выходу элемента ИЛИ 17, первый вход которого является входом импульса начала измерения с датчика наличия потока (не показан). Второй вход элемента ИЛИ 17 является входом импульса начала измерения с выключателя (не показан). Выход тактового генератора 16 соединен с третьим входом блока 14 управления, четвертым входом подсоединенного к первому выходу счетчика 13, второй вход которого подключен к управляющему входу интегратора 9 и второму выходу блока 14 управления. Третий и четверTbrii выходы блока 14 управления соединены соответственно с адресными вхо-

ами блоков 6 и 7 памяти, выходами одключенных к соответствующим вхоам блока 8 умножения, выход которого соединен с информационным входом интегратора 9. Пятый выход блска 14 управления подсоединен к первому входу элемента И 5, вторым входом соединенного с выходом блока 12 сравнения, первый вход которого подключен к выходу регистра 10. Шестой выход блока 14 управления подсоединен к первому входу элемента ИЛИ 18, вторым входом соединенного с выходом элемента И 5. Выход элемента ИЛИ 18 подключен к управляющим входам регистров 10 и 11. Информационный вход регистра 10 подсоединен к выходу интегратора 9 и второму входу блока 12 сравнения. Информационный вход регистра 11 соединен с вторым выходом счетчика 13, а выход регистра 11, являющийся выходом измерителя скорости, подключен к ; входу индикатора 19.

На фиг. 2 приведены временные диаграммы работы блоков 6 и 7 памяти, где а - импульсы тактового генератора 16; б - сигнал sign х(г.) на входе блока 6 памяти; в - содержимое ячеек блока 6 памяти; г - сигнал sign x(t+i) на входе блока 7 памяти; д - содержимое ячеек блока 7 памяти.

Сигнум-сигналы sign х (t) и sign X (t+t) записьтаются соответственно в блоки 6 и 7 памяти с частотой тактового генератора 16 в виде последовательностей О и 1. При этом период частоты тактового генератора 16 должен быть на порядок меньше минимально возможной длительности импульса сигнум-сигналов sign x(t) и sign X (t+t), а изменение сигнум-сигналов зависит от числа частиц-меток, пересекакяцих световой пучок и фиксируемых датчиками 1. и2. Частота считывания из блоков 6 и 7памяти равна частоте записи, так как осуществляется также с частотой тактового генератора 16. При этом на выходах блоков 6 и 7 памяти появляются точные копии сигнум-сигналов sign x(t) и sign x(t+t).

Схема 8 умножения выполТ1ена в виде логической схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, интегратор 9

и счетчик 13 выполнены каждый в виде

суммирующего группового счетчика. Интегратор 9 обеспечивает подсчет числа совпадений 0-0 шш 1-1 на входах схемы 8 умножения з один цикл считывания сигнум-сигнало из блоков 6 и 7 памяти. Остальные блоки не имеют особенностей выполнения. Блок 14 управления содержит RSтриггеры 20 и.21, 1К-триггер 22, эл менты И 23 и 24, счетчики 25 и 26, элементы ИЛИ 27 и 28, элемент 29 задержки и формирователь 30 импульсов. Первьш вход триггера 20 является первьм входом блока 14 управления. Первый вход триггера 21,соединенный с первым входом элемента ИЛИ 28, является вторым входом блока 14. Первый вход триггера 22, соединенньш с первым входом элемента И 24, являетс третьим входом блока 14 управления. Второй вход триггера 20, соединенный с вторым входом элемента ШШ 28, является четвертым входом блока 14. Выход триггера 21 является первым выходом блока 14 управления и подключен к входу формирователя 30 импульсов и к первому входу элемента ИШ1 21, выход которого является вторымвь1ходом блока 14. Информационные выходы счетчиков 25 и 26 являются соответственно третьим и четвертым выходами блока 14 управления. Выход переноса счетчика 25 является пятым выходом блока 14 и подсоединен к вхо ду элемента 29 задержки и вторым вхо дам триггеров 21 и 22. Выход формиро вателя 30 импульсов является шестым выходом блока 14 управления. Выход триггера 20 подключен к второьгу входу элемента И 24, выходом соединенного с первым входом элемента И 23 и с информационным входом счетчика 26. Выход элемента ИЛИ 28 подключен к управляккцим входам счетчиков 25 и 26. Выход триггера 22 под соединен к второму входу элемента И 23, выходом соединенного с информационным входом счетчика 25. Второй вход элемента ИЛИ 27 подключен к выходу элемента 29 задержки. На фиг. 3 приведены временные диаграгфи 1К-триггера 22, работающего в ключевом режиме, для чего инверсный.выход триггера 22 соединен с входами I и К. Первый вход триггера 22 является входом С, второй вход триггера 22 является входом К, а в качестве выхода триггера 22 использовап прямой выход 1К-триггера. На временных диаграммах работы триггера 22 обозначены: а - сигналы на первом входе триггера 22 (импульсы, приходящие с выхода тактового генератора 16)j б - сигналы на втором входе триггера 22 (с выхода переноса счетчика 25); в - сигналы на выходе триггера 22. Корреляционный измеритель скорости работает следующим образом. Перед началом измерений скорости на пути потока газа или жидкости устанавливают лазер (не показан) для зондирования потока двумя параллельными световыми пучкам с базисным, расстоянием между ни№1 S. Датчики 1 и 2 корреляционного измерителя скорости сориентированы таким образом, чтобы иметь возможность регистрировать факт пересечения световых пучков потоком газа или жидкости. Для удобства регистрации факта пересечения в поток вводят частицы - метки. Оператор задает с помощью таймера 15 задержку и шyльca начала записи сигнум-сигналов относительно начала измерения скорости. В исходном состоянии, когда отсутствует импульс начала измерения, тактовьш генератор 16 включен и третий вход посыпает импульсы на блока 14 управления, т.е. на И 24 и первые входы элемента триггера 22 поступают импульсы 16 (тактотактового г.енератора вые импульсы). На выходе триггера 22 - единичньш сигнал, на выходе элемента И 24 сигнал отсутствует, а следовательно, сигнал отсутствует на выходе элемента И. 23. Сигналы отсутствуют также на вькоде элемента И 5 и на входах и выходах таймера 15, элементов ИЛИ 17, 18, 27 и 28, триггеров 20 и 21, элемента 29 задержки и формирователя 30 импульсов. Состояние входов и выходов осталышх бло ков корреляционного измерителя скорости неопределенно и не имеет значения для дальнейшей работы устройства. Импульс начала измерения поступает на один из входов элемента ИЛИ 17. В случае измерения скорости квазинепрерывного потока пмпульс начала измерения поступает па один из входов элемента ИЛИ 17 с датчика наличия потока.(не показан), который реагирует на появление квазинепрерывного потока и может быть выполнен в виде пьезоэлектрического датчика. В случае измерения скорости непрерывного потока импульс начала измерения на другой вход элемента ШШ 17 в нужный момент времени подает Оператор, например, нажимая кнопку выключателя (не показан), один зажим которого соединен с входом схемы ИЛИ а второй зажим - заземлен. Появившийся импульс начала измерения через элемент ИЛИ 17 поступает на вход таймера 15 и на второй вход блока 14 управления, т.е. на первые входы триггера 21 и элемента ИЛИ 28. Триггер 21 переключается в единичное состояние. Этот же имйульс начала измерения, проходя через элемент ИЛИ 28 на управляющие входы счетчиков 25 и 26,обнуляет их, т.е. на адресных входах блоков 6 и 7 памяти появляются нулевые сигналы, запрещающие запись и считывание. Электрические сигналы x(t) с фото jдатчика 1 и х(с)их(с+Т) с фотодатчик 2, проявляющиеся при пересечении свет вых пучков потоком,поступают соответс венно на входы усилителей-рграничителей 3 и 4, которые преобразуют эти сигналы соответственно в сигнум-сигналы sign x(t) и sign x(t+i). Сигнум сигналы поступают на первые входы блоков 6 и 7 памяти, но не записываются в них, так как на адресных входах блоков 6 и 7 памяти нулевые сигналы. Единичньй сигнал с выхода триггера 21, т.е. с первого выхода блока 14, поступает на вторые входы блоков 6 и 7 памяти и переключает их в режим записи. Одновременно этот сигнал поступает на управляющий вход счетчика 13, обнуляя его, и через элемент ИЛИ 27 - на управляющий вход интегратора 9, обнуляя его. Единичнь сигнал на выходе триггера 21 существует на протяжении всего цикла записи сигнум-сигналов в блоки 6 и 7 памяти . По истечении времени задержки . таймера 15, заданной оператором, с выхода таймера 15 на первый вход блока 14 .управления, т.е. на первый вход триггера 20, поступает импульс, переключающий триггер 20 в единичное состояние. Единичный сигнал с выхода триггера 20 поступает на второй вход элемента И 24, разрешая прохождение импульсов с тактового генератора 16 через элемент И 24 на информационный вход счетчика 26 и на первый вход элемента И 23. На втором входе элемента И 23 уже есть единичньй сигнал с выхода триггера 22, который разрешает прохождение тактовых импульсов через элемент И 23 на информационньй вход счетчика 25. Счетчики 25 и 26 начинают считать тактовые импульсы, поступающие на их входы, при этом на их информационных выходах появляются выраженные в двоичном коде числа 1,2,3,4,5.... Эти числа поступают на адресные входы блоков 6 и 7 памяти и задают номера ячеек блоков 6 и 7 памяти, в которые в данный момент записываются сигнум-сигналы, соответственно в блок 6 памяти - сигнал sign x(t;), а в блок 7 памяти - сигнал sign x(c+t). Числа на выходах счетчиков 25 и 2S сменяют одно другое с частотой тактового генератора 16. Таким образом, на третьем и четвертом выходах блока 14 управления появляются числа, последовательно задающие номера ячеек 6 и 7 памяти, в которые записываются сигнум-сигналы. Числа, выраженные в двоичном коде, с третьего выхода блока 14 управления поступают на адресный вход блока 6 памяти, с четвертого выхода блока 14 - на адресный вход блока 7 памяти. Сигнумсигналы, поступающие на первые входы блоков 6 и 7 памяти, начинают записываться в ячейки блоков 6 и 7 памяти. При переполнении счетчика 25 он самоустанавливается в О, а на его выходе переноса появляется импульс переполнения, которьй определяет конец цикла записи. Этот импульс поступает на вторые входы триггеров 21 и 22, обнуляя их выходы. При этом на управляющих входах блоков 6 и 7 памяти единичный сигнал сменяется нулевым, и блоки 6 и 7 памяти переключаются в режим считывания. Формирователь 30 импульсов по срезу сигнала на выходе триггера 21 формирует импульс, которьй проходит с третьего выхода блока 14 через элемент ИЛИ 18 на управляющие входы регистров 10и 11 и разрешает запись впоследние 10 и 11 чисел в двоичном коде блоков 6 и 7 памяти и соответствует его началу. Нулевой уровень на выходе триггера 22 после обнуления его импульсом переполнения счетчика 25 запрещает прохождение тактовых импульсов на информационный вход счетчика 25, в то время, как на информационный вход счетчика 26 эти импульсы продолжают поступать. Импульс, пришедший с тактового генератора 16 на первый вход триггера 22, переключает его в единичное состояние, разрешая прохождение тактовых импульсов на информационный вход счетчика 25. Вследствие этих переключений триггера 22 число на информационном выходе счетчика 25 будет на две единицы меньше числа на информационном выходе счетчика 26 на протяжении всего второго цикла считывания. Это означает, что сигналы будут считываться одновременно из 1-й ячейки блока 6 памяти и из 3-й ячейки блока 7 памяти, из 2-й ячейки блока 6 памяти и из 4-й ячейки блока 7 памяти, т.е. из п-й ячейки блока 6 памяти и n+2-й ячейки блока 7 памяти Сигналы, считываемые из ячеек блоков 6 и 7 памяти, поступают на входы бло ка 8 умножения, и в случае совпадения состояний входов блока 8 умножения единица с выхода этой схемы поступает на информационньй вход интег ратора 9. Последний накапливает число совпадений в течение второго цикл считывания. Блок 12 сравнения сравни вает числа, поступающие на его входы с интегратора 9 и регистра 10. Счетчик 26 переполняется скорее, чем счетчик 25, самоустанавливается в О и снова начинает считывать с единицы. При переполнении счетчик 25 самоустанавливается в О, и на его выходе переноса появляется импульс переполнения, который поступа ет на второй вход триггера 22 и обнуляет его. Этот же импульс перепол нения с пятого выхода блока 14 упра ления поступает на первый вход элемента И 5, если в этот момент време ни на второй вход схемы И 5 поступа ет единичный сигнал с выхода блока 12 сравнения, то импульс переполне1ШЯ проходит через элементы И 5 и ИЛИ 18 на управляющие входы регистров 10 и11. В регистр 10 при этом записьшается число с выхода индикатора 9, а в регистр 11 - число 2 с второго выхода счетчика 13. Если же в конце второго цикла считывания число на выходе интегратора 9 меньше числа, записанного в регистре 10, на выходе блока 12 сравнения нулевой сигнал. Импульс переполнения не проходит через элемент И 5, и записи в регистры 10 и 11 не происходит, в регистрах 10 и 11 остаются ранее записанные числа. Спустя некоторое время, определяемое задержкой времени . элемента 29 задержки, и fflyльc переполнения появляется на выходе элемента ИЛИ 27, т.е. на втором выходе блока 14 управления. С второго выхода блока 14. управления этот импульс поступает на управляющий вход интегратора 9, обнуляя его, и на информационный вход счетчика 13, записывая в него еще одну единицу. В счетчике 13 будет записано число 3 - номер следующего начинающегося цикла считывания сигнум-сигналов из блоков 6 и 7 памяти. Нулевой уровень на выходе триггера 22 сохраняется до прихода следующего тактового импульса, который переключает триггер 22 в единичное состояние, разрешая тем самым прохождение тактовых импульсов на информационный вход счетчика 25. Вследствие переключений триггера 22 число на информационном выходе счетчика 25 будет на три единицы меньше числа на информационном выходе счетчика 26 на протяжении всего третьего цикла считывания. При этом осуществляется одновременное считывание из 1-й ячейки блока 6 памяти и 4-й ячейки блока 7 памяти, из 2-й ячейки блока 6 памяти и 5-й ячейки блока 7 памяти, т.е. из п-1 ячейки блока 6 памяти и n+3-й ячейки блока 7 памяти. Считываемые сигналы сравниваются в блоке 8 умножения. Интегратор 9 накапливает число совпадений в течение третьего цикла считьтанИя, блок 12 сравнения сравнивает числа, поступающие на его входы с интегратора 9 и регистра 10.При переполнении счетчика 25 импульс переполнения с его выхода переноса обнуляет триггер 22 и поступает на первый вход элемента И 5. Если в этот момент времени на выходе блока 12 сравнения единичньш сигнал, т.е. число на выходе интегратора 9 больше числа, записанного в регистре 10, которые поступают на входы регистров 10 и 11 и в этот момент равны О. На индикатор 19 постоянновыводится число, записанное в регистре 11. Этот же импульс переполнения с вл 1хода переноса счетчика 25 проходит через устройство 29 задержки с ;задержкой времени на второй вход элемента ИЛИ 27. С выхода . с второго выхода следнего. блока 14, задержанный импульс поступает на управляющий вход интегратора 9, повторно обнуляя его, и iia ипформациониьш вход счетчика 13, записывая в него 1, Эта 1 озкачает номер первого цикла считывания сигнум-сигналов из блоков 6 и 7 памяти и соответствует его началу. Счетчик 26 переполняется одновременно со счетчиком 25, самоустанавли вается в О и опять начинает счет с 1. При этом начинается считывани из блока 7 памяти, {улевой уровень на выходе триггера 22 после обнуления его импульсом переполнения счетчика 25 запрещает прохогкдение тактовых импульсов на информацио1П1ый вход счетчика 25, в то время .как на информациоиньш вход счетчика 26 зти импульсы продолжают поступать. Время существования нулевого сигнала на выходе триггера 22 меньше длительности периода частоты тактового генератора 16. Первьй же импульс. приходяицш с тактового генератора 16 на первьш вход триггера 22, переключает его в единичное состояние. Этот единичный сигнал разрешает прохождение тактовых импульсов на вход счетчика 25. Вследствие этих переключени триггера 22 число на информационном выходе счетчика 25 будет на единицу меньше числа на информационном выходе счетчика 26 на протяжении всего первого цикла считывания. Это означа ет, что в течение первого цикла считывания сигнум-сигналов из блоков 6 и 7 памяти сигнум-с11гналы будут считьшаться одновременно из первой ячей ки блока 6 памяти и из второй ячейки блока 7 памяти, из вторрй ячейки блока 6 памяти и из третьей ячейки блока .7 памяти, т.е. из п-ячейки бло ка 6 памяти и (п+1)-й ячейки блока 7 памяти. Сигналы, считанные из ячеек блоков 6 и 7 памяти, поступают на выходы блока 8 умножения. В случае совпадения состояний входов блока 8 умножения посьшает единицу на информационный вход интегратора 9, который накапливает число совпадений в течение первого цикла счит1лвания. В случае несовпадения состояний входов схемы 8 умножения на ее выходе О. С выхода интегратора 9 накопленное число совпадений, выраженное в двоичном коде, поступает на второй вход блока 12 сравнения, которьцЧ сравнивает числа, поступающие в двоичном коде на его входы. В случае, когда число, поступающее па блок 12 сравнения с выхода интегратора 9, больше числа, поступающего с выхода регистра 10, на выходе блока 12 сравнения появляется единичный сигнал. Если число, поступающее на блок 12 сравнения с выхода игггегратора 9, меньше числа, поступающего с выхода регистра 10, на выходе блока 12 - нулевой сипна. Счетчик 26 переполняется скорее, чем счетчик 25, самоустанавлиаается в О и снова начинает считать с единицы. При переполнении с сетчик 25 сггмоустанавливается в О и на его выходе переноса появляется импульс переполнения, которьш определяет конец первого цикла считывания.Этот импульс переполнения поступает на второй вход триггера 22 и обнуляет его. Этот же импульс переполнения с пятого выхода блока 14 управления. т.е. с выхода переноса счетчика 25, поступает на первьш вход элемента И 5, если на второй вход элемента II. 5 в это время поступает единичншЧ сигнал с выхода блока 12 сравнения, то импульс переполнения проходит через элементы И 5 и ИЛИ 18 на управляющие Бходы регистров 10 и 11. В регистр 10 при этом запишется число с выхода интегратора 9, а в регистр 11 - число 1 с второго выхода счетчика 13. Затем этот импульс переполнения, пройдя через элемент 29 задержки и элемент ИЛИ 27, с некоторой задержкой времени появляется на втором выходе блока 14 управления и поступает на управляющий сход интегратора 9 и на информационHbrii вход счетчика 13. При этом интегратор 9 обнуляется, а в счетчик 13 записывается еще одна единица В счетчике 13 теперь записано число 2, что означает номер второго цикла считываниясигнум-сигналов из

то импульс переполнения проходит через элемент И 5 и ИЛИ 18 на управляющие входы регистров 10 и 11. В регистр 10 при этом записывается число с выхода интегратора 9, а в регистр

11- число 3 со второго выхода счетчика 13, Если на выходе блока

12сравнения нулевой сигнал, т.е. число на выходе интегратора 9 меньше числа, записанного в регистре 10, то импульс переполнения не проходит через элемент И 5, и записи в регистры 10 и 11 не происходит, В регистрах 10 и 11 остаются ранее записанные числа. Спустя некоторое время импульс15 на переполнения, задержанный в элементе 29 задержки, описанным образом обнуляет интегратор 9 и записывает в счетчик 13 еще одну единицу. В счетчике 13 будет записано число 4 номер следующего начинающегося цикла считывания сигнум-сигналов из блоков 6 и 7 памяти. Нулевой уровень на выходе тригге.ра 22 сохраняется до прихода следующего тактового импульса, который переключает триггер 22 в единичное состояние, разрешая тем самым прохожде ние тактовых импульсов на информационный вход счетчика 25. Далее четвер тый цикл считывания происходит анало гично описанному. Таким же образом происходит пятый, шестой и все после дующие циклы вплоть до последнего, например сотого,цикла считывания. В сотом цикле считывания осуществляется одновременное считывание из 1-й ячейки блока 6 памяти и 101-й ячейки блока 7 памяти, т.е. из п-й ячейки блока 6 памяти и п+100-й ячей ки блока 7 памяти. Считанные сигналы поступают на входы схемы 8 умножения. Интегратор 9 накапливает число совпадений в течение сотого цикла считывания. По окончании сотого цикла считывания в регистры 10 и 11 записываются числа соответственно с интегратора 9 и со счетчика 13, если в этот момент число на выходе интегратора 9 больше числа,записанного в регистре 10. Если же число на выходе интегратора 9 меньше числа, записанного в регистре 10, записи в регистры 10 и 11 не происходит, в них оста ются ранее записанные числа. Импульс

переполнения счетчика 25 описанным образом обнуляет интегратор 9 и заносит еще одну единицу в счетчике

13. Последний переполняется и с его первого выхода проходит импульс на четвертый вход блока 14 управления, т.е. на второй вход триггера 20 и через элемент 11ЛП 28 на управляющие входы счетчиков 5 и 26. Последние обнуляются, и нулевой сигнал с их информационных выходов поступает на адресные входы блоков 6 и 7 памяти, запрещая считывание и запись.

В ко.нде последнего цикла считывания в регистре 10 записано максимальное число совпадений, считанных из блоков 6 и 7 памяти сигнум-сигналов

генератор 16 включен и посылает импульсы на третий вход блока 14 управления, т.е. на первые входы схемы И . входах схемы 8 умножения, т.е. максимум взаимной корреляционной функции сигнум-сигналов, достигнутый за сто циклов считывания. В регистр 11 при этом записано число т, которое индуцируется в двоичном коде на индикаторе 19 и означает номер цикла считывания, в котором был достигнут максимум совпадений. В т-ом цикле считывания одновременно считывают сигнум-сигналы из п-й ячейки блока 6 памяти и п+га-й ячейки блока 7 памяти. Максимум совпадении сигнум-сигналов достигается при равенстве временного сдвига t при считьшаиии сиг- нум-сигналов из блоков 6 и 7 памяти и времени транспортного запаздывания. С учетом того, что сдвиг на .одну единицу номеров ячеек блоков 6 и 7 памяти соответствует по времени периоду частоты тактового генератора 16, можно определить: I- L m-T. время транспортного запаздывания, с; временной , с; номер цикла считывания, в котором был достигнут максимум совпадений сигнум-сигналов (максимум взаимной корреля :рюнной функции); период частоты тактового генератора 16, с. Найденное время и является временем транспортного запаздывания f , зная которое несложно определить скорость. Цикл вычислений закончен, -устройство в исходном состоянии. Тактовый 24 и триггера 22 поступают тактовые импульсы. На выходе триггера 22 единичньй сигнал, на выходе схемы И 24, а значит и на выходе схемы И 23 сигнал отсутствует. Сигнал отсутствует также и на выходе схемы И 5, па выходах и входах таймера 15, схем ИЛИ 17, 18, 27 и 28, триггеров 20 и 21, устройства 29 задерж ки и формирователя 30 импульсов. Со стояние входов и выходов остальных блоков корреляционного измерителя скорости не имеет значения для даль нейшей работы устройства, Корреляционйый измеритель скорости готов к следующему измерению. Временная диаграмма, поясняющая процесс измерения скорости квазинепрерывного потока, приведена на чер теже фиг. 4, где t время запис - время суси сигнум-сигналов; ществования квазинепрерывного пото.ка; с оз время задержки записи сигнум-сигналов относительно момента появлершя квазинепрерынного потока. Формула изобретения Корреляционньй измеритель скороети, содержащий датчики начала и конца пути, соединенные с входами двух усилителей-ограничителей, элемент 1Ш1, первый регистр, блок умножения интегратор, тактовый генератор и счетчик, отличающийся тем, что, с целью обеспечения возможности измерения скорости квазинепрерывного потока и уменьшения погрешности измерения, в него введены элемент И, два блока памяти, второй регистр, блок сравнения, блок управпения и таймер, при этом выходы усипителей-огранпчителей подсоединены к первым входам блоков памяти, вторые входы которых соединены с управляющим входом счетчика и первым выходом блока управления, первым входом подключенного к выходу таймера, вход которого подсоединен к второму входу блока управления и является входом импульса начала измерения, а выход тактового генератора соединен с третьим входом блока управления, четвертым входом подсоединенного к первому ВЫХОДУ счетчика, информационный вход которого подключен к управляющему входу интегратора и второму выходу блока управления, третий и четвертый выходы блока управления соединены соответственно с адресными входами первого и второго блоков памяти, выходами подключенных к соответствующим входам блока умножения, выход которого соединен с информационным входом интегратора, а пятьй выход блока управления подсоединен к первому входу элемента И, вторым входом соединенного с выходом блока сравнения, первый вход которого подключен к выходу первого регистра, а шестой выход блока управления подсоединен к первому входу элемента ИЛИ, вторым входом соединенного с выходом элемента И, выход элемента ИЛИ подключен к управляющим входам первого и второго регистров, при этом информационньп вход первого регистра подсоединен к выходу интеграторд и второму входу блока дравне ния, информационньй вход второго регистра соединен с вторым выходом счетчика, а выход второго регистра является выходом измерителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель элементов матрицы спектральной плотности мощности двух сигналов | 1989 |

|

SU1661667A2 |

| Устройство контроля цифровых блоков | 1985 |

|

SU1339567A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

| Буферное устройство для передачи данных | 1987 |

|

SU1418725A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1589280A2 |

| Устройство для определения корреляционной функции | 1987 |

|

SU1501086A1 |

| Устройство для контроля | 1985 |

|

SU1295421A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство управления памятью | 1986 |

|

SU1401465A1 |

Изобретение относится к измерительной технике и позволяет обеспечить возможность измерения скорости квазинепрерывного потока и уменьшить погрешность измерения. Измеритель содержит датчики 1, 2 начала и конца пути,усилители-ограничители 3, 4,. схему И 5, блоки 6, 7 памяти, схему 8 умножения, интегратор 9, регистры 10 и 11, блок 12 сравнения, счетчик 13, блок 14 управления, таймер 15, тактовый генератор 16, схемы ИЛИ 17, 18 и индикатор 19. Блок 14 управления содержит триггеры 20-22, схемы И 23 и 24, ИЛИ 27 и 28, устройство 29 задержки и формирователь 30 импульсов. Введение новых элементов и образование новых связей между эле g ментами измерителя позволяет устра- нить зоны неопределенности с пони- /Л женной точностью определения скорое- л ти. 4 ил. . . См ю О) СП Од 00

Фиг. 2

О

Фиг. 3

| Прибор для исследования фрикционных свойств материалов | 1973 |

|

SU466433A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Корреляционный измеритель скорости | 1979 |

|

SU890251A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-10-23—Публикация

1985-03-13—Подача