to

о

4 О

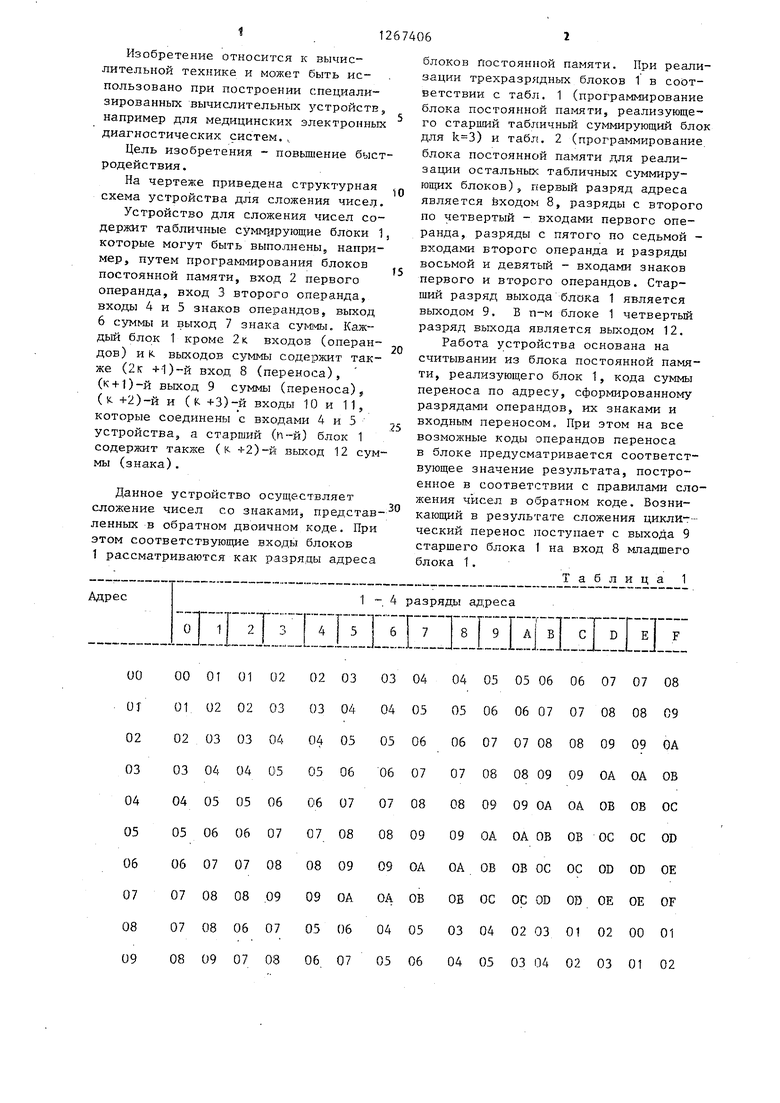

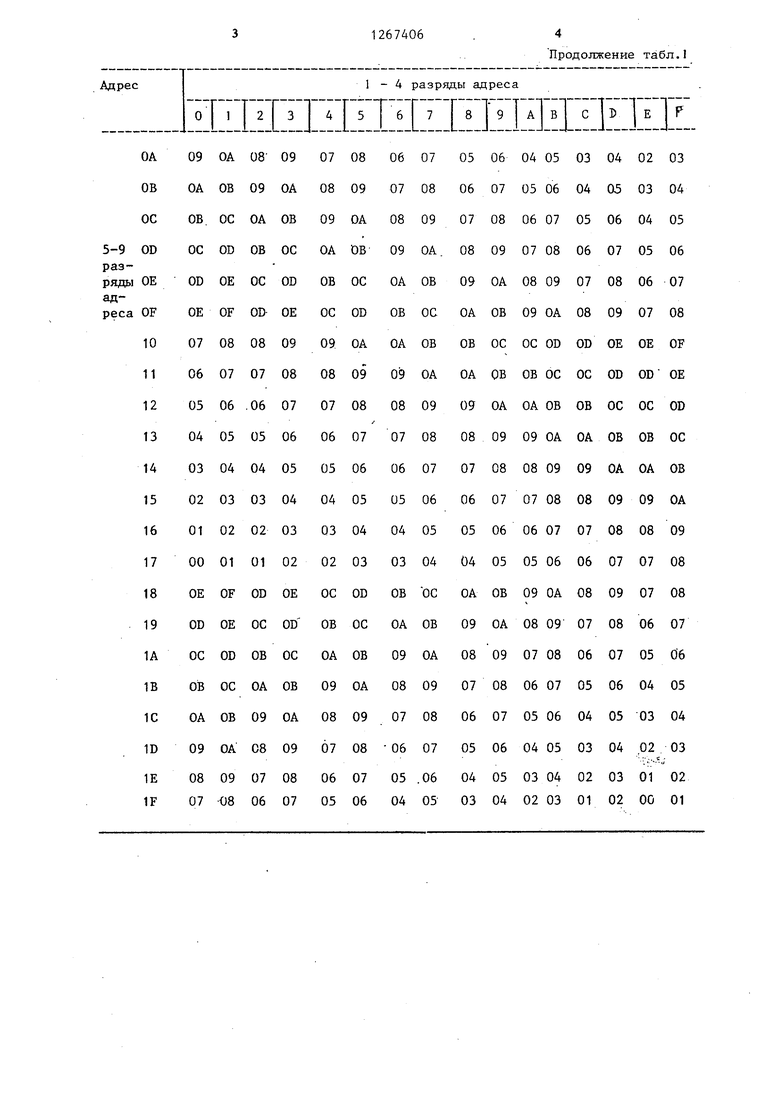

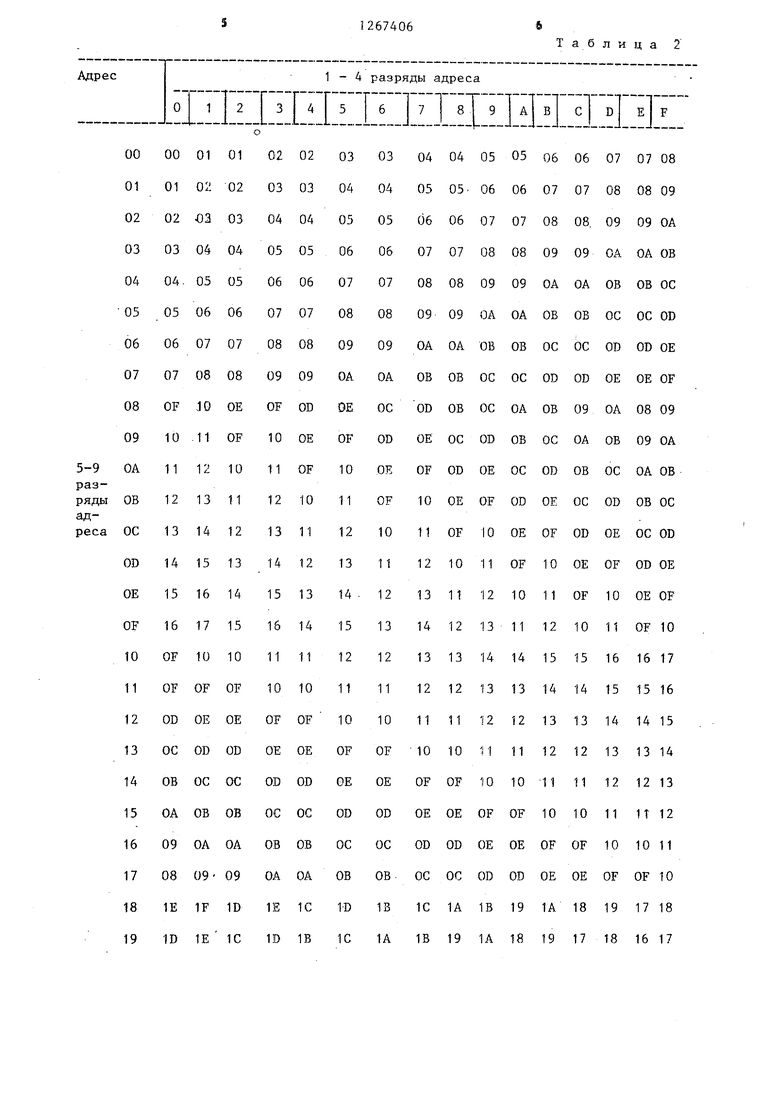

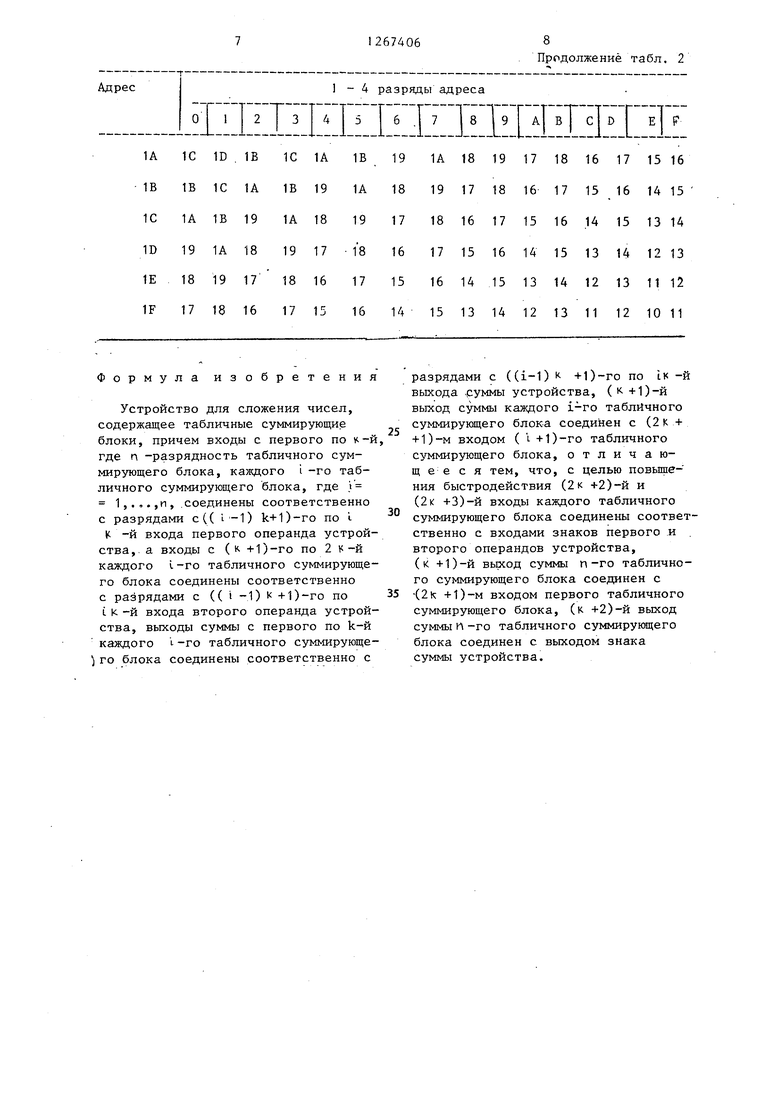

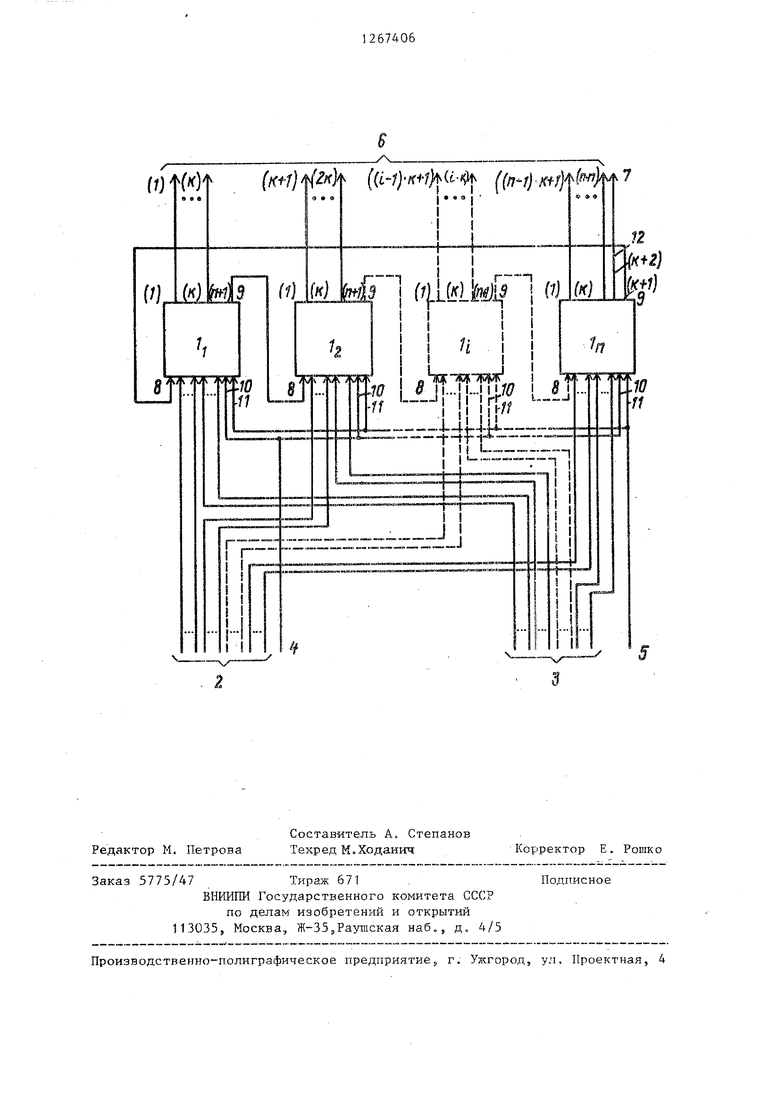

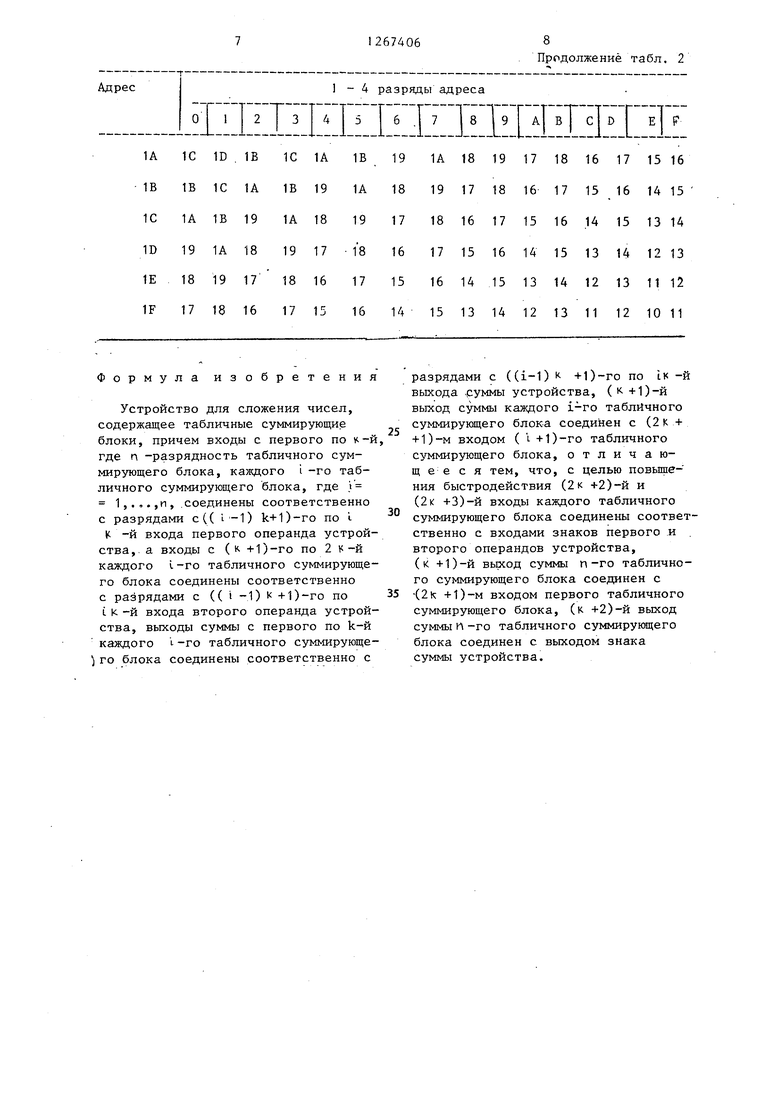

а Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных устройств например для медицинских электронных диагностических систем., Цель изобретения - повьшгение быст родействия. На чертеже приведена структурная схема устройства для сложения чиceJ7 Устройство для сложения чисел содержит табличные суммирующие блоки которые могут быть выполнены, например, путем програмг-шрования блоков постоянной памяти, вход 2 первого операнда, вход 3 второго операнда, входы 4 и 5 знаков операндов, выход 6 суммы и выход 7 знака cyMistbi. Каждый блок 1 кроме 2 к входов (операндов) и к выходов суммы содержит также (2к +1)-й вход 8 (переноса), (к+1)-й выход 9 суммы (переноса)J (к. +2)-й и (К +3)-й входы 10 и 11, которые соединены с входами 4 и 5 устройства, а старший (п-й) блок 1 содержит также (к +2)-и выход 12 сум мы (знака). Данное устройство осуЕ(ествляет сложение чисел со знаками представ ленных в обратном двоичном коде, При этом соответствующие входы блоков 1 рассматриваются как разряды адреса блоков Постоянной памяти. При реализации трехразрядных блоков 1 в соответствии с табл. 1 (программирование блока постоянной памяти, реализующего старший табличный суммирующий блок для ) и табл. 2 (программирование блока постоянной памяти для реализации остальных табличных суммирующих блоков)5 первый разряд адреса является 1зходом 8, разряды с второго по четвертый - входами первого операнда, разряды с пятого по седьмой входами второго операнда и разряды восьмой и девятый входами знаков первого и второго операндов. Старший разряд выхода блока 1 является выходом 9. В п-м блоке 1 четвертый разряд выхода является выходом 12. Работа устройства основана на считывании из блока постоянной памяти, реализующего блок 1, кода суммы переноса по адресу, сформированному разрядами операндов, их знаками и входным переносом. При этом на все возможные коды операндов переноса в блоке предусматривается соответствующее значение результата, построенное в соответствии с правилами сложения чисел в обратном коде. Возникающий в результате сложения цикли-ческий перенос поступает с выхода 9 старшего блока 1 на вход 8 младшего блока 1. Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Многовходовое суммирующее устройство | 1980 |

|

SU898422A1 |

| Система для выполнения команд десятичной арифметики табличным способом | 1981 |

|

SU1027731A1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для сложения @ -разрядных чисел в избыточной системе счисления | 1984 |

|

SU1188731A1 |

| Устройство для умножения | 1984 |

|

SU1176325A1 |

| Устройство адресации памяти | 1988 |

|

SU1674138A1 |

| Устройство для одновременного выполнения операций сложения над множеством чисел | 1975 |

|

SU558276A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ СЕМИ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018930C1 |

Изобретение относится к области вычислительной техники и предназначено для сложения многоразрядных двоичных чисел, представленных в обратном коде. Цель изобретения - повышение быстродействия. Устройство содержит k-разрядные суммирующие блоки, выполненные, например, на базе блоков постоянной памяти и включенные последовательно. На входы этих блоков подаются соотретствутощие операндов и входного переноса. На два дополнительных входа каадого блока памяти подаются знаки входных операндов, а на дополнительном выходе- старшего блока формируется знак суммы. 1 ил, 2 табл.

00010102

02030304

03040405

04050506

05060607

06070708

07080607

08090708

0505 06Об070708

0606 0707080809

0707 08080909ОА

0808 0909ОАОАОБ

0909 ОАОАОБОВОС

ОАОА ОВОВОСОСOD ОВОВ ОСОСODODОЕ ОСОС ODODОЕОЕOF

0402 0301020001

0503 0402030102

Продолжение табл.1

Таблица Формула изобретения Устройство для сложения чисел, содержащее табличные суммирующие блоки, причем входы с первого по к-и где п -разрядность табличного суммирующего блока, каждого i -го табличного суммирующего блока, где t 1,.,.,п, .соединены соответственно с разрядами с(( 1-1) k+1)-ro по i Y- -и входа первого операнда устройства, а входы с ( к. +1)-го по 2 s-и каждого I-го табличного суммирующего блока соединены соответственно с разрядами с (( i -1) к +1)-го по L к-и входа второго операнда устройства, выходы суммы с первого по k-й каждого L-го табличного суммирующе} го блока соединены соответственно с

Продолжение табл. 2 разрядами с ((i-1) к +1)-го по 1к -и выхода -суммы устройства, ( к +1)-й выход суммы каждого i-ro табличного суммирующего блока соединен с (2 к + +1)-м входом ( L +1)-го табличного суммирующего блока, отличающееся тем, что, с целью повышения быстродействия (2 к ч-2)-й и ( +3)-й входы каждого табличного суммирующего блока соединены соответственно с входами знаков первого и второго операндов устройства, (к вьрсод суммы п-го табличного суммирующего блока соединен с (2к +1)-м входом первого табличного суммирующего блока, (к +2)-и выход суммы И-го табличного суммирующего блока соединен с выходом знака суммы устройства. /Ш)АА ((t /J-/ff)t(4f ff -/j/ff/} k) II I i i I I .j.t™.™.-....« I i U™-„...„. I -T-T -U

| Соловьев Г.Н | |||

| Арифметические устройства ЭВМ | |||

| М.: Энергия, 1978, с | |||

| Способ размножения копий рисунков, текста и т.п. | 1921 |

|

SU89A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для вычисления разности двух чисел | 1984 |

|

SU1179320A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-30—Публикация

1984-03-05—Подача