со

СХ) СП Э

Изобретение относится к импульсной технике и может быть использовано, например, при построении хронизаторов цифровых синтезаторов частоты, электромузыкальных инструментов и других приборов.

Цель изобретения - повышение надежности за счет упрощения устройства.

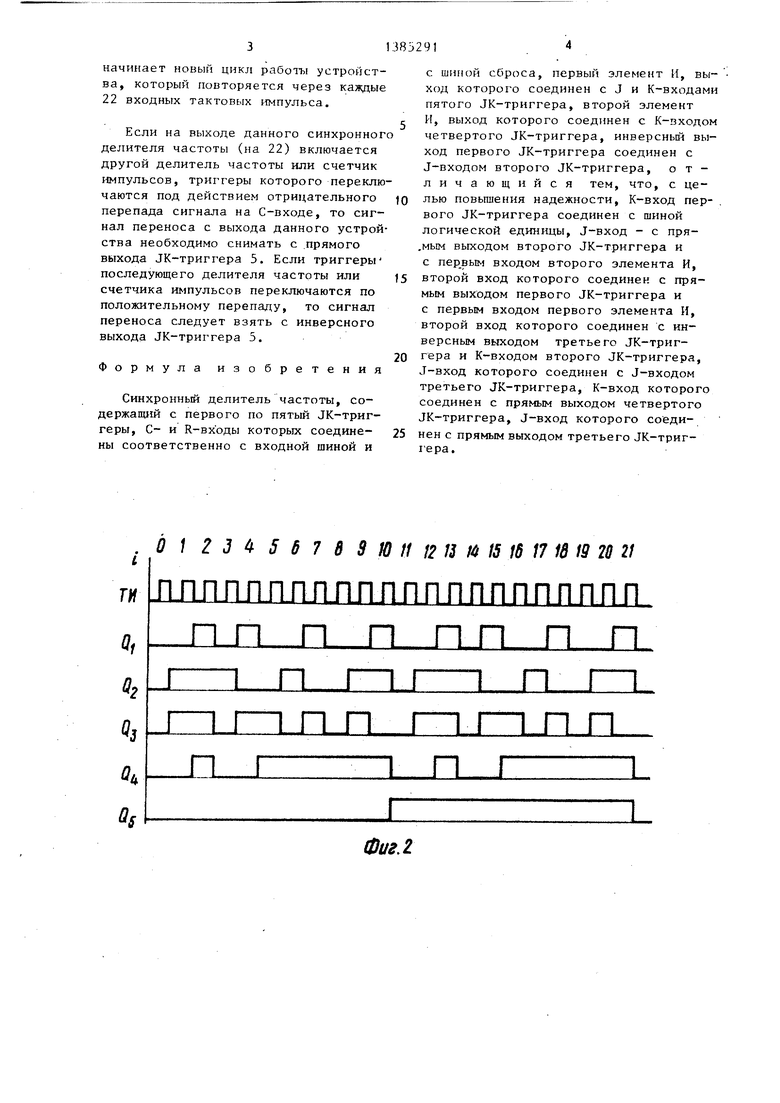

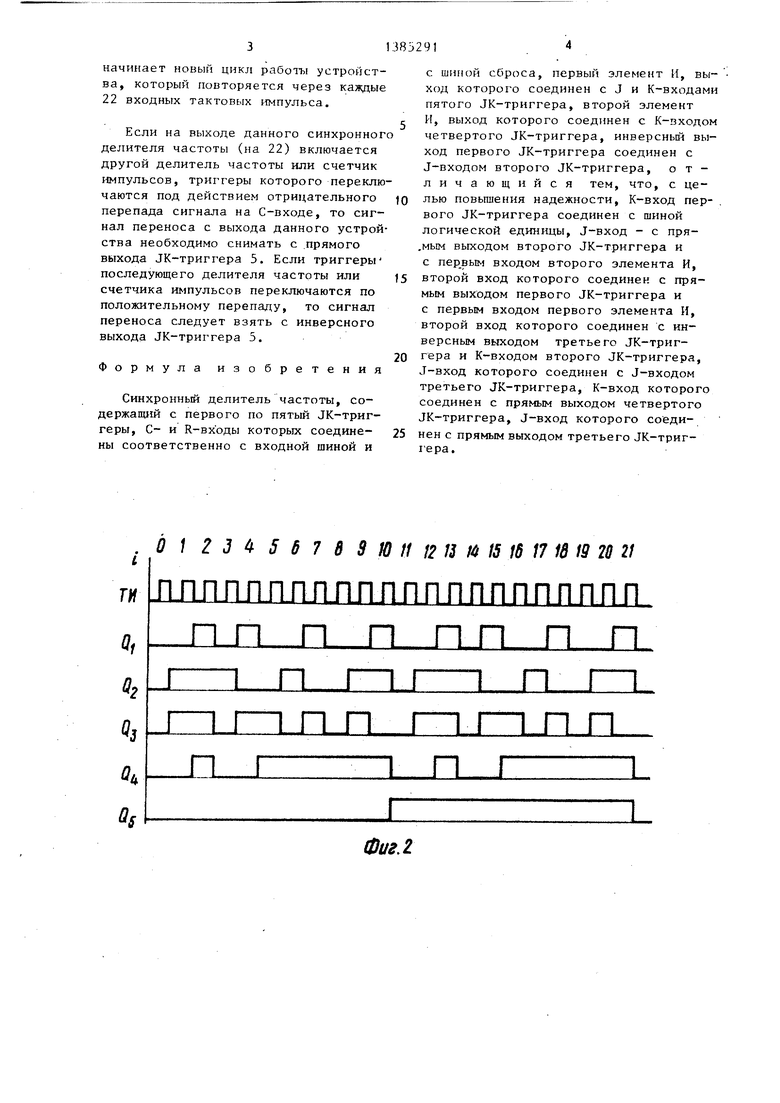

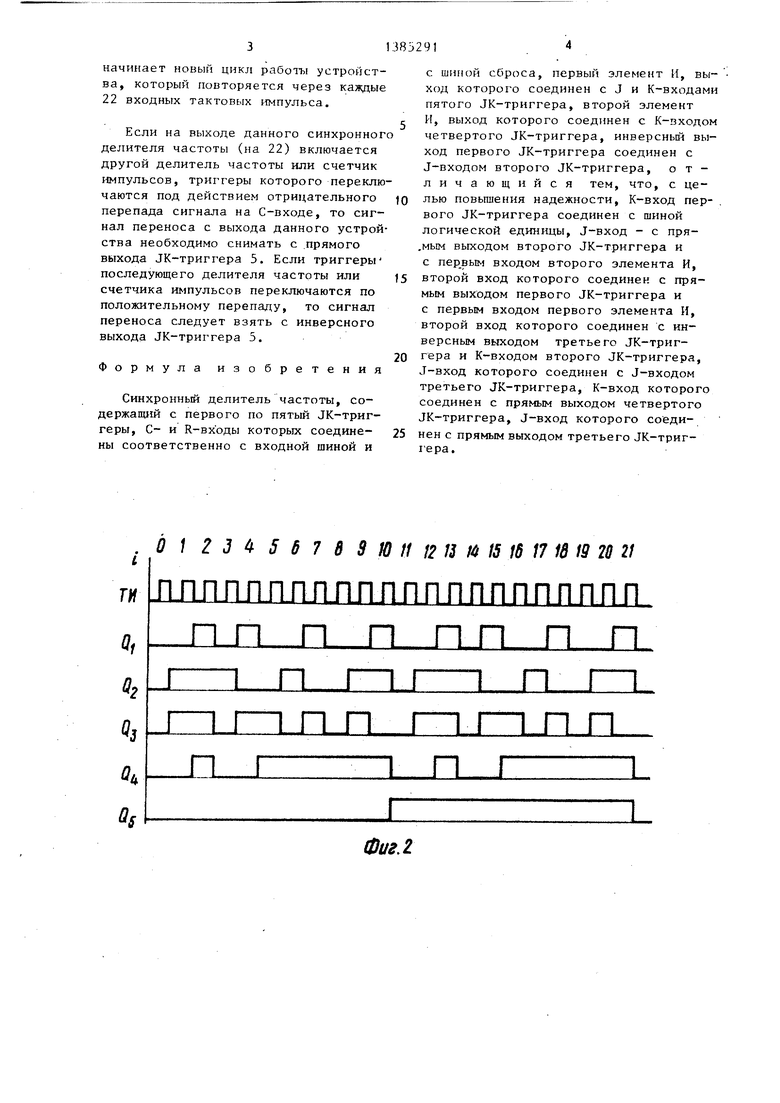

На фиг. 1 приведена электрическая функциональная схема устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Синхронный делитель частоты содержит первый 1, второй 2, третий 3, чет вертый 4 и пятый 5 JK-триггеры, первы 6 и второй 7 элементы И, С- и R-входы JK-триггеров 1-5 соединены соответственно с входной шиной 8 и с шиной 9 сброса, J - вход первого JK-триггера 1 соединен с прямым выходом второго JK-триггера 2 и с первым входом второго элемента И 7, второй вход которого соединен с прямым выходом первого JK- триггера 1 и с первым входом первого элемента И 6, выход которого соединен с J- и К-входами пятого JK-триггера 5, второй вход - с инверсным выходом третьего JK-триггера 3 и с К-входом второго JK-триггера 2, К - вход пер- вого JK-триггера 1 соединен с шиной логической единицы,инверсньш выход - с J-входами второго 2 и третьего 3 JK-триггеров, К-вход JK-триггера 3 соединен с прямым выходом JK-тригге- pa 4, J-вход которого соединен с прямым выходом JK-триггера 3, К - вход - с выходом второго элемента И 7.

При указанном соединении элементов устройства логические уравнения для J- и К-входов всех JK-триггеров следующие: .

,i; J,Q,; J. ; K,,Q,; K,Q,; , ,

где обозначение 1 показывает, что данный вход соединен с шиной логической единицы и на нем всегда присутствует уровень напряжения 1.

Работа синхронного делителя частоты определяется логическими уравне- ниями для J- и К-входов всех его JK-триггеров.

По сигналу Сброс, поступающему в виде импульса по шине 9, все JK- триггеры устройства устанавливаются в исходное нулевое состояние, после чего состояния выходов равны (фиг.2, при ).

Q,0; Q,0; Q Q,0.

Ha основании логических уравнения для J- и К-входов JK-триггеров состояния входов следующие: J, J,Q , 1; J, Q , 1; ,

K,1 1;. , 1; K,q,0; ,Q 0; .

Поскольку любой JK-триггер по последующему входному импульсу на шине 8 при изменяет своего состояния, при и переключается в противоположное состояние, при и переключается в состояние 1, а при и - в состояние О, то по первому входному импульсу на шине 8 JK-триггеры 2 и 3 переключаются в состояние 1, а остальные JK-триггеры 1, 4 и 5 не изменяют своего состояния (фиг. 2, при ). При этом состояния выходов ,следующие:

.

Изменяется и состояние входов:

J, 1; К, 1; J« 1; К,0; J, 1; К ,0; .

В результате по следующему втором входному импульсу на шине 8 устройство переходит во второе состояние (фиг. 2, при ), которое характеризуется следукнцими значениями выходов и входов:

Q, 1;

K, 1; K,0; .

В третьем такте (фиг. 2, при i 3) состояния входов становятся равны

Q,0; Q. .

Рассматривая далее работу предлагаемого синхронного делителя частоты получаем все состояния выходов и входов каждого JK-триггера 1-5 при всех i (фиг. 2).

По двадцать второму тактовому импульсу на шине 8 устройство возвращается в исходное состояние:

Q,0; Q,0; Q,0; Q 0.

При непрерьшном поступлении входных импульсов по шине 8 после этого

начинает новый цикл рабо1Ъ1 устройства, который повторяется через каждые 22 входных тактовых импульса.

Если на выходе данного синхронного делителя частоты (на 22) включается другой делитель частоты или счетчик импульсов, триггеры которого переключаются под действием отрицательного перепада сигнала на С-входе, то сигнал переноса с выхода данного устройства необходимо снимать с .прямого выхода JK-триггера 5. Если триггеры последующего делителя частоты или счетчика импульсов переключаются по положительному перепаду, то сигнал переноса следует взять с инверсного выхода JK-триггера 5.

Формула изобретения

Синхронный делитель частоты, содержащий с первого по пятый JK-триг- геры. С- и R-вхЪды которых соедине- 25 ны соответственно с входной шиной и

g 5

0

5

с сброса, первый элемент И, выход которого соединен с J и К-входами пятого JK-триггера, второй элемент И, выход которого соединен с К-входом четвертого JK-триггера, инверсньй выход первого JK-триггера соединен с J-входом второго JK-триггера, отличающийся тем, что, с целью повышения надежности, К-вход пер- . вого JK-триггера соединен с шиной логической едт1ицы, J-вход - с пря- ,мым выходом второго JK-триггера и с входом второго элемента И, второй вход которого соединен с прямым выходом первого JK-триггера и с первым входом первого элемента И, второй вход которого соединен с инверсным выходом третьего JK-триггера и К-входом второго JK-триггера, J-вход которого соединен с J-входом третьего JK-триггера, К-вход которого соединен с прямым выходом четвертого JK-триггера, J-вход которого соединен с прямым выходом третьего JK-тpИI- гера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на 9 на JK-триггерах | 1987 |

|

SU1444938A1 |

| Синхронный делитель частоты на 11 на @ -триггерах | 1983 |

|

SU1150759A1 |

| Синхронный делитель частоты | 1986 |

|

SU1406787A1 |

| Синхронный делитель на 12 | 1987 |

|

SU1517129A1 |

| Синхронный делитель частоты с четным коэффициентом деления | 1987 |

|

SU1629990A1 |

| Синхронный делитель частоты на 47 | 1990 |

|

SU1714806A1 |

| Синхронный делитель частоты на 21 | 1985 |

|

SU1267613A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396275A1 |

| Синхронный делитель частоты на 14 | 1985 |

|

SU1243130A1 |

| Синхронный делитель частоты | 1986 |

|

SU1429317A1 |

Изобретение относится к импульсной технике и может быть использовано, например, при построении хро- низаторов, цифровых синтезаторов частоты, электромузыкальных инструментов и других приборов. Изобретение позволяет повысить надежность устройства за счет его упрощения, чта достигается предложенной схемой его построения. На чертеже показаны JK-триг- геры 1-5, элементы И 6 и 7, входная шина 8, шина 9 сброса. Работа синхронного делителя частоты определяется логическими уравнениями для J- и К- входов всех JK-триггеров делителя .частоты и поясняется временными диаграммами, которые приводятся в описании изобретения. 2 ил.

I

т

Oi

2

j QU QS

о 2 3 5 6 7 д 3 Ю fn2J3 t tS 16 17 18 19 28 21

JlJin Л П Л ПЛЛЛ Л П П П ГУТПЛЛЛ ПЛ

п п п п п п п п

1 П I П П I I

1 п п ГП I-I ТТЛ

П-С

т n.j

т n.j

| Делитель частоты на 19 | 1984 |

|

SU1226660A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Синхронный делитель частоты | 1986 |

|

SU1322470A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-30—Публикация

1986-10-15—Подача