F

со 4

00 00

со

00

Vui.t

тг

1

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении специализированных вычислителей, цифровых устройств для обработки сигналов, .гибридных преобразователей и информационно-измерительных систем ,при цифровой нелинейной обработке звуковых и видеосигналов в устройствах реального времени, а также для повышения производительности микропроцессорных систем.

Цель изобретения - уменьшение объема памяти.

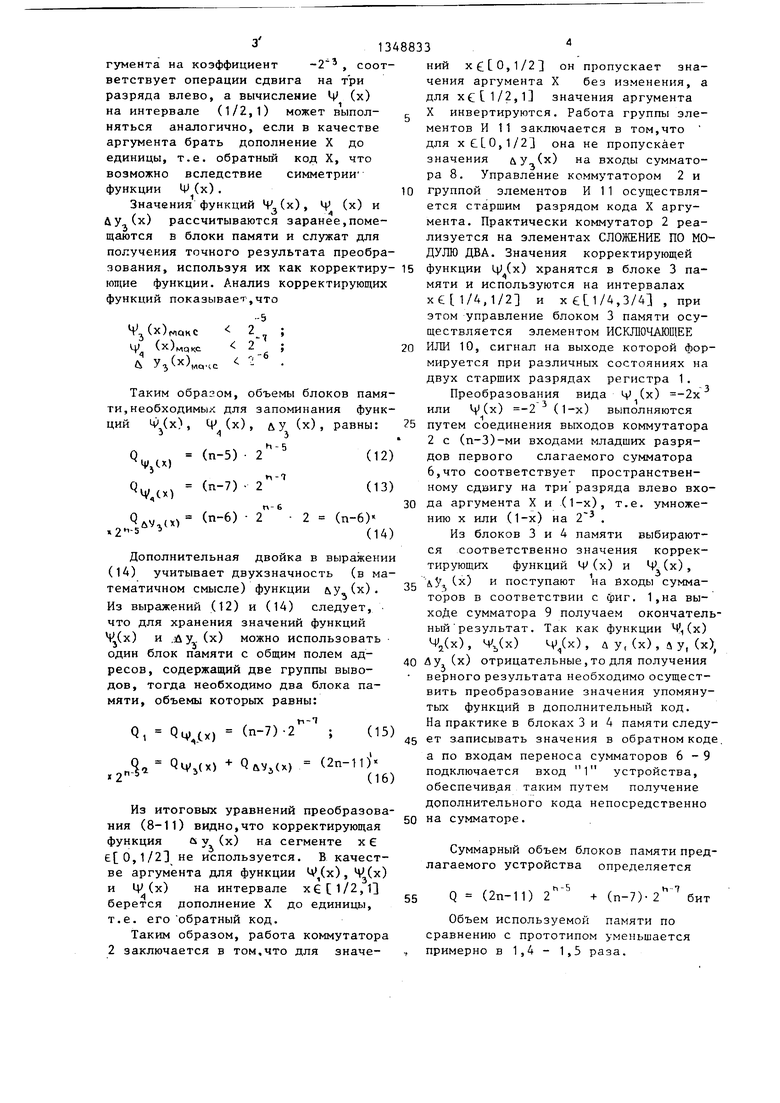

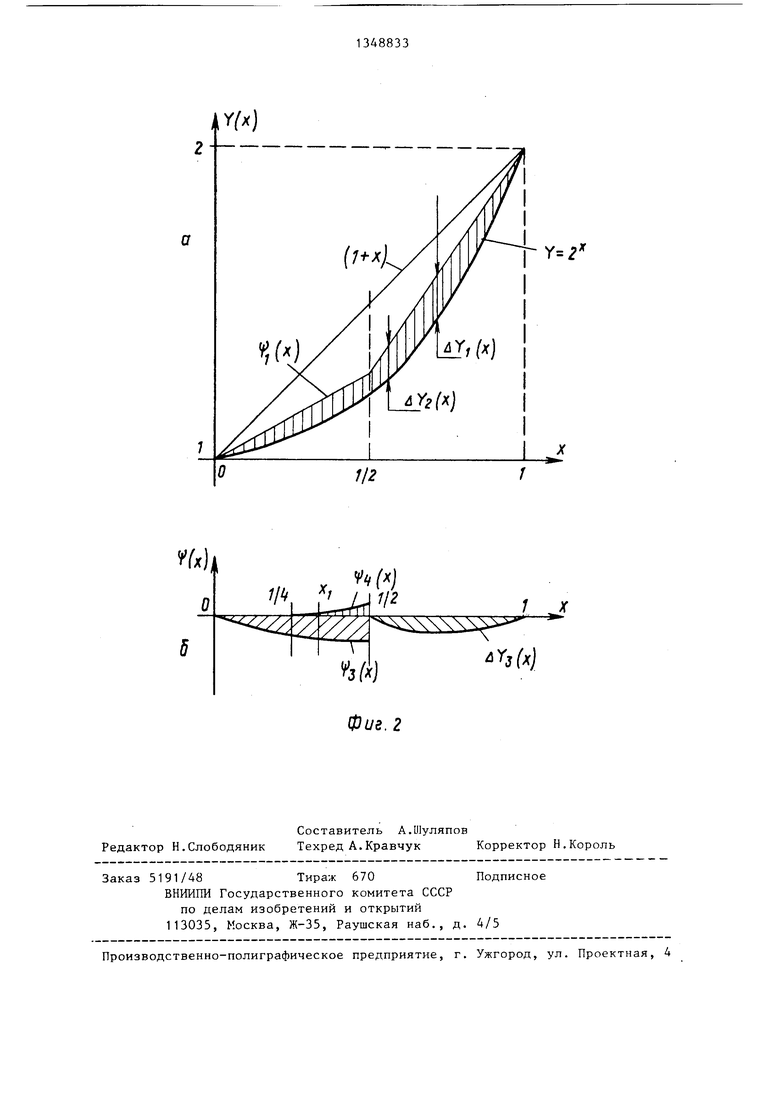

На фиг. 1 приведена структурная схема устройства для потенцирования на фиг. 2 - эпюры, поясняющие принцип преобразования.

Устройство для потенцирования (фиг. 1) содержит регистр 1, коммутатор 2, первый 3 и второй 4 блоки памяти, блок 5 элементов НЕ, первый 6, второй 7, четвертый 8 и третий 9 сумматоры элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, группу элементов И 11, входы 12 и 13 О и 1 соответственно.

Работа устройства для потенцирования основана- на кусочно-линейной аппроксимации функции у 2, где ,1j с последующей коррекцией разности между исходной функцией и ее линейным приближением.

На фиг. 2а показана аппроксимация функции у 2 , ,1 прямой линии. Входной код X содержит часть информации о выходной величине у и может быт использован как грубое приближение исходной функции.На фиг, 2а показана также разность между исходной функцией и ее линейным приближением

лу (х) 2 - (x-t-1) (1) анализ которой показывает,что

-

лу (х)1иацс 2 . (2)

Функция Ц (х) является кусочно- линейной аппроксимацией функции разхе 0,1/2 х 1/2,П(3)

т.е. функция Ч (х) симметрична относительно оси, проведенной через точку X 1 /2.

0

и

Разность между функциями ду (х) и Ф(х) равна

йу(х) Лу(х) - V,(x) (4)

и показана на фиг. 2а.

Можно построить функцию ф(х),которая на интервале х 1/2,1 будет являться симметричным отображением функции U у (х) для значений х g. 0,1/2 относительно оси,проведенной через Точку х 1/2,и совпадать с функцией лу (х) на интервале хе

5 ,1/2.

Разность между функциями ду (х) и Н (х) равна

Л уЛх) y (х) - Ч) (х)

(5)

20

и показана на фиг. 26.

Построим функцию Ц)(х),х (0,1/2) (фиг. 2б) таким образом,чтобы

V(x)

Ф/х) K(X)

x€LO,x

, (6)

фиг

значение аргумента х, при котором функция -(х) принимает максимальное значение V.

. 26 показана функция раз

V(x) 1

Ч(х) - V,(x), хеС i/4i

(7)

которую необходимо учитывать при определении V (х) .

Запишем итоговые уравнения преобразования:

у(х) ()+ VV (х)+ Ч(х) при х еСО,1/4 ; (8)

у(х) (х+1)+ iV(x)+ Ч(х)(х) , 1/2 (9).

у(х) (х+1)+ ф,(1-х)+ Vj(1-x)- V,(1- х)+ Луз(х) при ,(10)

55

у(х)(х+1)+ Ц)/1-х)+ Ч(1-х) +

при XLt3/4,1 ;(11)1

+лу(х)

Вычисление 0,1/2, т.е.

Ц,(х) на интервале умножение кода X аргумента на коэффициент -2 , соответствует операции сдвига на три разряда влево, а вычисление Ц (х) на интервале (1/2,1) может выпол- мяться аналогично, если в качестве аргумента брать дополнение X до единицы, т.е. обратньш код X, что возможно вследствие симметрии функции Ф(х).

Значения функций Ч (х), Ч (х) и йу (х) рассчитываются заранее,помещаются в блоки памяти и служат для получения точного результата преобразования, используя их как корректиру- 15 функции ф(х) хранятся в блоке 3 па- функции. Анализ корректирующих

ющие

функций показывает,что

УЛх)с,кс г

3

.

&

MQKC

(х)

УЗ (лачс

2

1

-7

мяти и используются на интервалах .1/2 и ,3/4 , при этом управление блоком 3 памяти осуществляется элементом ИСКЛЮЧАЮЩЕЕ

20 ИЛИ 10, сигнал на выходе которой фор мируется при различных состояниях на двух старщих разрядах регистра 1.

Таким обра: ом, объемы блоков памяти, необходимых для запоминания функии

LVj(x) ,

Ч ) -1

(п-5) 2

ДУ (х) , и-5

равны:

(12 (13

п-т

rv- 6

2 (п-6)«

Дополнительная двойка в выражении (14) учитывает двухзначность (в ма- тематичном смысле) функции лу (х). Из выражений (12) и (14) следует, что для хранения значений функций V(x) и .ду. (х) можно использовать один блок памяти с общим полем адресов, содержащий две группы выводов, тогда необходимо два блока памяти, объемы которых равны:

tn-T

«2

QI QM .CX) (п-7)-2

Л- з(Х) - QuVjCx)

(15)

1

(2п-11)«

(16)

Из итоговых уравнений преобразования (8-11) видно,что корректирующая функция а у (х) на сегменте х ,1/2l не используется. В качестве аргумента для функции V/x) , ) и IV (х) на интервале ,13 берется дополнение X до единицы, т.е. его обратный код.

Таким образом, работа коммутатора 2 заключается в том,что для значений ,1/2 он пропускает значения аргумента X без изменения, а для хс 1/2,1 значения аргумента X инвертируются. Работа группы зле- ментов И 11 заключается в том,что для X 0,1/21 она не пропускает значения у (х) на входы сумматора 8. Управление коммутатором 2 и группой элементов И 11 осуществляется старшим разрядом кода X аргумента. Практически коммутатор 2 реализуется на элементах СЛОЖЕНИЕ ПО МОДУЛЮ ДВА. Значения корректирующей

15 функции ф(х) хранятся в блоке 3 па-

мяти и используются на интервалах .1/2 и ,3/4 , при этом управление блоком 3 памяти осуществляется элементом ИСКЛЮЧАЮЩЕЕ

20 ИЛИ 10, сигнал на выходе которой формируется при различных состояниях на двух старщих разрядах регистра 1.

Преобразования вида Ц) (х) -2х или V(х) -2 (1-х) выполняются

5 путем соединения выходов коммутатора 2 с (п-З)-ми входами младших разрядов первого слагаемого сумматора 6,что соответствует пространственному сдвигу на три разряда влево вхо30 да аргумента X и (1-х), т.е. умножению X или (1-х) на 2 .

Из блоков 3 и 4 памяти выбираются соответственно значения корректирующих функций Ф (х) и Ч -(х),

35 &У ) и поступают на Входы сумматоров в соответствии с фиг. 1,на выходе сумматора 9 получаем окончательный результат. Так как функции (х) %(х), %(х) ), U у, (х), ay, (х),

отрицательные,то для получения верного результата необходимо осуществить преобразование значения упомянутых функций в дополнительный код. На практике в блоках 3 и 4 памяти следует записывать значения в обратном коде, а по входам переноса сумматоров 6-9 подключается вход 1 устройства, обеспечивая таким путем получение дополнительного кода непосредственно

50 на сумматоре.

40 Лу (х)

45

Суммарный объем блоков памяти предлагаемого устройства определяется

Q (2п-11) 2

п-5

(п-7)

h-7

2 бит

Объем используемой памяти по сравнению с прототипом уменьшается примерно в 1,4 - 1,5 раза.

Формула изобретения

Устройство для потенцирования, содержащее регистр, первый и второй блоки памяти, коммутатор, первый,второй и третий сумматоры, блок элементов НЕ, причем вход аргумента устройства соединен с информационным входом регистра, выходы с третьего по (п-1)-й разрядов которого соединены с информационными входами коммутатора (где п - разрядность регистра), выход старшего разряда регистра подключен к управляющему входу коммутатора,выходы которого поразрядно соединены с входами блока элементов НЕ, выходы которого соединены с входами с первого по (п-З)-й разрядов первого слагаемого первого сумматора,входы второго слагаемого которого поразрядно соединены с выходами регистра, входы переносов первого,второго и третьего сумматоров подключены к входу логической единицы устройства, вход логического нуля которого подключен к входам трех старших разрядов первого слагаемого первого сумматора и к входам двух старших разрядов второго слагаемого второго сумматора, выходы первого сумматора поразрядно соединены с входами второго слагаемого третьего сумматора,выход которого является выходом результата устройства,выходы коммутатора, кроме младшего разряда, соединены с адресными входами второго блока памяти, первая группа выходов которого соединена с входами

0

5

0

первого слагаемого второго сумматора, отличающееся тем, что,с целью уменьшения объема памяти, в него введены четвертый сумматор, группа элементов И и элемент ИС- КЛЮЧАЩЕЕ ИЛИ, причем выходы первого блока памяти соединены с входами с первого по (п-б)-й разрядов второго слагаемого второго сумматора,вторая группа выходов второго блока памяти соединена с информационными входами группы элементов И, выходы которой подклк)- чены к входам с первого по (п-5)-й разрядов первого слагаемого четвертого сумматора,входы второго слагаемого которого поразрядно соединены с выходами второго сумматора, выходы четвертого сумматора соединены с вхо- дам11 с первого по (п-4)-й разрядов первого слагаемого третьего сумматора, выходы р четвертого по (п-2)-й разрядов коммутатора подключены к адресным входам первого блока памяти, 5 управляющий вход которого подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого подключены соответственно к выходам п-го и (n-l)-ro разрядов регистра, управляющие входы группы элементов И соединены с выходом старшего разряда регистра, вход переноса четвертого сумматора подключен к входу логической единицы устройства, вход логического нуля которого подключен к входу старшего разряда первого ела-, гаемого четвертого сумматора и к входам четырех старших разрядов первого слагаемого третьего сумматора.

0

5

2

112

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции двоичной экспоненты | 1985 |

|

SU1305675A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Логарифмический преобразователь | 1984 |

|

SU1196860A1 |

| Логарифмический преобразователь | 1985 |

|

SU1269126A1 |

| Квадратор | 1986 |

|

SU1405053A1 |

| Устройство для вычисления функции двоичной экспоненты | 1984 |

|

SU1238066A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1001092A1 |

| Логарифмический преобразователь | 1981 |

|

SU959073A1 |

| Логарифмический преобразователь | 1986 |

|

SU1401457A1 |

| Преобразователь логарифмического кода в двоичный код | 1990 |

|

SU1716506A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислителей, цифровых устройств для обработки сигналов. Цель изобретения - уменьшение объема- памяти. В состав устройства входят регистр 1, коммутатор 2, первый и второй блоки памяти 3-4, блок элементов НЕ 5, первый,второй,третий и четвертый сумматоры 6-9, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, группа элементов И 11. В данном устройстве уменьшение объема памяти достигается за счет введения сумматора, группы элементов И, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и оригинальных связей. 2 ил. i (Л

W

,у Ч М

I/If f

1 X

jW

Составитель А.Шуляпов Редактор Н.Слободяник Техред А.Кравчук Корректор Н,Король

Заказ 5191/48Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Циделко В.Д., Хохлов Ю.В | |||

| К вопросу построения вычислительных устройств логарифмирования и потенцирования | |||

| - Управляющие системы и машины, 1981, 5, с | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления функции двоичной экспоненты | 1985 |

|

SU1305675A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-30—Публикация

1986-06-27—Подача