4

ел ч|

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический преобразователь | 1984 |

|

SU1196860A1 |

| Устройство для потенцирования | 1986 |

|

SU1348833A1 |

| Квадратор | 1986 |

|

SU1405053A1 |

| Устройство для вычисления функции двоичной экспоненты | 1985 |

|

SU1305675A1 |

| Квадратор | 1986 |

|

SU1325469A1 |

| Логарифмический преобразователь | 1981 |

|

SU959073A1 |

| Логарифмический преобразователь | 1985 |

|

SU1269126A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1361547A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU742947A1 |

| Устройство для вычисления функции двоичной экспоненты | 1984 |

|

SU1238066A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении гибридных функциональных преобразователей,цифровых фильтров и информационно-измерительных систем. Цель изобретения - уменьшение объема памяти. Логарифми- . ческий преобразователь содержит регистр 1, коммутатор 2, первый 3, третий 4 и второй 5 сумматоры, блок памяти 6 и группу элементов И 7. В данном преобразователе уменьшение объема памяти достигается за счет ввода сум- матора, группы элементов И и оригинальных связей. 2 ил. (Л с

Y tef,(M}

9ta.t

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении гибридных функциональных, преобразователей, цифровых фильтров и информационно- измерительных систем.

Цель изобретения - уменьшение объема памяти.

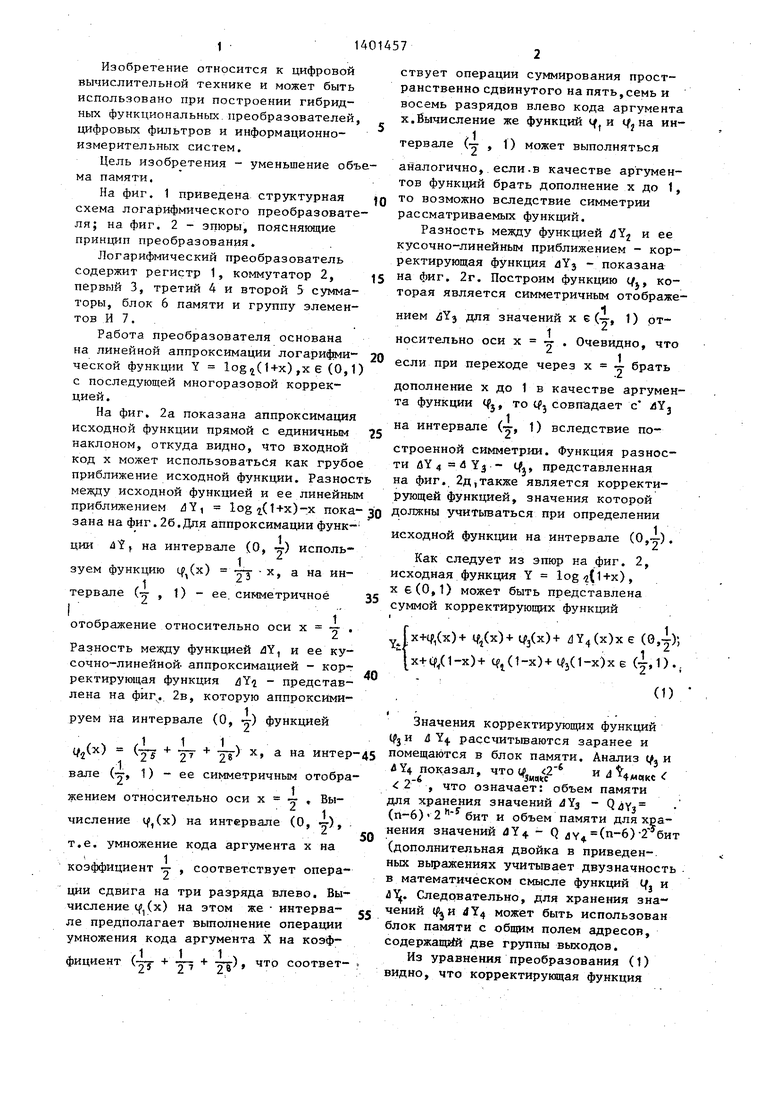

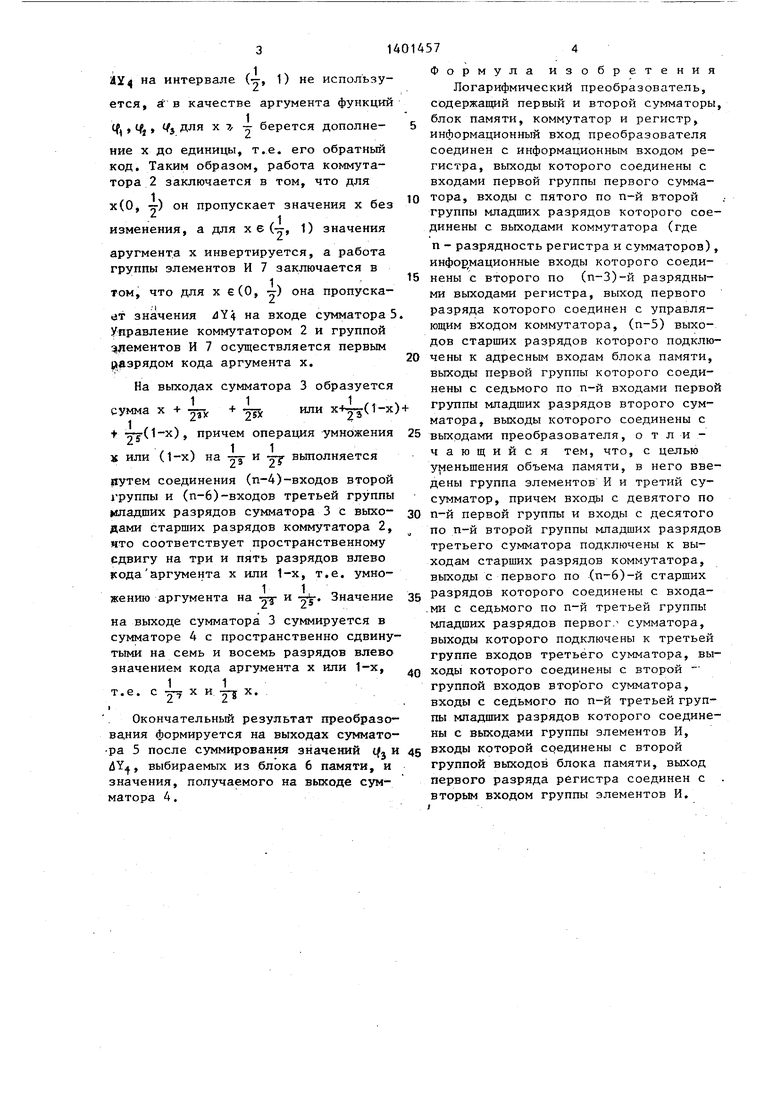

На фиг. 1 приведена структурная схема логарифмического преобразователя; на фиг. 2 - эпюры, поясняющие принцип преобразования.

Логарифмический преобразователь содержит регистр 1, коммутатор 2, первый 3, третий 4 и второй 5 сумматоры, блок 6 памяти и группу элементов И 7.

Работа преобразователя основана на линейной аппроксимации логарифмической функции Y logjCl+x),х е (О,1) с последующей многоразовой коррекцией .

На фиг. 2а показана аппроксимация исходной функции прямой с единичным наклоном, откуда видно, что входной код X может использоваться как грубое приближение исходной функции. Разност между исходной функцией и ее линейным

приближением ilY, logi(Hx)-x пока-зо Должны учитываться при определении

зана на фиг.2б.Дпя аппроксимации функции dtf на интервале (О, ) испольисходной функ1щи на интервале (0,у)

Как следует из эпюр на фиг. 2, исходная функция Y log/2(1+х), X 6(0,1) может быть представлена суммой корректирующих функций

tf,(x) 2 X, а на ин- 1) - ее. симметричное

отображение относительно оси

1 X - J

Разность между функцией /aY, и ее кусочно-линейной, аппроксимацией - корректирующая функция dYi - представлена на фиг. 2в, которую аппроксимируем на интервале (О, ) функцией

40

x+qi,(x)+ ) )+ dY4(x)x е (б,-2); x+tf/1-x)+ Cfj(1-x)(1-х)х 6 ()

(1)

2

(х) с

.1

JL

25

1

2

-L

28

) X,

Значения корректирующий функций (fj и Л Y рассчитьгоаются заранее и а на интер-45 помещаются в блок памяти. Анализ и

А V. Tij-sT/- f fif4-rr t-rm f IЛ x -r л Vf

вале (, 1) - ее симметричным отобра1

жением относительно оси х -TJ- , Вы1числение v,(x) на интервале (О, -д-),

Y4 показал, что tf. 2 , что означает:

и j1f4

JHCIW 4МС|КС

объем памяти

для хранения значений JYj - QjVi

т.е.

2 на

50

умножение кода аргумента х

1

коэффициент , соответствует операции сдвига на три разряда влево. Вычисление If, (х) на этом же интерва- « ле предполагает выполнение операции умножения кода аргумента X на коэффициент (- - Т7 оТ соответ- ь

VIT

2в

и с 3

(.П-ь; « бит и объем памяти для хранения значений dY4 - Q ау(п-6}-2 бит (дополнительная двойка в приведен-, ных выражениях учитьюает двузначность в математическом смысле функций tfj и й. Следовательно, для хранения зна чений 4Y4 может быть использован блок памяти с общим полем адресов, содержащими две группы выходов.

Из уравнения преобразования (1) видно, что корректирукяцая функция

ствует операции суммирования пространственно сдвинутого на пять,семь и восемь разрядов влево кода аргумента X.Вычисление же функций / и t/j на ин/1 1Л

тервале (- t ) может выполняться

аналогично,.если.в качестве аргументов функций брать дополнение х до 1, то возможно вследствие симметрии рассматриваемых функций.

Разность между функцией Y и ее кусочно-линейньм приближением - корректирующая функция 4 YS -показана на фиг. 2г. Построим функцию t/., которая является симметричным отображением 5Y3 для значений х е (у, 1) рт1носительно оси х -я- Очевидно, что

1

если при переходе через х -я- брать

дополнение х до t в качестве аргумента функции cfj, то tfj совпадает с /lYj

/1 ч

на интервале (, 1) вследствие построенной симметрии. Функция разности - f, представленная на фиг. 2д,также является корректирующей функцией, значения которой

исходной функ1щи на интервале (0,у).

Как следует из эпюр на фиг. 2, исходная функция Y log/2(1+х), X 6(0,1) может быть представлена суммой корректирующих функций

I.

x+qi,(x)+ ) )+ dY4(x)x е (б,-2); x+tf/1-x)+ Cfj(1-x)(1-х)х 6 ()(

(1)

Значения корректирующий функций (fj и Л Y рассчитьгоаются заранее и помещаются в блок памяти. Анализ и

А V. Tij-sT/- f fif4-rr t-rm f IЛ x -r л Vf

Y4 показал, что tf. 2 , что означает:

и j1f4

JHCIW 4МС|КС

объем памяти

для хранения значений JYj - QjVi

и с 3

(.П-ь; « бит и объем памяти для хранения значений dY4 - Q ау(п-6}-2 бит (дополнительная двойка в приведен-, ных выражениях учитьюает двузначность в математическом смысле функций tfj и й. Следовательно, для хранения зна чений 4Y4 может быть использован блок памяти с общим полем адресов, содержащими две группы выходов.

Из уравнения преобразования (1) видно, что корректирукяцая функция

ДУ на интервале С-, 1) не используется, а в качестве аргумента функций Cf, cfj, tfj для X 7/ - берется дополнение X до единицы, т.е. его обратный код. Таким образом, работа коммутатора 2 заключается в том, что для

х(0, ) он пропускает значения х без

/

изменения, а для х 6(у, 1) значения

аругмента х инвертируется, а работа группы элементов И 7 заключается в

том, что для X 6(0, у) она пропускает значения Y4 на входе сумматора 5 Управление коммутатором 2 и группой элементов И 7 осуществляется первым разрядом кода аргумента х.

На выходах сумматора 3 образуется

1 11

сумма X + jj-y. + t yj-(l-x), причем операция умньжения 25 X или

или x-bj5 () +

...11

(1-х) на у|- и -jj вьтолняется

путем соединения (п-4)-входов второй группы и (п-6)-входов третьей группы нпадших разрядов сумматора 3 с выходами старших разрядов коммутатора 2, НТО соответствует пространственному сдвигу на три и пять разрядов влево |сода аргумента х или 1-х, т.е. умножению аргумента на -j и у. Значение

на выходе сумматора 3 суммируется в сумматоре 4 с пространственно сдвинутыми на семь и восемь разрядов влево значением кода аргумента х или 1-х, 1 1

т.е.

с у и 2

Окончательный результат преобразования формируется на выходах суммато- ра 5 после суммирования значений ц и (lY, выбираемых из блока 6 памяти, и значения, получаемого на выходе сумматора 4.

0

5

0

5

0

0

5

Формула изобретения

Логарифмический преобразователь, содержащий первый и второй сумматоры, блок памяти, коммутатор и регистр, информационный вход преобразователя соединен с информационным входом регистра, выходы которого соединены с входами первой группы первого сумматора, входы с пятого по п-й второй группы младших разрядов которого соединены с выходами коммутатора (где

п - разрядность регистра и сумматоров), информационные входы которого соединены с второго по (п-З)-й разрядными выходами регистра, выход первого разряда которого соединен с управляющим входом коммутатора, (п-5) выходов старших разрядов которого подключены к адресным входам блока памяти, выходы первой группы которого соединены с седьмого по п-й входами первой группы младших разрядов второго сумматора, выходы которого соединены с выходами преобразователя, о т л и - чающийся тем, что, с целью уменьшения объема памяти, в него введены группа элементов И и третий су- сумматор, причем входы с девятого по п-й первой группы и входы с десятого по п-й второй группы младших разрядов третьего сумматора подключены к выходам старших разрядов коммутатора, выходы с первого по (п-6)-и старших разрядов которого соединены с входа- .ми с седьмого по п-и третьей группы младших разрядов первог. сумматора, выходы которого подключены к третьей группе входов третьего сумматора, выходы которого соединены с второй группой входов второго сумматора, входы с седьмого по п-й третьей группы младших разрядов которого соединены с выходами группы элементов И, входы которой срединены с второй группой вьгходрв блока памяти, выход первого разряда регистра соединен с вторым входом группы элементов И.

а

i;,V, ,

iy,,vv Г-L

7 X

| Цифровой логарифмический преобразователь | 1979 |

|

SU881741A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № | |||

| Логарифмический преобразователь | 1984 |

|

SU1196860A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| /. | |||

Авторы

Даты

1988-06-07—Публикация

1986-12-08—Подача