Изобретение относится к цифровой вычислительной технике и может быть использовано при построении специализированных вычислителей, информационно-измерительных систем, цифровы устройств для обработки сигналов и гибридных функциональных преобразователей.

Цель изобретения - сокращение суммарного объема памяти.

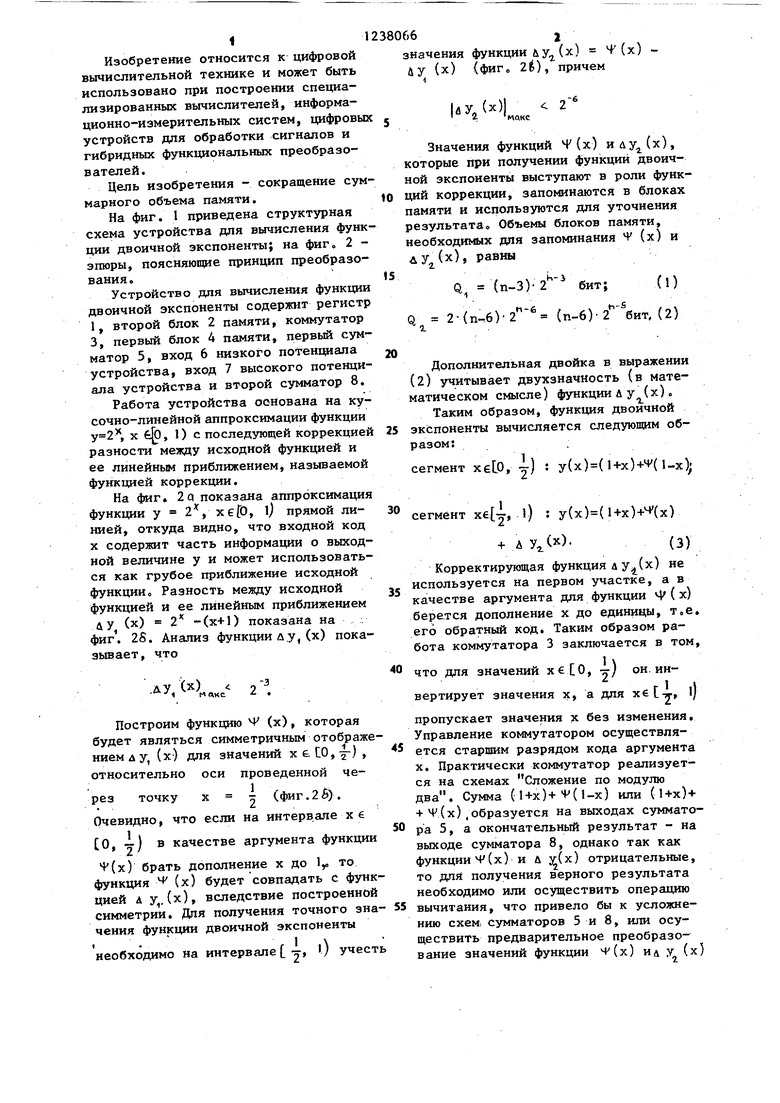

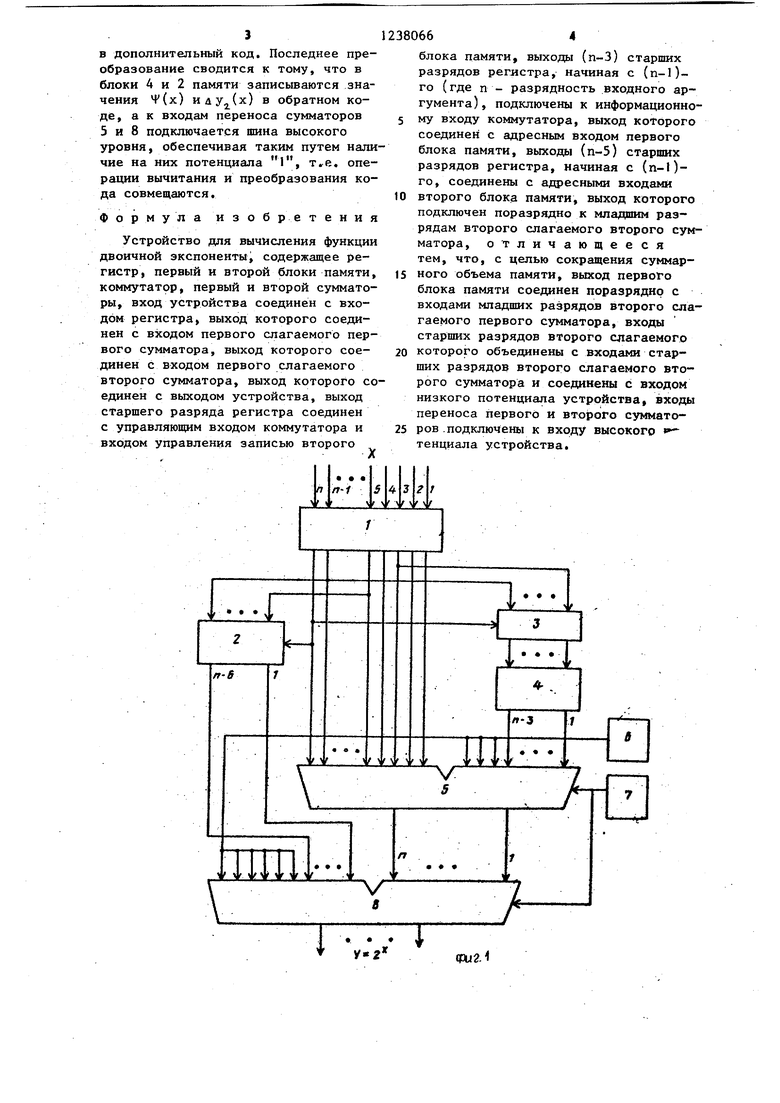

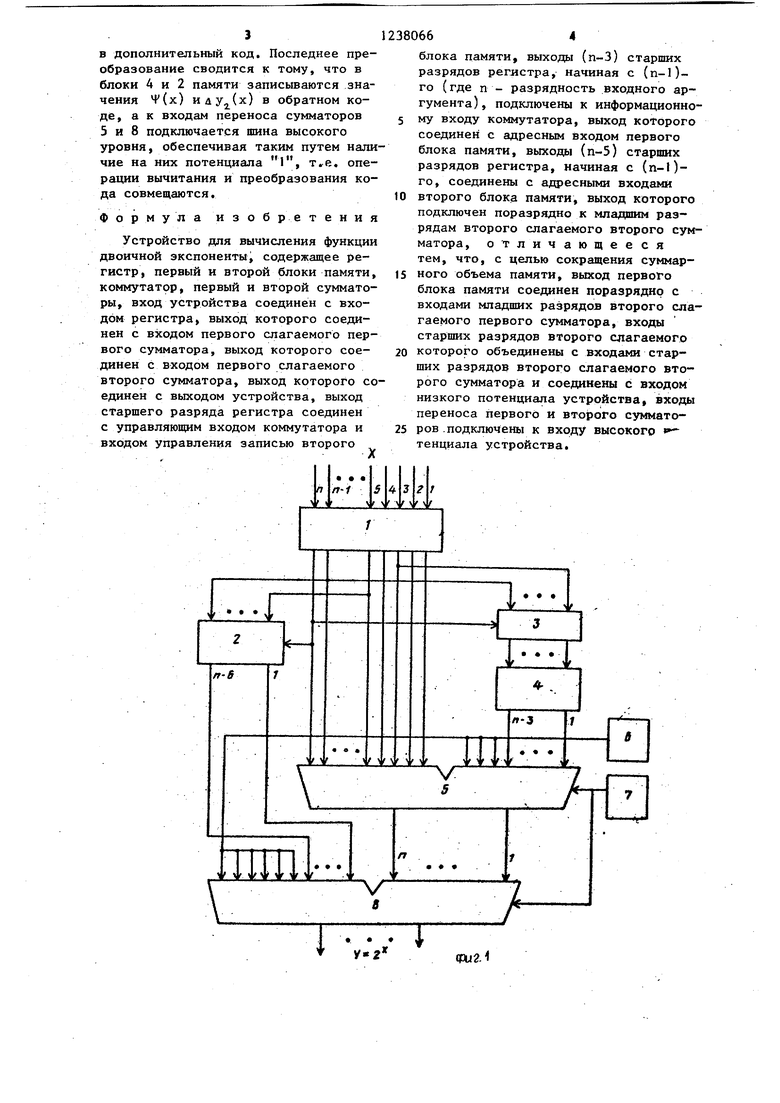

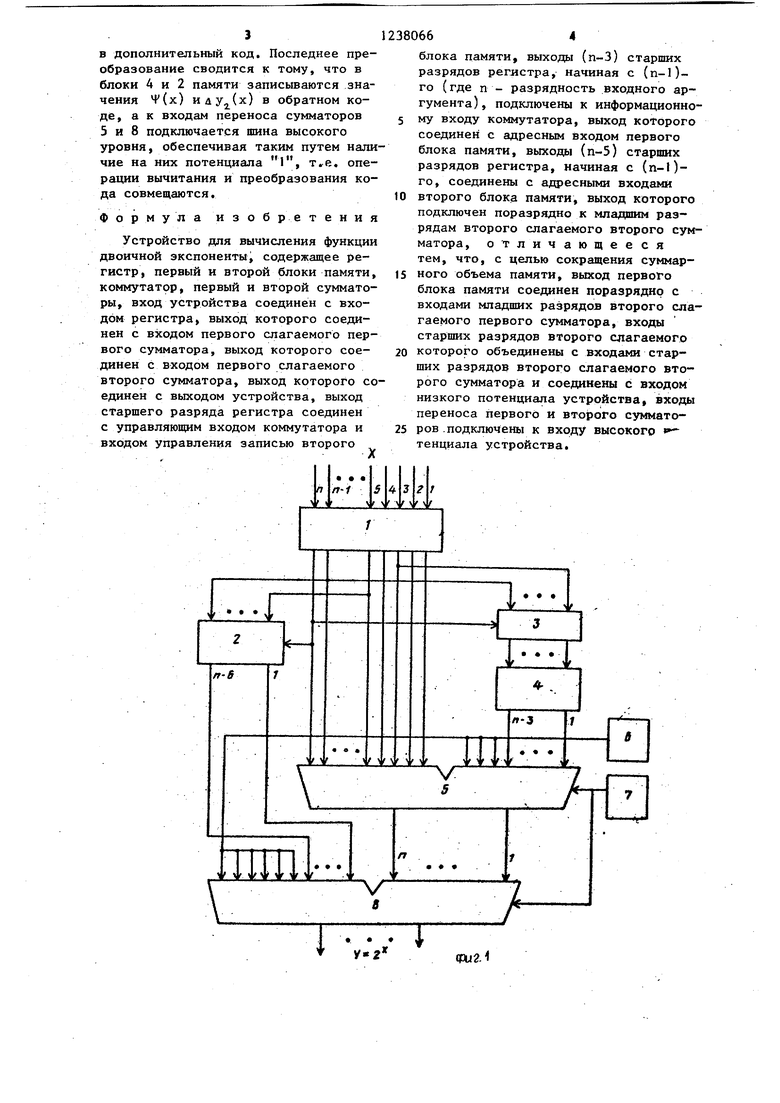

На фиг. 1 приведена структурная схема устройства для вычисления функции двоичной экспоненты; на фиг, 2 - эпюры, поясняющие принцип преобразования.

Устройство для вычисления функции двоичной экспоненты содержит регистр 1, второй блок 2 памяти, коммутатор 3, первый блок 4 памяти, первый сумматор 5, вход 6 низкого потенциала устройства, вход 7 высокого потенциала устройства и второй сумматор 8.

Работа устройства основана на кусочно-линейной аппроксимации функции , X fe, 1) с последующей коррекцией разности между исходной функцией и ее линейным приближением, называемой функцией коррекции.

На фиг. 2а показана аппроксимация функции у 2, xefO, l) прямой линией, откуда видно, что входной код X содержит часть информации о выходной величине у и может использоваться как грубое приближение исходной функции Разность между исходной функцией и ее линейным приближением Л У (х) 2 -(х+1) показана на . фиг. 2S. Анализ функции д.у,(х) показывает , что

,ДУ Сх) -L

- 1 м

-3

Построим функцию Ч (х), которая будет являться симметричным отображением д у, (х) для значений х СО, ) , относительно оси проведенной через точку

I (фиг. 2 6).

Очевидно, что если на интерв.але х е

1 V

О, ) в качестве аргумента функции

4 (х) брать дополнение х до 1 то функция (х) будет совпадать с функцией д у,.(х), вследствие построенной симметрии. Дпя получения точного зна- чения функции двоичной экспоненты

г 1 Л

необходимо на интервале L у, U учесть

значения функции &у (х) Ч (х) - йу (х) (фиго 2), причем

hy.()L

2

-6

Значения функций Ч (х) илу(х), которые при получении функций двоичной экспоненты выступают в роли функций коррекции, запоминаются в блоках памяти и используются для уточнения результата Объемы блоков памяти, необходимых для запоминания Ч (х) и

ду(х), равны

-j

Q (n-3)- 2 бит;

(1)

Q,

) 2

Н-6

(п-б), (2)

Дополнительная двойка в выражении (2) учитывает двухзначность (в математическом смысле) функции д у (х).

Таким образом, функция двоичной экспоненты вычисляется следующим образом:

сегмент xeLO, -j) : у(х)( 1+х)+Н ( Ux); сегмент ., l) ; у(х)( И-х)+ (х)

5

0

5

0

5

Л У,).

+ Л (3)

Корректирующая функция д у.(х) не используется на первом участке, а в качестве аргумента для функции Ч ( х) берется дополнение х до единицы, т.е. его обратный код. Таким образом работа коммутатора 3 заключается в том,

что для значений , -j) он. инвертирует значения х, а для ., l)

пропускает значения х без изменения. Управление коммутатором осуществляется старшим разрядом кода аргумента X. Практически коммутатор реализуется на схемах Сложение по модулю два. Сумма ( 1+х)+t ( ) или (l+x) + Ч(х)/образуется на выходах сумматора 5, а окончательный результат - на выходе сумматора 8, однако так как функции Ч(х) и л у(х) отрицательные, то для получения верного результата необходимо или осуществить операцию вычитания, что привело бы к усложнению схем, сумматоров 5 и 8, или осуществить предварительное преобразование значений функции ч(х) ИА У (х)

1

в дополнительный код. Последнее преобразование сводится к тому, что в блоки 4 и 2 памяти записываются значения Ч (х) в обратном коде, а к входам переноса сумматоров 5 и 8 подключается шина высокого уровня, обеспечивая таким путем наличие на них потенциала I, т.е. операции вычитания и преобразования кода совмещаются.

Формула и 3 о б ре тения

Устройство для вычисления функции двоичной экспоненты, содержащее регистр, первый и второй блоки памяти, коммутатор, первый и второй сумматоры, вход устройства соединен с входом регистра, выход которого соединен с входом первого слагаемого первого сумматора, выход которого сое- динен с входом первого слагаемого второго сумматора, выход которого соединен с выходом устройства, выход старшего разряда регистра соединен с управляющим входом коммутатора и входом управления записью второго

1 - I У.2

блока памяти, выходы (п-З) старших разрядов регистра, начиная с (п-1)- го (где п - разрядность входного аргумента), подключены к информационному входу коммутатора, выход которого соединен с адресным входом первого блока памяти, выходы (п-5) старших разрядов регистра, начиная с (n-l)- го, соединены с адресными входами второго блока памяти, выход которого подключен поразрядно к младшим разрядам второго слагаемого второго сумматора, отличающееся тем, что, с целью сокращения суммарного объема памяти, выход первого блока памяти соединен поразрядно с входами младших разрядов второго слагаемого первого сумматора, входы старших разрядов второго слагаемого которого объединены с входами старших разрядов второго слагаемого второго сумматора и соединены с входом низкого потенциала устройства, входы переноса первого и второго сумматоров .подключены к входу высокого

тенциала устройства.

(Pu2.

ayrfX.)

ЛУгМ

-7-е

Составитель А, Шуляпов Редактор М. Товтин ТехредМ.Ходанич Корректор Л.Патай

3292/49

Тираж 671 Подписное ВНИИПИ Государственного комитета СССР

по.делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

1/2

..|4Фие. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции двоичной экспоненты | 1985 |

|

SU1305675A1 |

| Устройство для потенцирования | 1986 |

|

SU1348833A1 |

| Логарифмический преобразователь | 1981 |

|

SU959073A1 |

| Устройство вычисления функции арктангенс отношения | 1988 |

|

SU1585793A1 |

| Квадратор | 1986 |

|

SU1325469A1 |

| Логарифмический преобразователь | 1984 |

|

SU1196860A1 |

| Логарифмический преобразователь | 1986 |

|

SU1401457A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1001092A1 |

| Устройство для вычисления функций @ и @ | 1988 |

|

SU1608651A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано при построении специализированных вычислителей, информационно-измерительных систем, цифровых устройств для обработки сигналов в реальном времени и гидридных функциональных преобразователей. Цель изобретения - уменьшение суммарного объема используемой памяти, В состав устройства входят регистр, два блока памяти, коммутатор и два сумматора. Уменьшение суммарного объема памяти достигается за счет использования симметрии функции погрешности аппроксимации исходной функции линейным приближением и единичным коэффициентом наклона. 2 ил. (Л IND со 00 О) О)

| Циделко Во Д., Хохлов Ю | |||

| В, К вопросу лостроения вычислительных устройств логарифмирования и потенцирования | |||

| - Управляющие системы и машины, 1981, 5, с | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логарифмический преобразователь | 1984 |

|

SU1196860A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-12-17—Подача