.г

7 X-Mfji:

/

т

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU1001079A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1985 |

|

SU1269271A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU983701A1 |

| Преобразователь двоичного кода в модулярный код | 1985 |

|

SU1267624A1 |

| Преобразователь числа из двоичной системы счисления в систему остаточных классов | 1983 |

|

SU1125621A1 |

| РЕВЕРСИВНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ | 1990 |

|

RU2022467C1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1986 |

|

SU1388997A1 |

| Преобразователь непозиционного кода в двоичный код | 1988 |

|

SU1578810A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1984 |

|

SU1156058A1 |

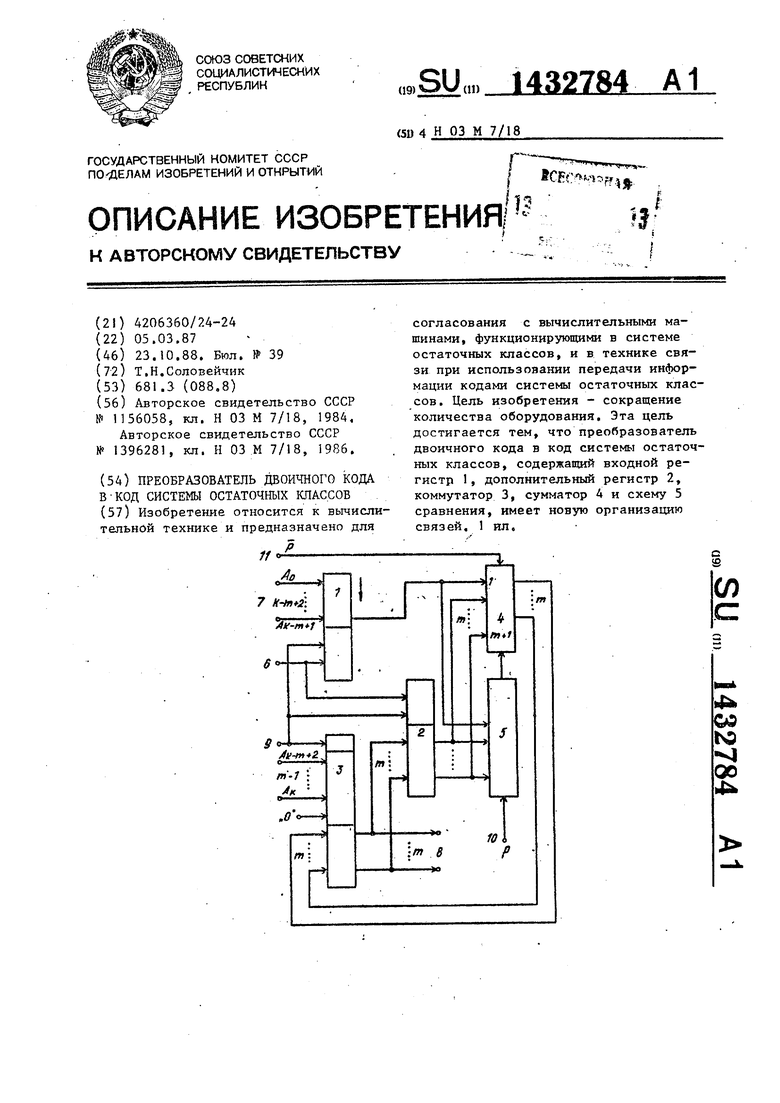

Изобретение относится к вычислительной технике и предназначено для у //осогласования с вычислительными машинами, функционирующими Б системе остаточных классов, и в технике связи при использовании передачи информации кодами системы остаточных классов. Цель изобретения - сокращение количества оборудования. Эта цель достигается тем, что преобразователь двоичного кода в код системы остаточных классов, содержащий входной регистр 1, дополнительный регистр 2, коммутатор 3, сумматор 4 и схему 5 сравнения, имеет новую организацию связей. 1 ил.

.

т-1 :

т:

Л;

г-

т:

ь ч

00 42

JW в

X

f0i

Изобретение относится к вычислительной технике и может быть использовано для согласования с вьгшсли- тельными устройствами, функционирующими в системе остаточных классов, а также в технике связи при использовании передачи информации,кодами системы остаточных классов.

Целью изобретения является .сокра- щение количества оборудования.

На чертеже представлена схема преобразователя двоичного кода в код системы остаточных классов.

Преобразователь содержит входной регистр 1, Дополнительный регистр 2, коммутатор 3, сумматор 4 схему 5 сравнения, тактовый вход 6, информационньш вход 7, выход 8, вход 9 на- чальной, установки, вход 10 значения модуля, и вход 11 дополнительного кода модуля.

Работа преобразователя основана на следующих соотнопениях:

K-m + 1 -К

тш-г X 2+ ,

„т-г

2 + Ац.,

+ А

k-ni+2

S,., (S,-- 2 + А;-, );

S(, ( 2 + Ад) modp X modp

где р - значение модуля;

X - значение числа в двоичной

системе счисления; (1 1 +К)- коэффициенты в двоичной системе счисления, А,1,А, 111

m log, + 1 - количество двоичных разрядов, необходимы для -представления р;

Sg(e О - K-in+2) - промежуточные результаты.

При переводе в каждом такте при S - 1S р осуществляется вычитание (S; - 1 - р), причем, так как то вычитание требуется не более одного раза.

Умножение на два в двоичной системе счисления эквивалентно сдвигу на один разряд влево, а последующее сложение с одноразрядным двоичным числом эквивалентно подстановке этого числа в младший разряд результата.

Преобразователь работает следующим образом.

Поступающий на вход 9 начальной установки преобразователя единичньш

Q

5

Q

5

импульс осуществляет запись ипадших (К-т+2) разрядов двоичного числа X во входной регистр 1, а старших (m-l) разрядов числа X - в дополнительный регистр 2, причем в т-й (старший) разряд регистра 2 записывается логический О,

Поступление старщих (m-l) разрядов двоичного числа X на вход дополнительного регистра 2 обеспечивается коммутатором 3 только в режиме начальной установки.

В процессе дальнейшей работы преобразователя коммутатор 3 подключает к входу дополнительного регистра 2 выход сумматора 4,

Далее на вход 6 преобразователя подается пачка из (К-т+1) импульсов, В каждом такте m разрядов с выхода регистра 2 и старший разряд с выхода регистра поступают на второй вход схемы 5 сравнения и на вход второго слагаемого сумматора 4, На схеме 5 сравнения производится сравнение со значением р, поступающим на ее первый вх од с входа 10 преобразователя, и, если входное число больше или равно р, то вырабатывается сигнал на выходе схемы 5 сравнения, по которому в сумматоре 4 входное число складывается с дополнительным кодом р, поступаюЕцим с входа I 1 преобразователя. Если входное число меньше р, то оно проходит на выход сумматора .4 без изменения. Младшие m разрядов суммь с выхода с -мматора 4 поступают через коммутатора 3 в регистр 2 и на выход 8 преобразователя. При этом осуществляется в каждом такте сдвиг на один разряд младших, разрядов числа X во входном регистре 1,

По окончании пачки входных тактовых импульсов на входе 6 преобразователя, на выходе коммутатора 3 и, следовательно, на выходе 8 преобразователя присутствует двоичное представление числа X по модулю р,

I

Формула изобретения

Преобразователь двоичного кода в код системы остаточных классов, содержащий входной регистр, дополнительный регистр, коммутатор, сумматор и схему сравнения, причем вход начальной установки преобразователя соединен с управляющим входом коммутатора, выход которого является выходом прспбр }зователя, входы старших разрядов информационного входа которого соединены с первым информационным входом коммутатора, тактовый вход преобразователя соединен с входом разрешения записи дополнительного регистра, входы значения модуля и дополнительного кода модуля преобразователя соединены соответственно с первым входом схемы сравнения и входом первого слагаемого сумматора-, вход разрешения которого соединен с выходом схемы сравнения, отличающийся тем, что, с целью сокращения количества оборудования, вход начальной установки преобразователя соединен с установочными входа

ми входного регистра и дополнительного регистра, выходы разрядов которого и выход старшего разряда входного регистра соединены соответственно с входами разрядов второго входа схемы сравнения н входами разрядов второго слагаемого сумматора, выход которого соединен с вторым информационным входом коммутатора, выход которого соединен с информационным входом дополнительного регистра,тактовый вход преобразователя соединен с входом разрешения сдвига входного регистра, информационный вход которого соединен с входами младших разрядов информационного входа преобразователя.

Авторы

Даты

1988-10-23—Публикация

1987-03-05—Подача