I

Изобретение относится к цифровой вычислительной технике и может быть использовано в качестве микропрограммного устройства управления, а также для решения оптимизационных задач при разработке микропрограммного обеспечения вычислительных и управляющих систем.

Известно устройство микропрограммного управления, содержащее два блока памяти, буферный и адресный регистры, счетчики адреса и микрокоманд, два дешифратора, генератор тактовых импульсов, два блока элементов И, четыре элемента И 1.

Недостатком указанного устройства является низкая функциональная возможность.

Наиболее близким по технической сущности и достигаемому положительному эффекту к изобретению является микропрограммное устройство, содержащее последовательно соединенные адресный регистр, перийй вход, которого является кодбм операции устройства, первый дешифратор, первый блок памяти и шифратор, счетчик адреса и второй дешифратор, первый блок элементов И, первый буферный регистр и второй блок элементов И, счетчик микрокоманд и первый элемент И, второй блок памяти, генератор тактовых импульсов, второй буферный регистр, второй - четвертый

10 элементы ИС.2.1.

Недостатком известного устройства являются низкие функциональные возможности, так как в устройстве отсутствует возможность предвари15тельного моделирования и оптимизации микропрограмм, которые используются в дальнейшем для целей управления.

Цель изобретения - сокращение

20 оборудования.

Поставленная цель достигается тем, что микропрограммное устройство управления, содержащее последовательно соединенные регистр адреса, первый дешифратор и первый блок памяти, выход первого адресного поля которого соединен с первым входом шифратора, первый вход регистра адреса является входом кода операции устройства, первый блок элементов И, выход которого через первый буферный регистр соединен с первым входом второго блока элементов И, счетчик адреса, выходом соединенный с первым входом второго дешифратора, счетчик микрокоманд, выходом соединенный с первым входом первого элемента И, второй блок памяти, выходом соединенный с выходом регистра микрокоманд, генератор так товых импульсов, второй буферный регистр, второй, третий и четвертый элементы И, дополнительно содер жит первый и второй информационные регистры, регистр микрокоманд, блок анализа разности, три узла сравнени третий дешифратор, триггер режима, третий - седьмой блоки элементов И, первый - четвертый блоки элементов ИЛИ, пятый элемент И, первый четвертый элементы ИЛИ, элемент ИЛИ-И, причем выход микроопераций регистра микрокоманд соединен с первым входом первого узла сравнени и является выходом микроопераций устройства, выход логических условий регистра микрокоманд соединен с первым входом третьего дешифратора, второй вход которого соединен с выходом второго адресного поля первого блока памяти, второй вход третье го дешифратора соединен с нулевым выходом триггера режима, единичный вход которого является информационным входом устройства, а единичный выход триггера режима соединен со вторым входом шифратора, выход которого соединен со вторым входом регистра адреса, выхрд третьего дешифратора соединен с первым входом первого блока элементов ИЛИ, второй вход которого соединен с выходом второго дешифратора, а выход первого блока элементов ИЛИ - с адресным входом второго блока памяти, информационный вход которого соединен с выходом второго блока элементов ИЛИ, первый - третий входы кото рого соединены соответственно с выхо дами третьего - пятого блоков элементов И, первый вход третьего блок элементов И соединен со вторым входом первого узла сравнения и с выходом -микрокоманд первого информационного регистра, вход которого является информационным входом устройства, выход метки начала первого информационного регистра соединен с первым входом второго элемента И, второй вход которого соединен с первым выходом второго узла сравнения, а аыход второго элемент а И - с первым входом первого элемента ИЛИ, выход которого соединен с первым входом первого блока элементов И, второй вход которого соединен с выходом счетчика адреса, первыми входами второго узла сравнения, блока анализа разности и шестого блока элементов И, выход через второй буферный регистр соединен с первым входом седьмого блока элементов И, второй вход которого соединен с выходом второго элемента ИЛИ, а выход седьмого блока элементов И - с первым входом третьего блока элементов ИЛИ, второй вход которого является информационным входом устройства, третий вход третьего блока элементов ИЛИ соединен с первым выходо блока анализа разности, а четвертый выход третьего блока элементов ИЛИ соединен с выходом второго блока элементов И,, первый вход которого соединен со вторым входом второго узла сравнения, второй вход которого соединен со вторым входоммпервого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход третьего блока элементов ИЛИ соединен с информационным вводом счетчика адреса, счетный вход которого соединен с выходом элемента ИЛИ-Иу первый вход которого соединен со вторым входом третьего элемента ИЛИ, второй вход элемента ИЛИ-И - с первым входом четвертого элемента ИЛИ, первый вход четвертого блока элементов И соединен с выходом микрокоманд второго информационного регистра, вход которого является информационным входом устройства, выход метки конца второго информационного регистра соединен с инверсными входами четвертого блока элементов И и четвертого элемента ИЛИ, а также с первым входом второго и вторым входом первого элементов ИЛИ, выход метки начале второго информационного регистра соединен со вторым входом шестого блока элементов И, первый вход генератора тактовых импульсов соединен с первым входом третьего элемента И, выход которого соединен со входом считывания второго блока памяти, вход записи соединен с выходом четвертого элемента И, первый вход которого соединен со вторым входом генератора тактовых импульсовJ а второй вход четвертого элемента И соединен с выходом третьего элемента ИЛИ, информационный вход устройства соединен с первым входом третьего узла сравнения, второй вход которого соединен с выходом счетчика кмкрокоманд, счетный вход которого соединен с выходом первого узла сравнения и вторым входом блока анализа разности, а выход третьего узла сравнения - с инверсным входом элемента ИЛИ-И и первым входом пятого элемента И, второй вход которого соединен со вторым выходом блока анализа разности, а выход пятого элемента И с первым входом пятого блока элементов И и первым управляющим входом второго.дешифратора, второй управляющий вход которого соединен с выходом четвертого элемента ИЛИ, третий выход генератора тактовых импульсов соединен с управляющим входом первого дешифратора, соответствующие входы группы входов шифратора соединены со вторыми и третьими выходами первого и второго информационных регистров, выходами и третьего узлов сравнения, вторым выходом блока анализа разности, выходами первого и пятого элементов И, третий .вход первого узла сравнения, третий вход третьего узла сравнения, третий и четвертый входы блока анализа разности, установоч-, ные входы счетчика адреса и счетчика микрокоманд, второй вход второго элемента ИЛИ, третий вход первого элемента ИЛИ, первый и второй входы первой группы входов элемента ИЛИ-И, второй вход второго блока элементов И, второй вход третьего блока элементов И и второй вход пятого блока элементов И соединены с соответствующими выходами поля микроопераций первого блока памяти. Кроме того, блок анализа разности содержит буферный регистр, сумматор, три блока элементов И, узел сравнения и

шестой элемент И, причем первый вход блока соединен с прямым входом первого блока элементов И и с входами элемента И, выход которого соединен с инверсным входом первого и первым входом второго блока элементов И, второй вход которого соединен с первым входом сумматора и вторым входом блока, а выход второго блока элементов И - со входом буферного регистра, выход которого соединен с первым входом узла сравнения, второй вход которого соединен с первым входом третьего блока элементов И . и выходом сумматора, второй вход Которого соединен с выходом первого блока элементов И, третий вход узла сравнения соединен с третьим входом блока, четвертый вход которого соединен со вторым входом третьего блока элементов И, выход которого является первым выходом блока, второй вход которого соединен с выходом узла сравнения.

Информация в устройстве хранится в двух блоках памяти,

В первом блоке памяти хранятся управляющие микропрограммы, позволяющие- управлять выборкой информации из второго блока памяти. Во втором блоке памяти, представляющем динамическое микропрограммное :; запоминающее устройство, содержится информация о линейных последовательностях операционных микрокоманд и логических условиях перехода.

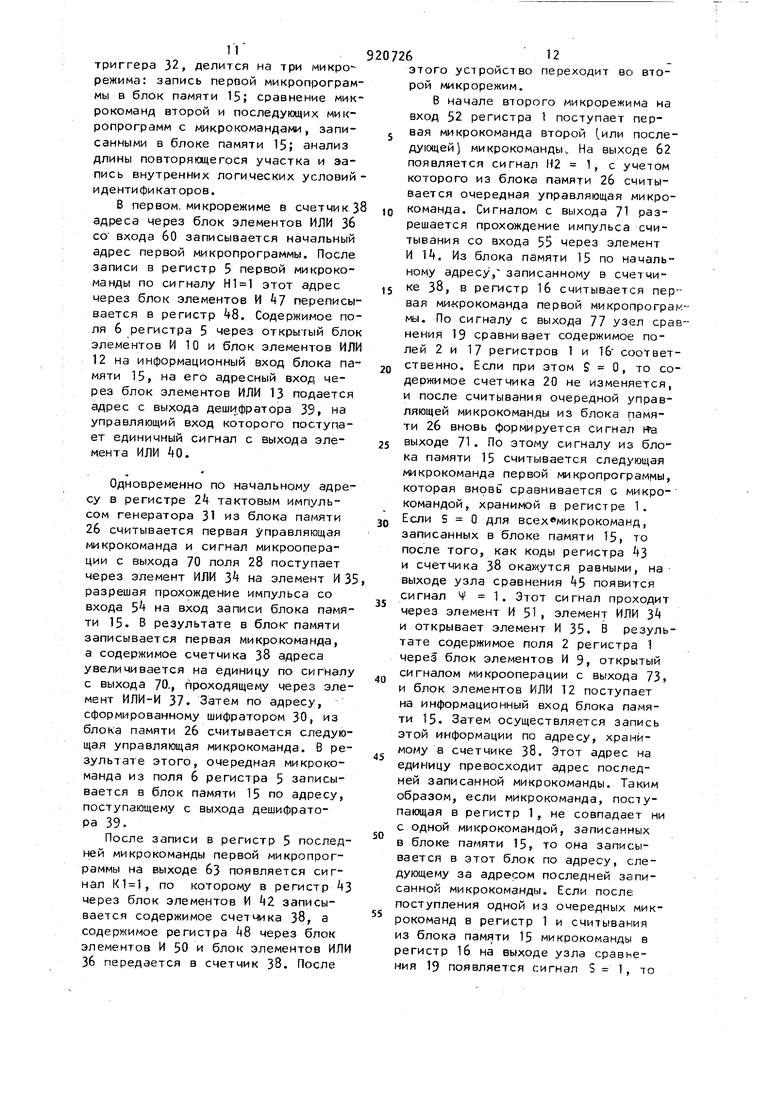

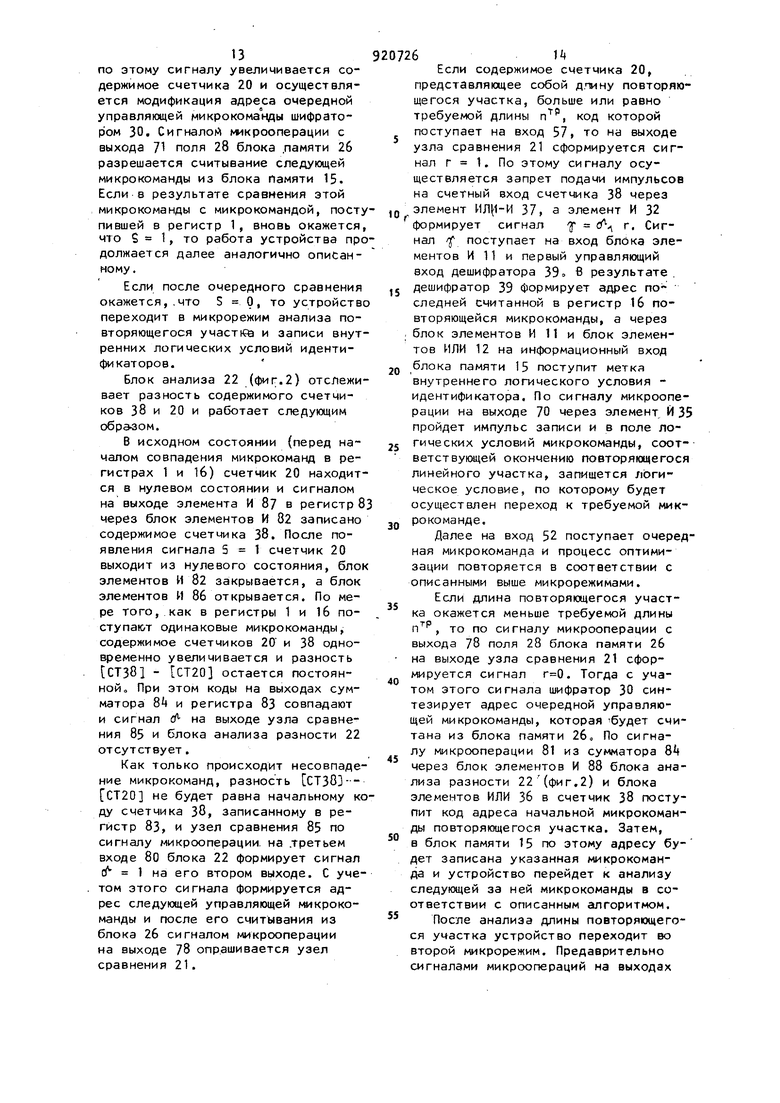

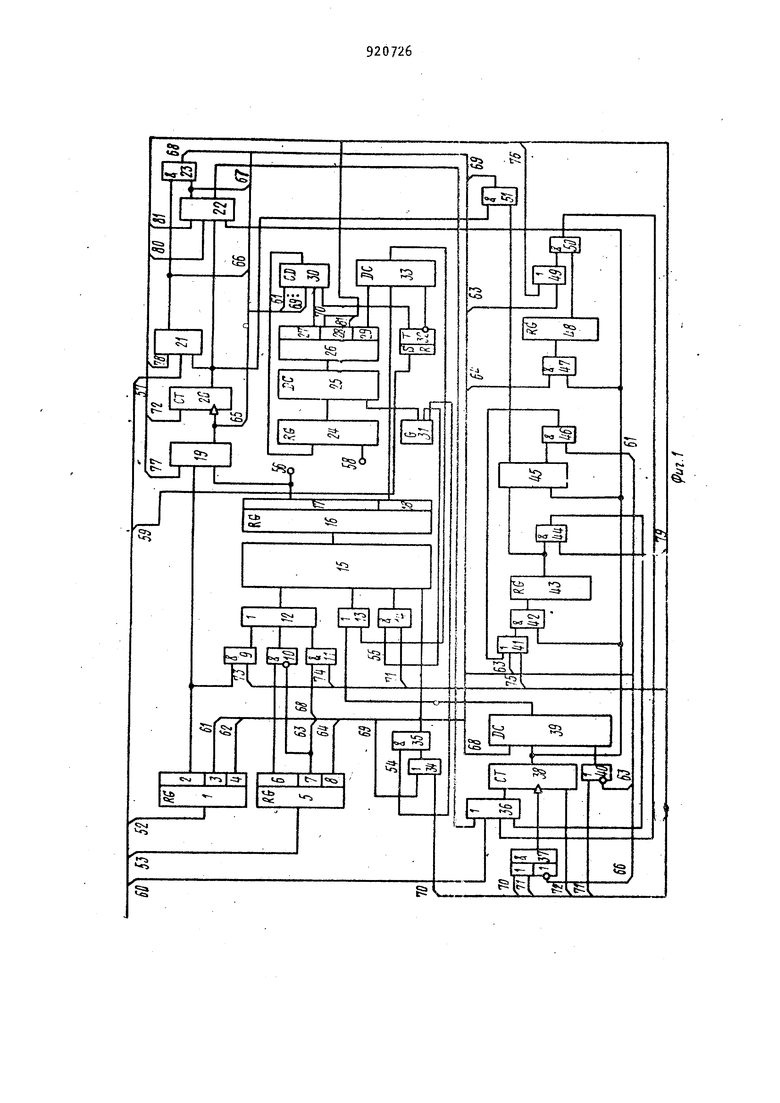

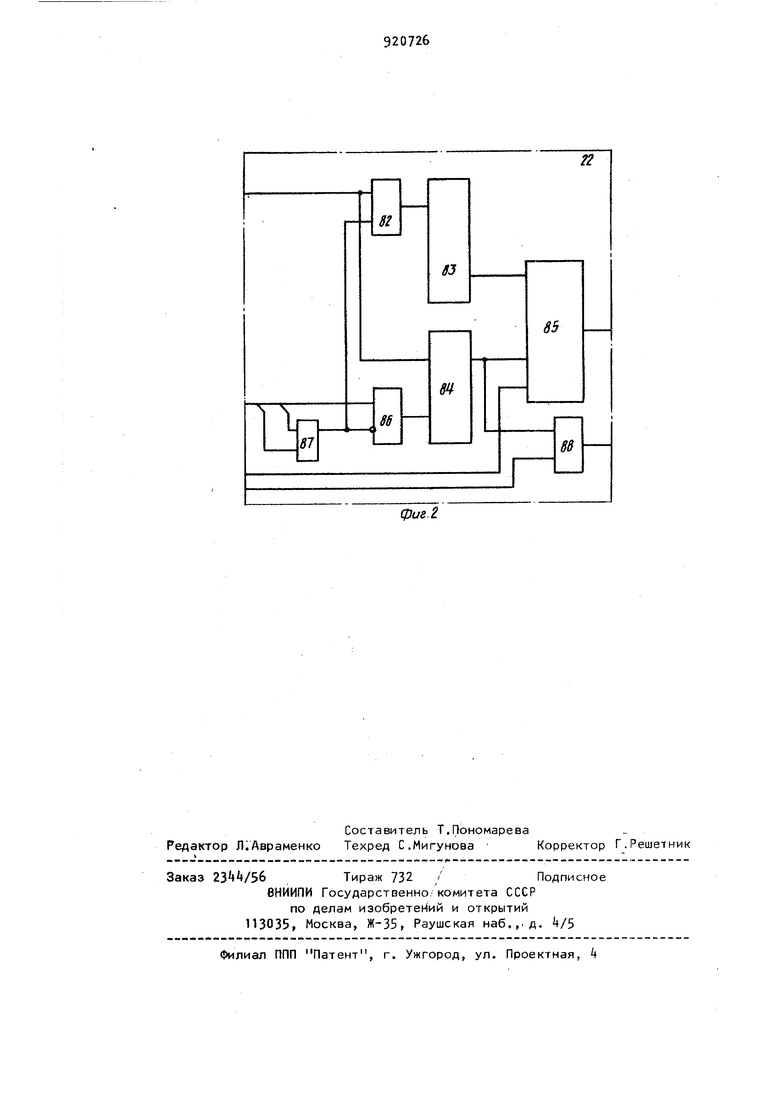

На фиг.1 приведена функциональная схема устройства; на фиг.2 функциональная схема блока анализа разности.

Функциональная схема устройства (фиг.1) содержит первый информационный регистр 1 с полями микрокоманд 2, метки конца 3, метки начала , второй информационный регистр 5 с полями микрокоманд 6, метки конца 7, метки начала 8, третий - пятый блоки элементов И 9 - П соответственно, второй 12 и первый 13 блоки элементов ИЛИ, третий элемент И 1, второй блок памяти 15, регистр.1б. микрокоманд с полями микроопераций 17 и логических условий .18, первый узел сравнения 19, счетчик 20 микрокоманд, третий узел сравнения 21i блок анализа разности 22, пятый элемент И 23, регистр адреса 2k, первый дешифратор 25, первыА блок памяти 26 с первым адресным полем 27, полем 28 микроопераций и вторым адресным полем 29, шифратор 30, генератор 31 тактовых импульсов, триггер 32 режима, третий дешифратор 33, третий элемент ИЛИ 3 четвертый элемент И 35, третий блок элементов ИЛИ 36, элемент ИЛИ-И 37 счетчик 38 адреса, второй дешифратор 39, четвертый элемент ИЛИ if О, первый элемент ИЛИ 41, первый блок элементов И k2, первый буферный регистр 3, второй блок элементов И , второй узел сравнения 45 второй элемент И 46, шестой блок элементов И 47, второй буферный регистр 48, второй элемент ИЛИ 49, седьмой блок элементов И 50, первый элемент И 51. Кроме того, обозначены первый и второй информационные входы 52 и 53 устройства соответственно, входы импульсов считывания и записи 54 и 55 устройства соответственно, выход микроопераций 5б устройства, вход 57 задания глубины оптимизации устройства, вход 58 кода операции устройства, вход 59 задания- режима работь устройства, вход 60 начального адреса устройства, второй и третий выходы 61-64 первого и второго информационных регистров соответственно, выходы 65 - 67 первого, четвертого и третьего узлов сравнения соответственно, выход 68 пятого эле мента И, выход б9 первого элемента И, выходы 70-81 поля микроопераций первого блока памяти Блок анализа разности 22 (фиг,2) состоит из блока элементов И 82, буферного регистра 83, комбинационного сумматора 84, уэла сравнения 85, блока элементов И 86, элемента И 87 и бло ка элементов И 88, Микропрограммное устройство управления работает в-дв режимах - режиме моделирования и on тимизации (первый режим) и режиме управления (второй режим). Первому режиму соответствует единичное, а второму - нулевое состояние триггера 32. В первом режиме регистр 24, дешифратор 25, блок памяти 26 и шиф ратор 30 выполняют функцию шестого устройства управления, которое формирует сигналы микроопераций на выходах 70 - 80 поля 28 блока памяти 26 в соответствии с адресами, передаваемыми в регистр 24 шифратором 30. Синхронизация считывания информации осуществляется по импуль сам генератора 31. Адрес очередной управляющей микрокоманды синтезируется е зависимости от информации записанной в первом адресном поле 27, и значений логических условий, поступающих на входы 61-69 шифратора ЗОо Логические условия формируются на выходах различных узлов устройства (регистров 1 и 5, узлов сравнения 19 и 21, блока анализа разности 22, элементов И 23 и 51), с целью организации ветвлений в последовательностях управляющих микрокоманд . Сигналы К1 (HI) и К2 (Н2) на выходах 63 (64) и 61 (б2) регистров 5 и 1 соответственно равны единице в последних (первый) микрокомандах первой и второй, а также последующих микропрограмм. Во втором блоке памяти 15 хранятся последовательности операционных микрокоманд, считываемых в регистр 16. Информация записывается в 6jfoK памяти 15 из регистров 5 (первая микропрограмма) , 1 (вторая и последующие) , блоки элементов И 9 и 10 и блок элементов ИЛИ 12, Кроме того, через блок элементов И 11 осуществляется запись Значений внутренних логических условий - идентификаторов, определяющих переход к выполнению требуемой линейной последовательности. Адрес, по которому производится запись или считывание информации, формируется дешифраторами 39 и 33, через блок элементов ИЛИ 13. В первом режиме адрес формируется дешифратором 39 в соответствии с кодом, записанным в счетчике 38, по сигналам управления, поступающим через элемент ИЛИ 40. Исходное состояние счетчика 38 устанавливается через блок элементов ИЛИ Зб по коду на входе задания начального адреса 60 или по кодам, записанным в буферных регистрах 43 и 48. Содержимое счетчика увеличивается по сигналам г-и-жроопераций на выходах 70 и 71 поля 28 блока памяти 26, этими сигналами также разрешается соответственно считывание и запись информации в блок памяти 15 -по импульсам на входах 54 и 55, поступающим на элементы И 35 и 14. Управляющий сигнал, по которому формируется адрес дешифратором 39, поступает через элемент ИЛИ 40. Первый буферный регистр 43 Г1редназначен для хранения конечного адреса, по которому записана последняя микрокоманда в блок памяти 15. Запись ко да в регистр 43 производится из счет чика 38 через блок элементов И 42 по сигналам, формируемым элементом ИЛИ il р Содержимое регистра 3 переписы вается в счетчик 38 через блок эле ментов И Ц, управляемый сигналом н выходе 79 поля микроопераций 28 бло ка памяти 26. Второй буферный регист k8 используется для хранения начального адреса, по которому записана первая микрокоманда первой микропрограммы. Запись кода адреса в регистр +8 из 38 осуществляет ся через блок элементов И «7 по си налу начала первой микропрограммы на выходе 6 регистра 5 . Перезапись содержимого регистра В в i счетчик 38 производится через блок элементов И 50 по сигналу, формируемому элементом ИЛИ 49 после прихода сигнала с выхода 63 регистра 5 свидетельствующего об окончании записи первой микропрограммы (), или сигнала с выхода 76 поля микроопераций 28 блока памяти 26. Первый узел сравнения 19 предназначен для сравнения микрокоманд, поступающих в регистр 1 и считываемых из блока памяти 15 в регистр 16 Узел .сравнения 19 по сигналу микрооперации на выходе 77 поля 28 блока памяти 26 формирует сигнал S, причем р, если RG1 RG16U-, |0, если IRG161 T где - содержимое j-того пол i-Toro регистра. Счетчик микрокоманд 20 осуществляет подсчет числа совпадающих команд и хранит код длины повторяющейся последовательности. Второй узел сравнения 45 производит сравнение содержимого регистра 43 и счетчика 38. Сигналы Ч и У на первом и втором выходах узла сравнения 43 определяются следующим образом:если RG431 СТ381; если RG43i 1СТ38. ., 1, если ICT381-, , если RG431 lCT381. Элемент И 46 при V 1 и разрешает перезапись в регистр 43 содержимого счетчика 38. Элемент И 51 при4 1 и нулевом состоянии счетчика 20 формирует сигнал S , разрешающий прохождение через элемент И 35 импульса записи информации в блок памяти 15. Кроме того, разрешающий сигнал может поступить с выхода 70 поля микроопераций 28 через элемент ЯПИ 3. Третий узел сравнения 21 предназначен для сравнения по сигналу микрооперации на выходе 72 длины повто- ряющейся последовательности ее требуемым значением Ь и формирования сигнала Т , для которого справедливо следующее если СТ211 7/ если СТ2П п Блок анализа разности 22 используется для получения сигнала сЛ , определяемого следующим образом: 1,если tCT38 - CT20l) 0,если CT38l- CT20 Const. Элемент И 87 (фиг.25 предназначен для контроля нулевого состояния счетчика микрокоманд 20. БЛок элементов И 82 (86) управляет подачей кода счетчика 38 (20) в регистр 83 (сумматор 84), Регистр 83 осуществляет хранение кода счетчика 38, соответствующего нулевому состоянию счетчика 20. Сумматора 84 определяет разность кодов, записанных в счетчиках 38 и 20. Узел сравнения 85 производит сравнение начального кода, записанного в счетчике 38 при нулевом состоянии счетчика 20 (т.е. начальной разности ССТ381- СТ20 при СТ20 0) с кодом текущей разности состояний этих счетчиков. Блок элементов И 88 предназначен для управления передачей в счетчик 38 кода разности ICT381 - СТ20 , который представляет собой код адреса первой повто- : ряющейся микрокоманды. Это позволяет затем продолжить дальнейший анализ с адреса начала повторения и указать в микрокоманде, предшествующей повторяющемуся участку требуемой длины, адрес безусловного перехода к соответствующему участку, ранее записанному в блоке памяти 15. Сигналом У сЛт на выходе 68 элемента И 23 разрешается запись внутреннего логического условия идентификатора по сигналу на выходе 74 блока памяти 26, через блок элементов 11 и блок элементов ИЛИ 12 в блок памяти 15. Микропрограммное устройство функционирует следующим образом. Первый режим работы, которому соответствует единичное состояние триггера 32, делится на три микрорежима: запись первой микропрограм мы в блок памяти 15; сравнение микрокоманд второй и последующих микропрограмм с микрокомандами, записанными в блоке памяти 15; анализ длины повторяющегося участка и запись внутренних логических условий идентифи кат оров. В первом, микрорежиме в счетчик 3 адреса через блок элементов ИЛИ 36 СО входа 60 записывается начальный адрес первой микропрограммы. После записи в регистр 5 первой микрокоманды по сигналу этот адрес через блок элементов И 47 переписывается в регистр k8. Содержимое поля 6 регистра 5 через открытый блок элементов И 10 и блок элементов ИЛИ 12 на информационный вход блока па мяти 15, на его адресный вход через блок элементов ИЛИ 13 подается адрес с выхода деши,фратора 39, на управляющий вход которого поступает единичный сигнал с выхода элемента ИЛИ 40. Одновременно по начальному адресу в регистре 24 тактовым импульсом генератора 31 из блока памяти 26 считывается первая 5правляющая микрокоманда и сигнал микрооперации с выхода 70 поля 28 поступает через элемент ИЛИ 34 на элемент И 35 разрешая прохождение импульса со входа 54 на вход записи блока памяти 15. В результате в блок- памяти записывается первая микрокоманда, а содержимое счетчика 38 адреса увеличивается на единицу по сигналу с выхода 70., проходящему через элемент ИЛИ-И 37. Затем по адресу, сформированному шифратором 30, из блока памяти 26 считывается следующая управляющая микрокоманда. В результате этого, очередная микрокоманда из поля 6 регистра 5 записывается в блок памяти 15 по адресу, поступающему с выхода дешифратора 39. После записи в регистр 5 последней микрокоманды первой микропро(- раммы на выходе 63 появляется сигнал , по которому в регистр 4з через блок элементов И 42 записывается содержимое счетчика 38, а содержимое регистра 48 через блок элементов И 50 и блок элементов ИЛИ 36 передается в счетчик 38. После 6 во втоЭТОГО устройство переходит рой микрорежим. В начале второго микрорежима на вход 52 регистра поступает первая микрокоманда второй (или последующей) микрокоманды„ На выходе 62 появляется сигнал Н2 1, с учетом которого из блока памяти 26 считывается очередная управляющая микрокоманда. Сигналом с выхода 71 разрешается прохождение импульса считывания со входа 55 через элемент И 14. Из блока памяти 15 по начальному адресу, записанному в счетчике 38, в регистр 16 считывается первая микрокоманда первой микропрограммы. По сигналу с выхода 77 узел сравнения 19 сравнивает содержимое полей 2 и 17 регистров 1 и 16 соответственно. Если при этом , то содержимое счетчика 20 не изменяется, и после считывания очередной управляющей микрокоманды из блока памяти 26 вновь формируется сигнал ид выходе 71. По этому сигналу из блока памяти 15 считывается следующая микрокоманда первой N iKponporpaMMH, которая вновь сравнивается о микрокомандой, хранимой в регистре 1. Если для всех микрокоманд, записанных в блоке памяти 15 то после того, как коды регистра 43 и счетчика 38 окажутся равными, на выходе узла сравнения 45 появится сигнал Ч 1 . Этот сигнал проходит через элемент И 51, элемент ИЛИ 34 и открывает элемент И 35. В результате содержимое поля 2 регистра 1 через блок элементов И 9, открытый сигналом микрооперации с выхода 73 и блок элементов ИЛИ 12 поступает на информационный вход блока памяти 15. Затем осуществляется запись этой информации по адресу, хранимому в счетчике 38. Этот адрес на единицу превосходит адрес последней записанной микрокоманды. Таким образом, если микрокоманда, поступающая в регистр 1, не совпадает ни с одной микрокомандой, записанных в блоке памяти 15, то она записывается в этот блок по адресу, следующему за адресом последней записанной микрокоманды. Если после поступления одной из очередных микрокоманд в регистр 1 и считывания из блока памяти 15 микрокоманды в регистр 16 на выходе узла сравнения 19 появляется сигнал , то по этому сигналу увеличивается содержимое счетчика 20 и осуществляется модификация адреса очередной управляющей микрокоманды шифратором 30. Сигналов микрооперации с выхода 71 поля 28 блока .памяти 26 разрешается считывание следующей микрокоманды из блока Памяти 15. Если в результате сравнения этой микрокоманды с микрокомандой, пост пившей в регистр 1, вновь окажется что S 1, то работа устройства пр должается далее аналогично описанному . Если после очередного сравнения окажется,.что 5 0, то устройств переходит в микрорежим анализа повторяющегося участ(€й и записи внут ренних логических условий идентификаторов. Блок анализа 22 (фиг.2) отслежи вает разность содержимого счетчиков 38 и 20 и работает следующим образом. В исходном состоянии (перед началом совпадения микрокоманд в регистрах 1 и 1б) счетчик 20 находит ся в нулевом состоянии и сигналом на выходе элемента И 8 в регистр 8 через блок элементов И 82 записано содержимое счетчика 38, После появления сигнала 5 1 счетчик 20 выходит из нулевого состояния, бло элементов И 82 закрывается, а блок элементов И 86 открывается. По мере того, как в регистры 1 и 1б поступают одинаковые микрокоманды, содержимое счетчиков 20 и 38 одновременно увеличивается и разность СТЗб - СТ20 остается постоянной.. При этом коды на выходах сумматора В и регистра 83 совпадают и сигнал rf на выходе узла сравнения 85 и блока анализа разности 22 отсутствует, Как только происходит несовпаде ние микрокоманд, разность СТЗОЗ- СТ20 не будет равна начальному к ду счетчика 38, записанному в регистр 83, и узел сравнения 85 по сигналу микрооперации, на .третьем входе 80 блока 22 формирует сигнал 0 1 на его втором выходе. С уче том этого сигнала формируется адрес следующей управляющей NMKPOKOманды и после его считывания из блока 26 сигналом микрооперации на выходе 78 опрашивается узел сравнения 21. 6U Если содержимое счетчика 20, представляющее собой д.мну повторяющегося участка, больше или равно требуемой длины п, код которой поступает на вход 57 то на выходе узла сравнения 21 сформируется сигнал г 1. По этому сигналу осуществляется запрет подачи импульсов на счетный вход счетчика 38 через элемент 37, а элемент И 32 формирует сигнал J сЛ г. Сигнал f поступает на вход блока элементов И П и первый управляющий вход дешифратора 39 б результате . дешифратор 39 Формирует адрес по следней считанной в регистр 16 повторяющейся микрокоманды, а через блок элементов И 11 и блок элементов ИЛИ 12 на информационный вход блока памяти 15 поступит метка внутреннего логического условия идентификатора. По сигналу микрооперации на выходе 70 через элемент И 35 пройдет импульс записи и в поле логических условий микрокоманды, соответствующей окончению повторяющегося линейного участка, запишется логическое условие, по которому будет осуществлен переход к требуемой микрокоманде. Далее на вход 52 поступает очередная микрокоманда и процесс оптимизации повторяется в соответствии с описанными выше микрорежимами. Если длина повторяющегося участка окажется меньше требуемой длины , то по сигналу микрооперации с выхода 73 поля 28 блока памяти 26 на выходе узла сравнения 21 сформируется сигнал . Тогда с учатом зтого сигнала шифратор 30 синтезирует адрес очередной управляющей микрокоманды, которая будет считана из блока памяти 26, По сигналу микрооперации 81 из сумматора 8 через блок элементов И 88 блока ана.пиза разности 22 (фиг.2) и блока элементов ИЛИ 36 в счетчик 38 поступит код адреса начальной микрокоманды повторяющегося участка. Затем, в блок памяти 15 по этому адресу будет записана указанная микрокоманда и устройство перейдет к анализу следукяцей за ней микрокоманды в соответствии с описанным алгоритмом. После анализа длины повторяющегося участка устройство переходит во второй микрорежим. Предаврительно сигналами микроопераций на выходах 72 И 79 поля 28 блока памяти 26 осу ществляется обнуление счетчиков 20 и 38, а из регистра 2 через блок элементов И 4 и блок элементов ИЛИ 36 в счетчик 38 записывается код ад реса из буферного регистра . В последней микрокоманде второй (или последующей) микрокоманды в по ле 3 регистра 1 содержится метка конца , котбрая поступает на вход элемента И i+S. После окончания анализа 5той микрокоманды, ког да содержимое счетчика превзойдет содержимое регистра 43, узел сравнения сформирует сигнал , которым в регистр 3 через блок эл ментов И k2 перепишется код счетчи ка 38, который является кодом адреса, следующим за последней записанной микрокомандной, и указывает границу записанной в блоке памяти 15 информации. В целях сокращения объема инфор мации, записанной во второй блок памяти 15, глубину оптимизации может изменяться путем задания на входе 57 различных значений длины повторяющихся участков „ Критерием оценки при этом являет-ся вели чина -жода, хранимого в регистре и указывающего границу записанной информации. После окончания моделирования и оптимизации микропрограмм устройст во переходит во второй режим - режим управления, которому соответствует нулевое состояние триггера режима 32о Начальный адрес задается кодом операции, поступающим на вход 58. Работа шифратора 30 блокируется, а адрес очередной микрокоманды формируется дешифратором 33 в соответствии с содержимым адресного поля 29 блока памяти 2б иполя логических условий 18 регистра 16. Если в поле 18 записаны метки логических условий - идентификаторов, то дешифратор 33 формирует адрес перехода к микрокоманде, следующей за повторяющимся участком. Если поле 18 свободно, то адрес фор мируется по коду, записанному в поле 29 блока памяти 26. Во втором режиме из блока памяти 15 осуществляется только считывание информации, поэтому на вход 71 элемента И поступают сигналы микроопераций, разрешающие прохождение импульсов считывания со входа 55 устройства. Если в процессе эксплуатации устройства или управляемого им объекта возникает необходимость дополнить или изменить хранимые в блоке памяти 15 микропрограммы, то осуществляется переход в режим моделирования и оптимизации, в котором оптимизируется модифицированный набор микропрограмм с целью повышения ко эффициента использования оборудования и снижения времени выполнения микропрограмм. Таким образом, данное микропрограммное устройство выгодно отличается от известного более широкими функциональными возможностями, которые позволяют решать задачи сокращения объема памяти при обеспечении выполнения требуемых функций управления. Формула изобретения 1. Микропрограммное устройство управления, содержащее последовательно соединенные регистр адреса, первый дешифратор и первый блок памяти, выход первого адресного поля которого соединен с первым входом шифратора, первый вход регистра адреса является входом кода операции устройства, первый блок элементов. И, выход которого через первый буферный регистр соединен с первым входом второго блока элементов И, счетчик адреса, выходом соединенный с первым входом второго дешифратора, счетчик микрокоманд, выходом соединенный с первым входом первого элемента И, второй блок памяти, выходом соединенный с выходом регистра микрокоманд, генератор тактовых импульсов, второй буферный регистр второй, третий и четвертый элементы И, о т ли чающееся тем, что, с целью сокращения оборудования, оно дополнительно содержит первый и второй информационные регистры, блок анализа разности, три узла сравнения, третий дешифратор, триггер режима, третий - седьмой блоки элементов И, первый - четвертый блоки элементов ИЛИ, пятый элемент И, первыйчетвертый элементы ИЛИ, элемент ИЛИ-И, причем выход микроопераций регистра микрокоманд соединен с первым входом первого узла сравнения и яЕзляется выходом микроопераций устройства, выход логических условий регистра микрокоманд соединен с первым входом третьего дешифратора, второй вход которого соединен с выходом второго адресног о поля первого блока памяти, второй вход третьего де.шифратора соединен с нулевым выходом триггера режима, единичный вход которого является информационным входом устройства, единичный выход триггера режима соединен со вторым входом шифратора, выход которого соединен со вторым входом регистра адреса, выход третьего дешифратора соединен с первым входом первого блока элементов ИЛИ,, второй вход ко торого соединен с выходом второго дешифратора, а выхсй первого блока элементов ИЛИ - с адресным входом второго блока памяти, информационный вход которого соединен с выходом второго блока элементов ИЛИ, первый - третий входы которого соединены соответственно с выходами третьего - пятого блоков элементов И, первый вход третьего блока элементов И соединен со вторым входом первого узла сравнения и выходом микрокоманд первого информацион ного регистра, вход которого являет ся информационным входом устройства выход метки начала первого информационного регистра соединен с первым входом второго элемента И, второй вход которого соединен с первым выходом второго узла сравнения, выход второго элемента И - с первым входо первого элемента ИЛИ, выход которого соединен с первым входом первого блока элементов И, второй вход которого соединен с выходом счетчика адреса, первыми входами второго узла сравнения, блока анализа разности и шестого блока элементов И, выход которого через второй буферный регистр соединен с первым входом седьмого блока элементов И, вто рой вход которого соединен с выходом второго элемента ИЛИ, а выход седьмого блока элементов И - с первым входом третьего блока элементов ИЛИ, второй вход которого является информационным входом устройства, третий вход третьего блока элементов ИЛИ соединен с первым выходом блока анализа разности, четвертый выход третьего блока элементов ИЛИ соединен с выходом второго блока элементов И, первый вход 2618 которого соединен с вторым входом второго узла сравнения, второй выход которого соединен со вторым входом первого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход третьего блока элементов ИЛИ соединен с информационным входом счетчика адреса, счетный вход которого соединен с выходом элемента ИЛИ-И, первый вход которого соединен со вторым входом третьего элемента ИЛИ, второй вход элемента ИЛИ-И - с первым входом четвертого элемента ИЛИ, первый вход четвертого блока элементов И соединен с выходом микрокоманд второго информационного регистра, вход которого является информационным входом устройства, выход метки конца второго информационного регистра соединен с инверсными входами четвертого блока элементов И и четвертого элемента ИЛИ, а также с первым входом второго и вторым входом первого элементов ИЛИ, выход метки начала второго информационного регистра соединен со вторым входом шестого блока элементов И, первый вход генератора тактовых импульсов соединен с первым входом третьего элемента И, выход которого соединен со входом считывания второго блока , вход записи которого соединен с выходом четвертого элемента И, первый вход которого соединен со вторым входом генератора тактовых импульсов, а второй вход четвертого элемента И соединен с выходом третьего элемента ИЛИ, информационный вход устройства соединен с первым входом третьего узла сравнения, второй вход которого, соединен с выходом счетчика микрокоманд, счетный вход которого соединен с выходом первого узла сравнения и вторым входом блока анализа разности, а выход третьего узла сравнения - с инверсным входом элемента ИЛИ-И и первыА1 входом пятого элемента И, второй вход которого соединен со вторым выходом блока анализа разности, а выход пятого элемента И - с первым входом пятого блока элементов И и первым управляющим входом второго дешифратора, второй управляющий вход которого соединен с выходом четвертого элемента ИЛИ, тертий выход генератора тактовых импульсов соединен с управляюцим входом первого дешифратора, соответствующие входы группы входов шифратора соединены со вт рыми и третьими выходами первого и второго информационных регистров, выходами первого и третьего узлов сравнения, вторым выходом блока ана лиза разности, выходами первого и пятого элементов И, третий вход пер вого узла сравнения, третий вход третьего узла сравнения, третий и четвертый входы блока анализа разности, устайовленные входы счетчика адреса и счетчика микрокоманд, второй вход второго элемента ИЛИ, третий вход, первого элемента ИЛИ, первый и второй входы первой группы входов элемента ИЛИ-И, второй вход второго блока элементов И, второй вход третьего блока элементов И и второй вход пятого блока элементов И соединены с соответствующими выходами поля микроопераций первого блока памяти, 2. Устройство по п. 1, о т л и чающееся тем, что блок анализа разности содержит буферный регистр, сумматор, три блока элементов И, узел сравнения и элемент И, причем первый вход блока соединен 620 с прямым входом первого блока элементов И, с входами элемента И, выход которого соединен с инверсным входом первого и первым входом второго блока элементов И,второй вход которого соединен с первым входом сумматора и вторым входом блока, выход второго блока элементов И - с входом буферного регистра, выход которого соединен с первым входом узла сравнения, второй вход которого соединен с первым входом третьего блока элементов И и выходом сумматора, второй вход которого соединен с выходом первого блока элементов И, третий вход узла сравнения соединен с третьим входом блока, четвертый вход которого соединен со вторым входом третьего блока элементов И, выход которого является первым выходом блока, второй вход которого соединен с выходом узла сравнения. Источники информации, принятые во внимание при экспертизе , Авторское свидетельство СССР № 827t, кл, G-06 F 9/22, 1975. 2. Авторское свидетельство СССР по заявке № 2633719/18-24, кл. G 06 F9/22, 1978 (прототип)..

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1982 |

|

SU1038944A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1091158A1 |

| Микропрограммное устройство управления | 1980 |

|

SU943728A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Микропрограммное устройство управ-лЕНия C КОНТРОлЕМ | 1979 |

|

SU842813A1 |

| Микропрограммное устройство управления | 1981 |

|

SU999052A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

Авторы

Даты

1982-04-15—Публикация

1980-05-21—Подача