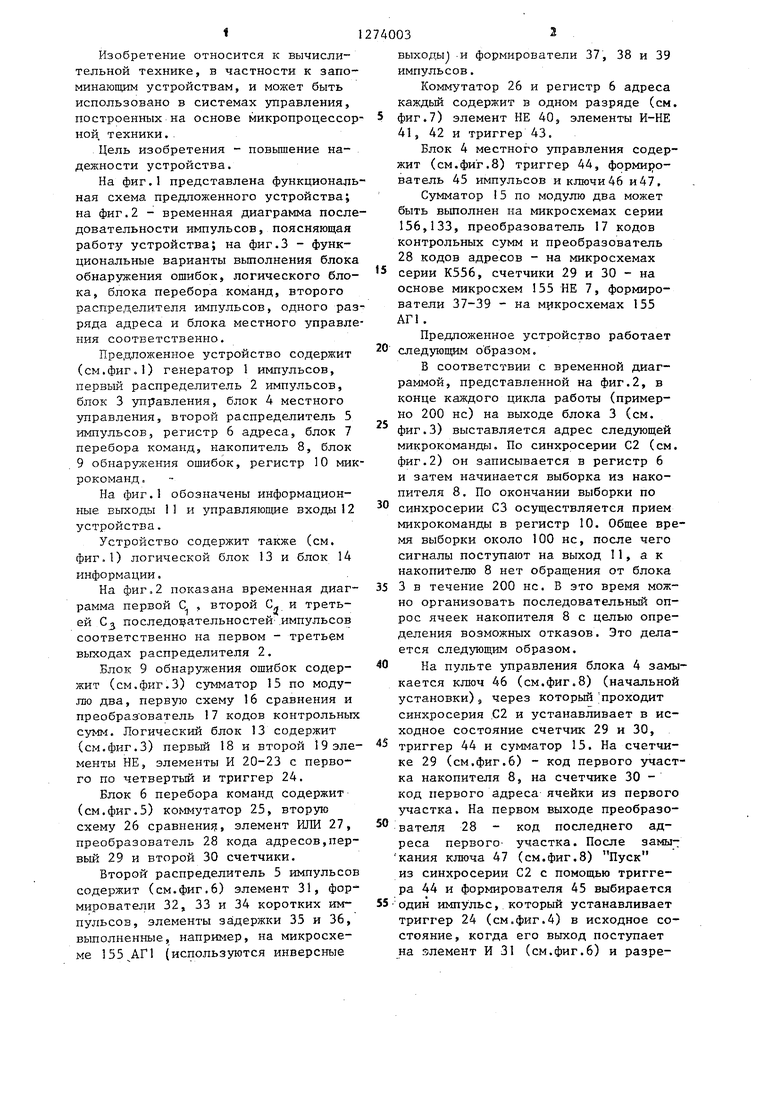

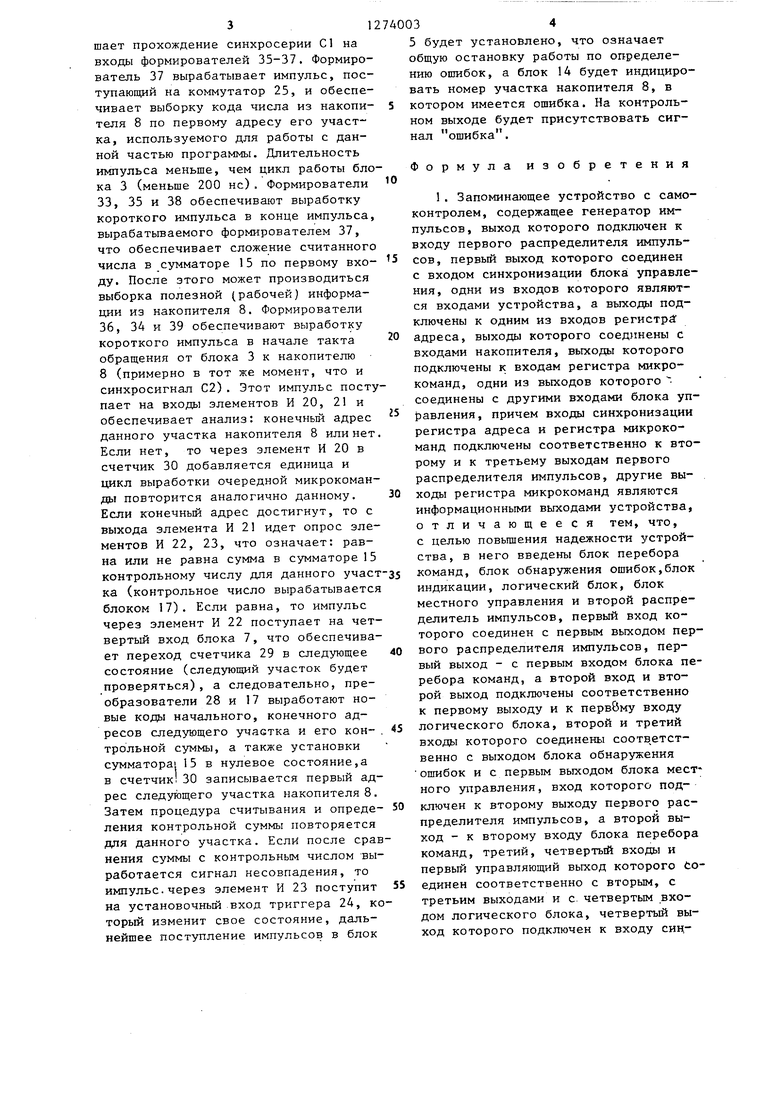

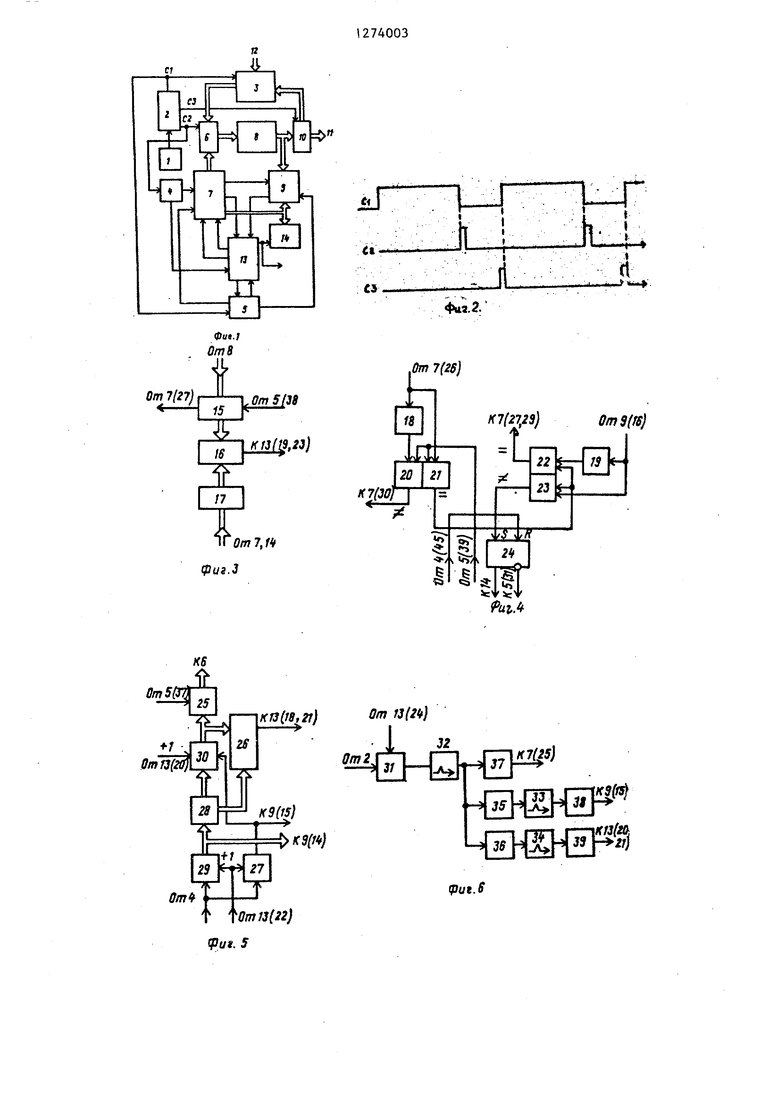

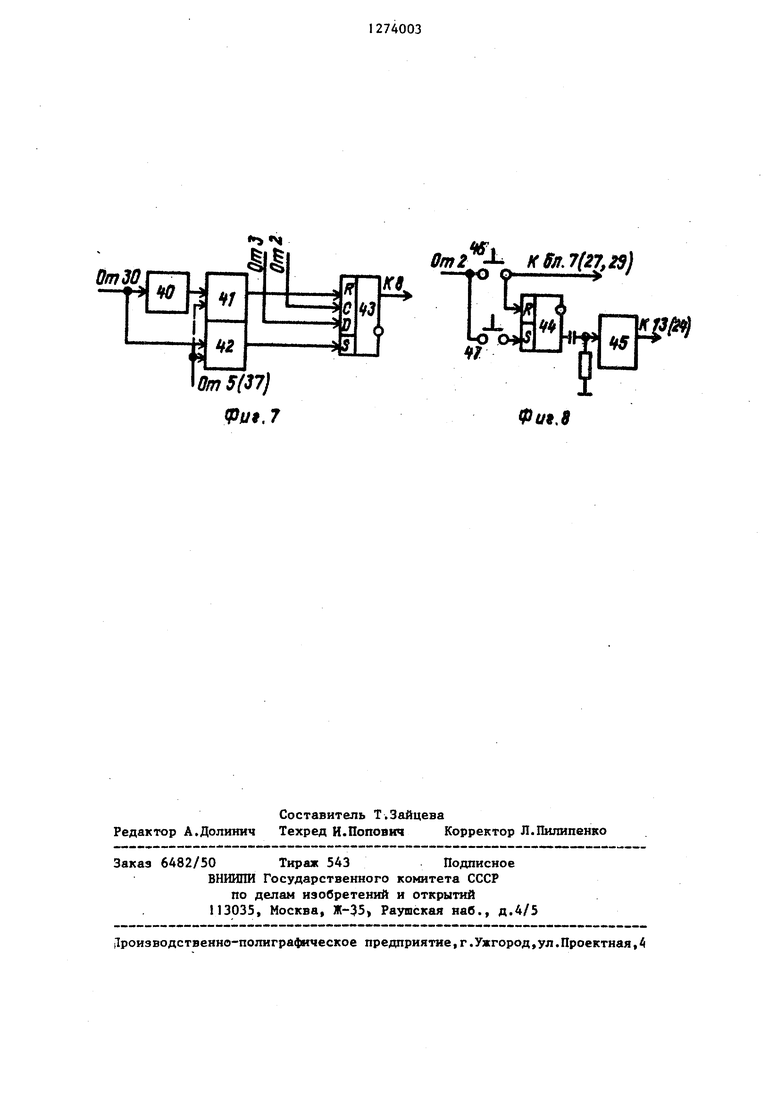

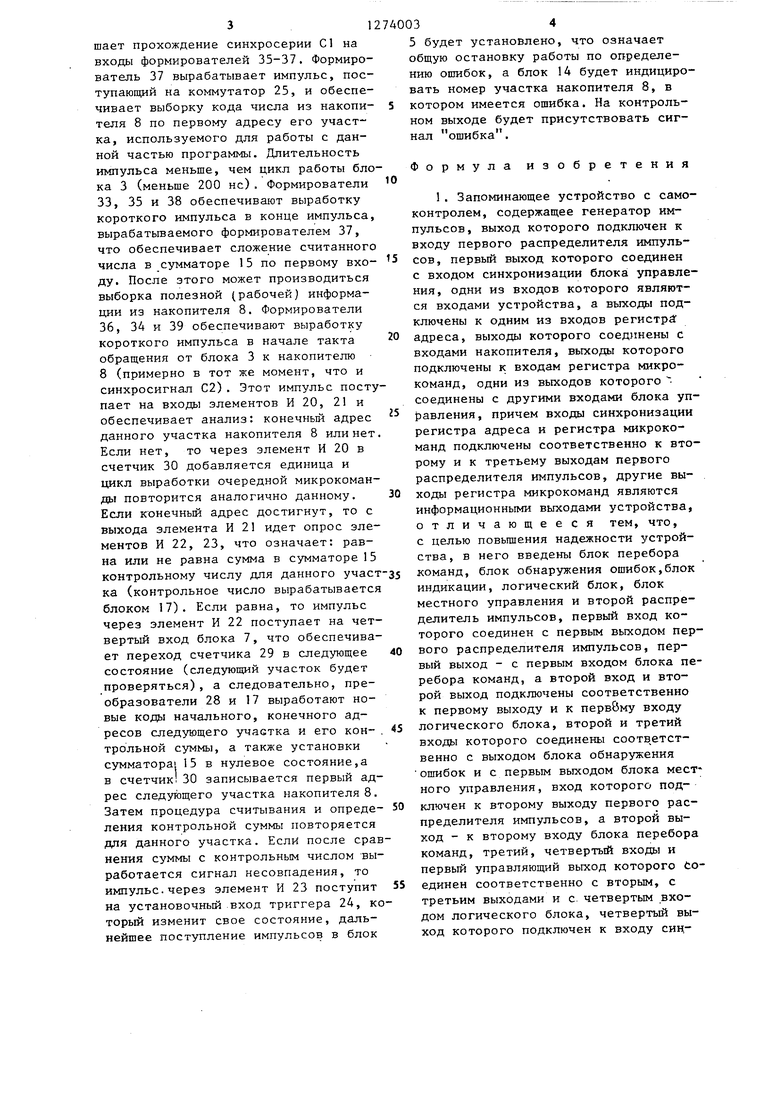

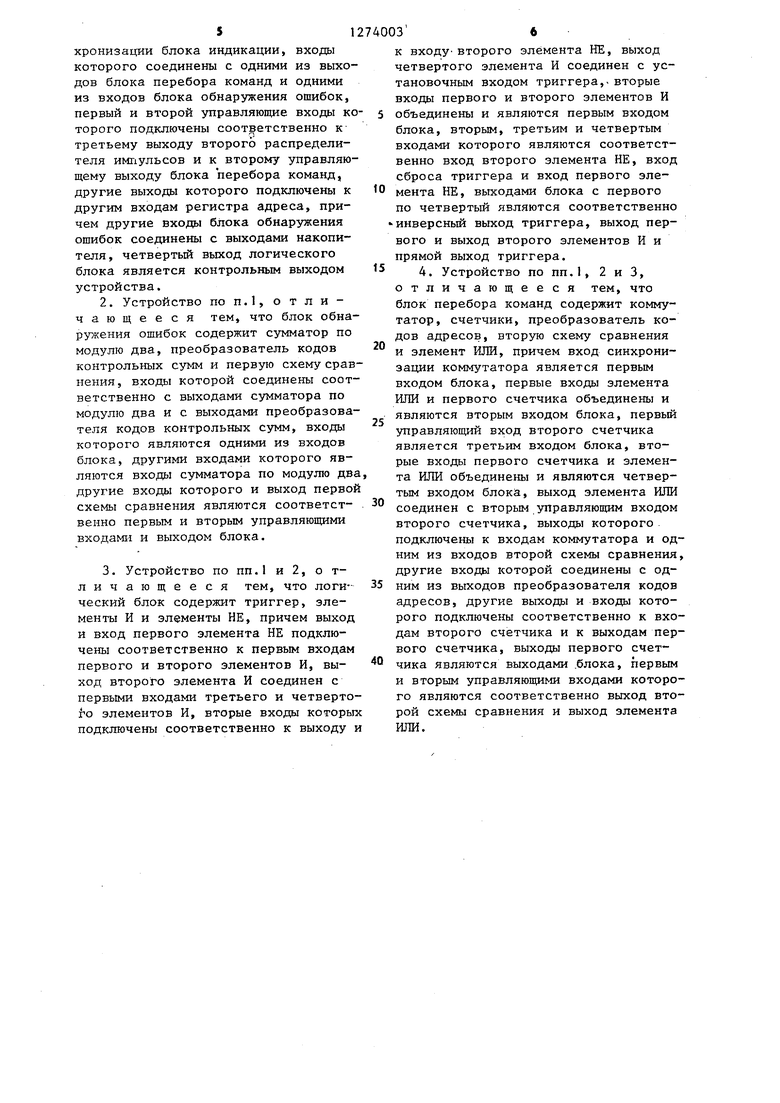

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано в системах управления, построенных на основе микропроцессор ной, техники.. Цель изобретения - повьппение надежности устройства. На фиг.1 представлена функциональ ная схема предложенного устройства; на фиг.2 - временная диаграмма после довательности импульсов, поясняющая работу устройства; на фиг.З - функциональные варианты выполнения блока обнаружения ошибок, логического блока, блока перебора команд, второго распределителя импульсов, одного раз ряда адреса и блока местного управле ния соответственно. Предложенное устройство содержит (см.фиг.1) генератор 1 импульсов, первый распределитель 2 импульсов, блок 3 управления, блок 4 местного управления, второй распределитель 5 импульсов, регистр 6 адреса, блок 7 перебора команд, накопитель 8, блок 9 обнаружения ошибок, регистр 10 мик рокоманд. На фиг.1 обозначены информационные выходы 11 и управляющие входы 12 устройства. Устройство содержит также (см. фигЛ) логической блок 13 и блок 14 информации. На фиг.2 показана временная диаграмма первой С , второй С,, и третьей С последовательностей .импульсов соответственно на первом - третьем выходах распределителя 2. Блок 9 обнаружения ошибок содержит (см.фиг.З) сумматор 15 по модулю два, первую схему 16 сравнения и преобразователь 17 кодов контрольных сумм. Логический блок 13 содержит (см.фиг.З) первый 18 и второй 19 эле менты НЕ, элементы И 20-23 с первого по четвертьй и триггер 24. Блок 6 перебора команд содержит (см.фиг.5) коммутатор 25, вторую схему 26 сравпени;, элемент ИЛИ 27, преобразователь 28 кода адресов,первый 29 и второй 30 счетчики. Второй распределитель 5 импульсов содержит (см.фиг.6) элемент 31, формирователи 32, 33 и 34 коротких импульсов, элементы задержки 35 и 36, выполненные, например, на микросхеме {используются инверсные 032 выходы -и формирователи 37, 38 и 39 импульсов. Коммутатор 26 и регистр 6 адреса каждьш содержит в одном разряде (см. фиг.7) элемент НЕ 40, элементы И-НЕ 41, 42 и триггер 43. Блок 4 местного управления содержит (см.фиг.8) триггер 44, формирователь 45 импульсов и ключи 46 и 47, Сумматор 15 по модулю два может быть вьтолнен на микросхемах серии 156,133, преобразователь 17 кодов контрольных сумм и преобразователь 28 кодов адресов - на микросхемах серии К556, счетчики 29 и 30 - на основе микросхем 155 НЕ 7, формирователи 37-39 - на микросхемах 155 АГ1 . Предложенное устройство работает следующим образом. В соответствии с временной диагра1Ф10й, представленной на фиг.2, в конце каждого цикла работы (примерно 200 не) на выходе блока 3 (см. фиг.З) выставляется адрес следующей микрокоманды. По синхросерии С2 (см. фиг.2) он записывается в регистр 6 и затем начинается выборка из накопителя 8. По окончании выборки по синхросерии СЗ осуществляется прием микрокоманды в регистр 10. Общее время выборки около 100 НС, после чего сигналы поступают на выход 11, а к накопителю 8 нет обращения от блока 3 в течение 200 не. В это время можно организовать последовательный опрос ячеек накопителя 8 с целью определения возможных отказов. Это делается следующим образом. На пульте управления блока 4 замыкается ключ 46 (см.фиг.8) (начальной установки)J через который проходит синхросерия .С2 и устанавливает в исходное состояние счетчик 29 и 30, триггер 44 и сумматор 15. На счетчике 29 (см.фиг.6) - код первого участка накопителя 8, на счетчике 30 код первого адреса ячейки из первого участка. На первом выходе преобразователя 28 - код последнего адреса первого- участка. После замы-: кания ключа 47 (см.фиг.8) Пуск из синхросерии С2 с помощью триггера 44 и формирователя 45 выбирается один импульс, который устанавливает триггер 24 (см.фиг.4) в исходное состояние, когда его выход поступает на элемент И 31 (см.фиг.6) и разрешает прохождение синхросерии С1 на входы формирователей 35-37. Формирователь 37 вырабатывает импульс, поступающий на коммутатор 25, и обеспечивает выборку кода числа из накопителя 8 по первому адресу его участка, используемого для работы с данной частью программы. Длительность импульса меньше, чем цикл работы бло ка 3 (меньше 200 не). Формирователи 33, 35 и 38 обеспечивают выработку короткого импульса в конце импульса вырабатьшаемого формирователем 37, что обеспечивает сложение считанного числа в сумматоре 15 по первому входу. После этого может производиться выборка полезной (рабочей) информации из накопителя 8. Формирователи 36, 34 и 39 обеспечивают выработку короткого импульса в начале такта обращения от блока 3 к накопителю 8 (примерно в тот же момент, что и синхросигнал С2). Этот импульс посту пает на входы элементов И 20, 21 и обеспечивает анализ: конечный адрес данного участка накопителя 8 или нет Если нет, то через элемент И 20 в счетчик 30 добавляется единица и цикл выработки очередной микрокоманды повторится аналогично данному. Если конечный адрес достигнут, то с выхода элемента И 21 идет опрос элементов И 22, 23, что означает: равна или не равна сумма в сумматоре 15 контрольному числу для данного участ ка (контрольное число вырабатывается блоком 17). Если равна, то импульс через элемент И 22 поступает на четвертый вход блока 7, что обеспечивает переход счетчика 29 в следующее состояние (следующий участок будет проверяться), а следовательно, преобразователи 28 и 17 выработают новые коды начального, конечного адресов следующего участка и его контрольной суммы, а также установки сумматора 15 в нулевое состояние,а в счетчик 30 записывается первый адрес следующего участка накопителя 8. Затем процедура считывания и определения контрольной суммы повторяется для данного участка. Если после срав нения суммы с контрольным числом выработается сигнал несовпадения, то импульс.через элемент И 23 поступит на установочный вход триггера 24, ко торый изменит свое состояние, дальнейшее поступление импульсов в блок 5 будет установлено, что означает общую остановку работы по определению ошибок, а блок 14 будет индицировать номер участка накопителя 8, в котором имеется ошибка. На контрольном выходе будет присутствовать сигнал ошибка. Формула изобретения 1. Запоминающее устройство с самоконтролем, содержащее генератор импульсов, выход которого подключен к входу первого распределителя импульсов, первый выход которого соединен с входом синхронизации блока: управления, одни из входов которого являются входами устройства, а выходь подключены к одним из входов регистрйГ адреса, выходы которого соединены с входами накопителя, выходы которого подключены к входам регистра микрокоманд, одни из выходов которого соединены с другими входами блока управления, причем входы синхронизации регистра адреса и регистра микрокоманд подключены соответственно к второму и к третьему выходам первого распределителя импульсов, другие выходы регистра микрокоманд являются информационными выходами устройства, отличающееся тем, что, с целью повьш1ения надежности устройства, в него введены блок перебора команд, блок обнаружения ошибок,блок индикации, логический блок, блок местного управления и второй распределитель импульсов, первый вход которого соединен с первым выходом первого распределителя импульсов, первый выход - с первым входом блока перебора команд, а второй вход и второй выход подключены соответственно к первому выходу и к первЙму входу логического блока, второй и третий входы которого соединены соотдетственно с выходом блока обнаружения ошибок и с первым выходом блока местного управления, вход которого подключен к второму выходу первого распределителя импульсов, а второй выход - к второму входу блока перебора команд, третий, четвертый входы и первый управляющий выход которого toединен соответственно с вторым, с третьим выходами и с. четвертым входом логического блока, четвертый выход которого подключен к входу синхронизации блока индикации, входы которого соединены с одними из выхо дов блока перебора команд и одними из входов блока обнаружения ошибок, первый и второй управляющие входы к торого подключены соответственно к третьему выходу второго распределителя импульсов и к второму управляю щему выходу блока перебора команд, другие выходы которого подключены к другим входам регистра адреса, причем другие входы блока обнаружения ошибок соединены с выходами накопителя, четвертый выход логического блока является контрольным выходом устройства. 2.Устройство по п.1, отличающееся тем, что блок обна ружения ошибок содержит сумматор по модулю два, преобразователь кодов контрольных сумм и первую схему срав нения, входы которой соединены соот ветственно с выходами сумматора по модулю два и с выходами преобразова теля кодов контрольных сумм, входы которого являются одними из входов блока, другими входами которого являются входы сумматора по модулю дв другие входы которого и выход перво схемы сравнения являются соответственно первым и вторым управляющими входами и выходом блока. 3.Устройство по ПП.1 и 2, о тличающееся тем, что логический блок содержит триггер, элементы И и элементы НЕ, причем выход и вход первого элемента НЕ подключены соответственно к первым входам первого и второго элементов И, выход второго элемента И соединен с первыми входами третьего и четверто Io элементов И, вторые входы которы подключены соответственно к выходу К входу-второго элемента НЕ, выход четвертого элемента И соединен с установочным входом триггера,- вторые входы первого и второго элементов И объединены и являются первым входом блока, вторым, третьим и четвертым входами которого являются соответственно вход второго элемента НЕ, вход сброса триггера и вход первого элемента НЕ, выходами блока с первого по четвертьш являются соответственно инверсный выход триггера, выход первого и выход второго элементов И и прямой выход триггера. 4. Устройство по ПП.1, 2 и 3, отличающееся тем, что блок перебора команд содержит коммутатор, счетчики, преобразователь кодов адресов, вторую схему сравнения и элемент ИЛИ, причем вход синхронизации коммутатора является первым входом блока, первые входы элемента ИЛИ и первого счетчика объединены и являются вторым входом блока, первый управляющий вход второго счетчика является третьим входом блока, вторые входы первого счетчика и элемента ИЛИ объединены и являются четвертым входом блока, выход элемента ИЛИ соединен с вторым управляющим входом второго счетчика, выходы которого, подключены к входам коммутатора и одним из входов второй схемы сравнения, другие входы которой соединены с одним из выходов преобразователя кодов адресов, другие выходы и входы которого подключены соответственно к входам второго счетчика и к выходам первого счетчика, выходы первого счетчика являются выходами .блока, первым и вторым управляющими входами которого являются соответственно выход второй схемы сравнения и выход элемента ИЛИ. KS кгз(г8,2г) От ;j/«J I 28 К9(Г5) jf i K9(fff) -жOm p 0m 13(22) (put. 5 tput. К7(25)

N

.

2 - Kffff.7(27,29)

KR

ю-W

3ft9)

I

4S

Фи9,8

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем переходов | 1980 |

|

SU966694A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100625A1 |

| УСТРОЙСТВО ОБУЧЕНИЯ ОПЕРАТОРОВ | 1997 |

|

RU2129734C1 |

| Устройство для контроля блоков памяти | 1983 |

|

SU1092569A1 |

| Адаптивное вычислительное устройство | 1980 |

|

SU957214A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для контроля блоков | 1985 |

|

SU1247951A1 |

| Устройство для ввода-вывода информации из накопителей на магнитных дисках | 1982 |

|

SU1019431A1 |

| Запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1317484A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано в системах управления, построенных на основе микропроцессорной техники. Целью изобретения является повышение надежности устройства. Устройство содержит генератор импульсов, распределители импульсов, блок управления, блок местного управления, регистр адреса, блок перебора команд, накопитель, блок обнаружения ошибок, регистр микрокоманд. 3 з.п. ф-лы, В ил.

| Minis et Micros, 1980, 124, p.79-82 | |||

| Прангишвипи И.В | |||

| Микропроцессоры и мшсро-ЭВМ, М.: Энергия, 1979,с.53, рис.2.4. |

Авторы

Даты

1986-11-30—Публикация

1983-04-29—Подача