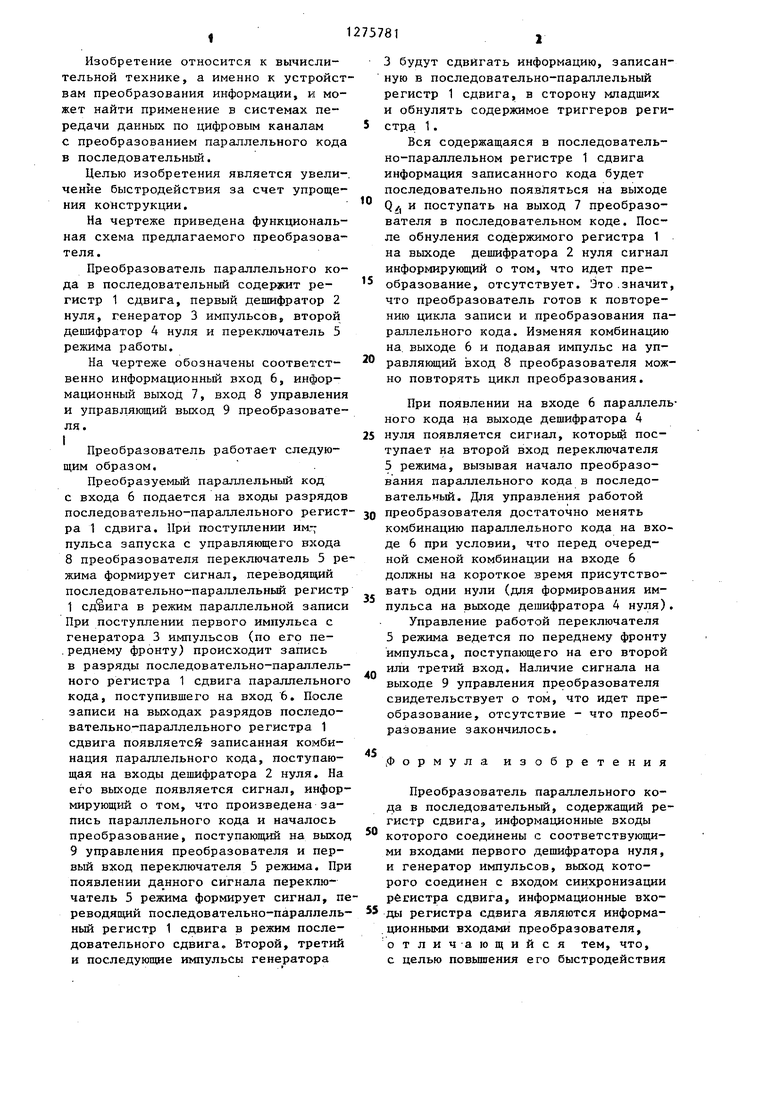

Изобретение относится к вычислительной технике, а именно к устройст вам преобразования информации, и может найти применение в системах передачи данных по цифровым каналам с преобразованием параллельного кода в последовательный. Целью изобретения является увеличенйе быстродействия за счет упрощения конструкции. На чертеже приведена функциональная схема предлагаемого преобразователя . Преобразователь параллельного кода в последовательный содержит регистр 1 сдвига, первый дешифратор 2 нуля, генератор 3 импульсов, второй дешифратор А нуля и переключатель 5 режима работы. На чертеже обозначены соответственно информационньш вход 6, информационный выход 7, вход 8 управления и управляющий выход 9 преобразоватеПреобразователь работает следующим образом. Преобразуемьй параллельный код с входа 6 подается на входы разрядов последовательно-параллельного регист ра 1 сдвига. При поступлении импульса запуска с управляющего входа 8 преобразователя переключатель 5 ре жима формирует сигнал, переводящий последовательно-параллельный регистр 1 сдёига в режим параллельной записи При поступлении первого импульеа с генератора 3 импульсов (по его пе.реднему фронту) происходит запись в разряды последовательно-параллельного регистра 1 сдвига параллельного кода, поступившего на вход 6. После записи на выходах разрядов последовательно-параллельного регистра 1 сдвига появляется записанная комбинация параллельного кода, поступающая на входы дешифратора 2 нуля. На его выходе появляется сигнал, информирующий о том, что произведена запись параллельного кода и началось преобразование, поступающий на выход 9 управления преобразователя и первый вход переключателя 5 режима. При появлении данного сигнала переключатель 5 режима формирует сигнал, пе реводящий последовательно-параллельный регистр 1 сдвига в режим последовательного сдвига. Второй, третий и последующие импульсы генератора 3 будут сдвигать информацию, записанную в последовательно-параллельный регистр 1 сдвига, в сторону младших и обнулять содержимое триггеров регистр.а 1. Вся содержащаяся в последовательно-параллельном регистре 1 сдвига информация записанного кода будет последовательно появляться на выходе Q/, и поступать на выход 7 преобразователя в последовательном коде. После обнуления содержимого регистра 1 на выходе дешифратора 2 нуля сигнал информирующий о том, что идет преобразование, отсутствует. Это .значит, что преобразователь готов к повторению цикла записи и преобразования параллельного кода. Изменяя комбинацию на. выходе 6 и подавая импульс на управляющий вход 8 преобразователя можно повторять цикл преобразования. При появлении на входе 6 параллельного кода на выходе дешифратора 4 нуля появляется сигнал, который поступает на второй вход переключателя 5 режима, вызывая начало преобразования параллельного кода в последовательный. Для управления работой преобразователя достаточно менять комбинацию параллельного кода на входе 6 при условии, что перед очередной сменой комбинации на входе 6 должны на короткое время присутствовать одни нули (для формирования импульса на выходе дешифратора 4 нуля). Управление работой переключателя 5 режима ведется по переднему фронту импульса, поступающего на его второй или третий вход. Наличие сигнала на выходе 9 управления преобразователя свидетельствует о том, что идет преобразование, отсутствие - что преобразование закончилось. 1Формула изобретения Преобразователь параллельного кода в последовательньй, содержащий регистр сдвига, информационные входы которого соединены с соответствующими входами первого дешифратора нуля, и генератор импульсов, выход которого соединен с входом синхронизации регистра сдвига, информационные входы регистра сдвига являются информационными входами преобразователя, отличающийся тем, что, с целью повы1иения его быстродействия

в него введены второй дешифратор нуля и переключатель режима работы, выход которого соединен с входом управления регистра сдвига, информационный выход младшего разряда которого является информационным выходом преобразователя, выход первого дешифратора нуля соединен с первым входом переключателя режима работы и является управляющим выходом преобразователя, информационные входы регистра сдвига объединены с соответствукяцими входами второго дешифратора нуля, выход которого соединен с вторым входом переключателя режима работы, вы ход генератора импульсов соединен с третьим входом переключателя режима работы, четвертый вход которого является входом управления преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИСПРАВЛЯЮЩЕЙ СПОСОБНОСТИ ПРИЕМНИКОВ ДИСКРЕТНЫХ СИГНАЛОВ | 1992 |

|

RU2040118C1 |

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1270897A1 |

| Адаптивный коммутатор системы телеизмерений | 1985 |

|

SU1312629A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

| Преобразователь параллельного кода в последовательный | 1987 |

|

SU1547076A1 |

| Устройство для измерения мощности потерь при коммутации тиристора | 1982 |

|

SU1057891A2 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство сопряжения с магистралью последовательного интерфейса | 1983 |

|

SU1275417A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Многоканальное устройство для регистрации информации | 1984 |

|

SU1236452A1 |

Изобретение относится к вычислительной технике, а именно к устройствам преобразования информации, и может найти применение в системах передачи данных по цифровым каналам с преобразованием параллельного кода в последовательный. Упрощение кон струкции преобразователя обеспечивает преобразование параллельного кода в последовательный без предварительной информации о формате вводного кода, что позволяет повысить его быстродействие. Преобразователь параллельного кода в последовательный содержит регистр сдвига, два дешиф,ратора нуля, генератор импульсов и переключатель режима. 1 ил. (Л Q

9 iH

7Ш

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1159165A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь параллельного кода в последовательный | 1983 |

|

SU1119002A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-07—Публикация

1985-07-11—Подача