Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств обработки дискретной информации.

Цель изобретения - повышение быстродействия преобразователя.

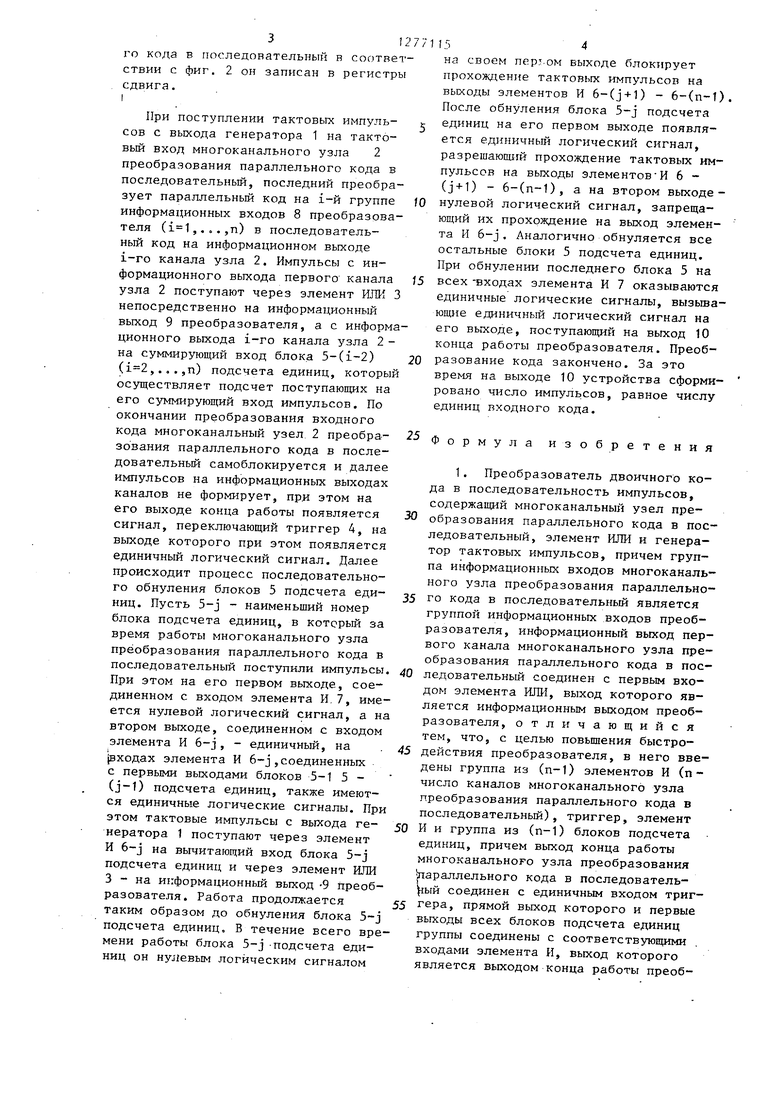

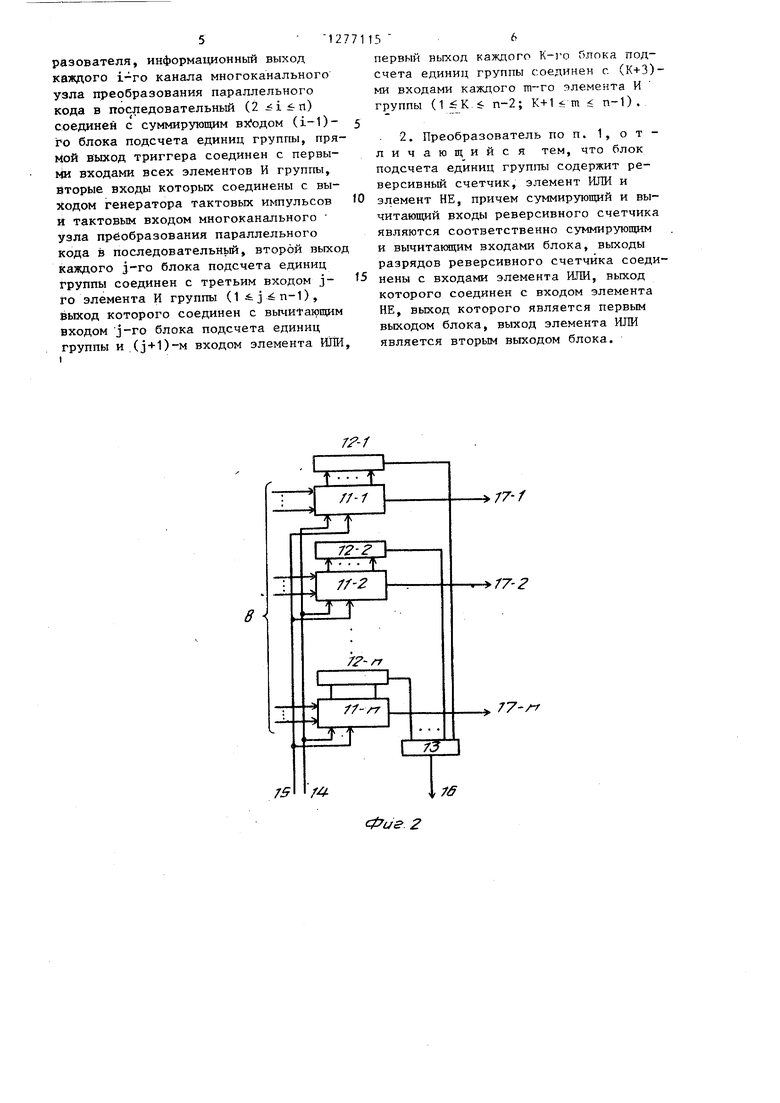

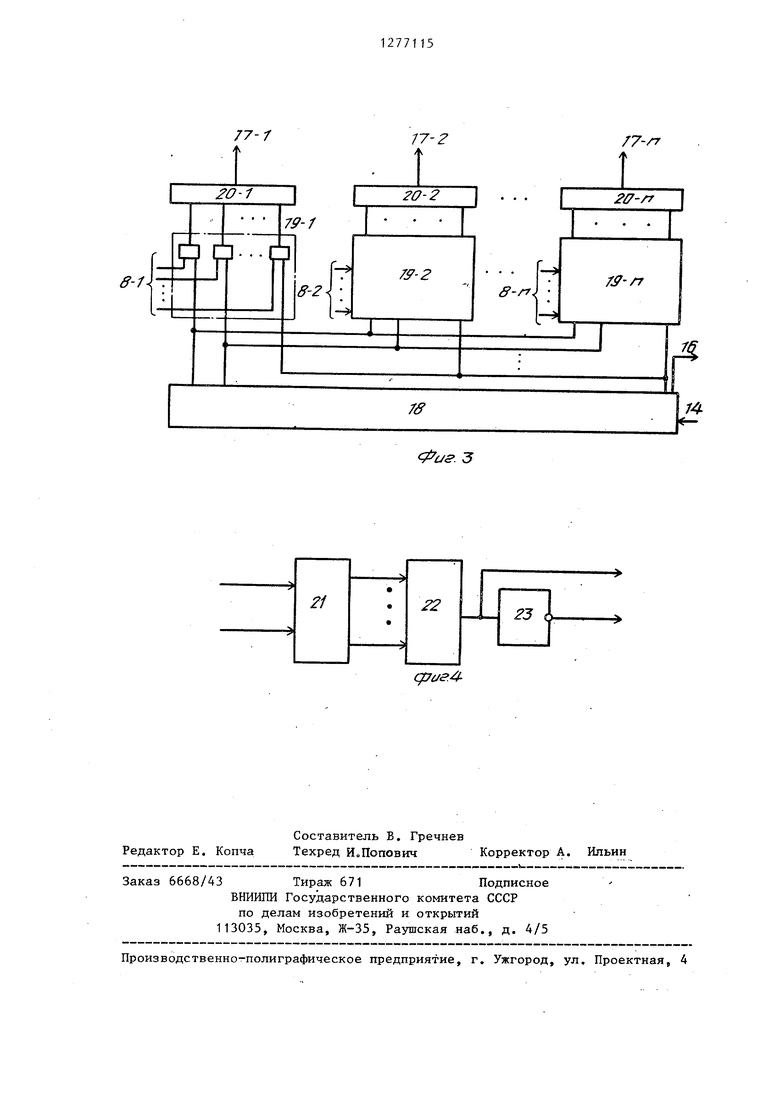

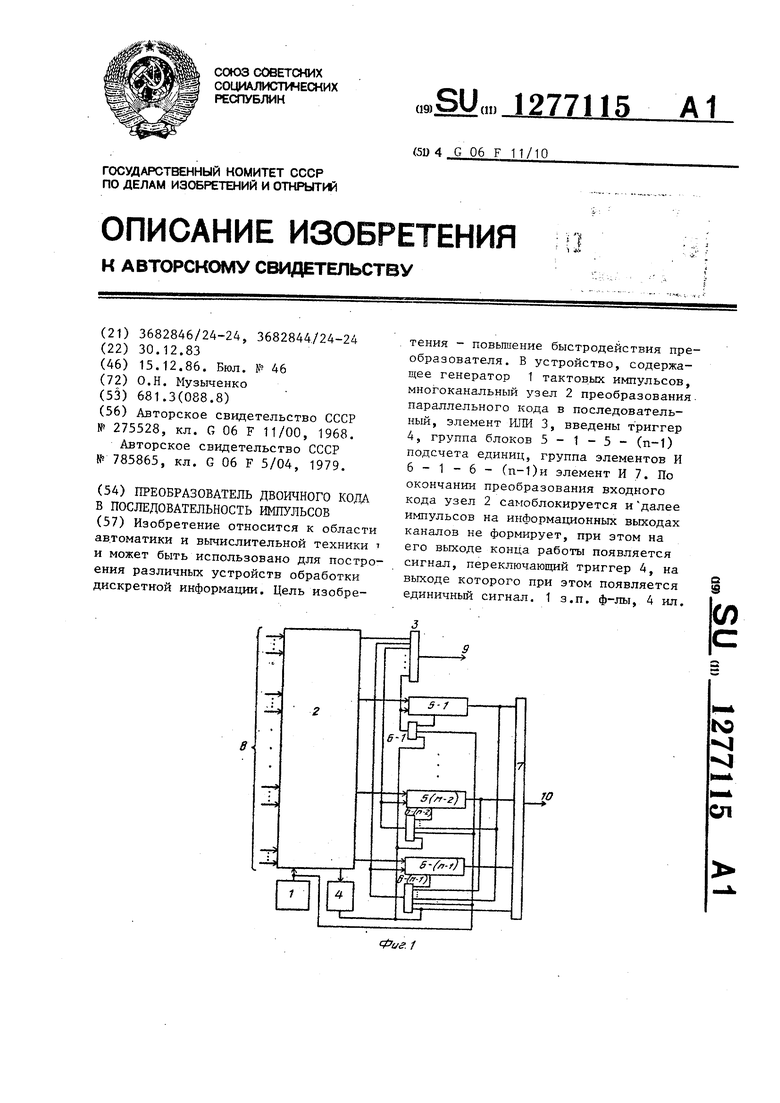

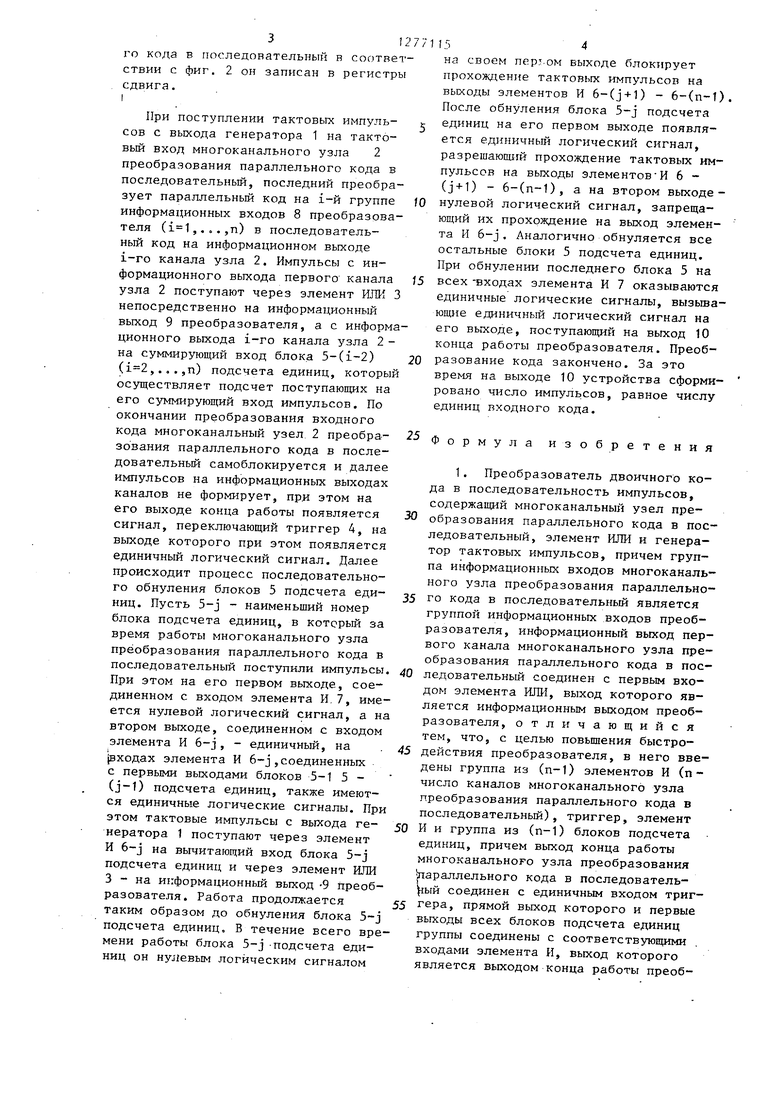

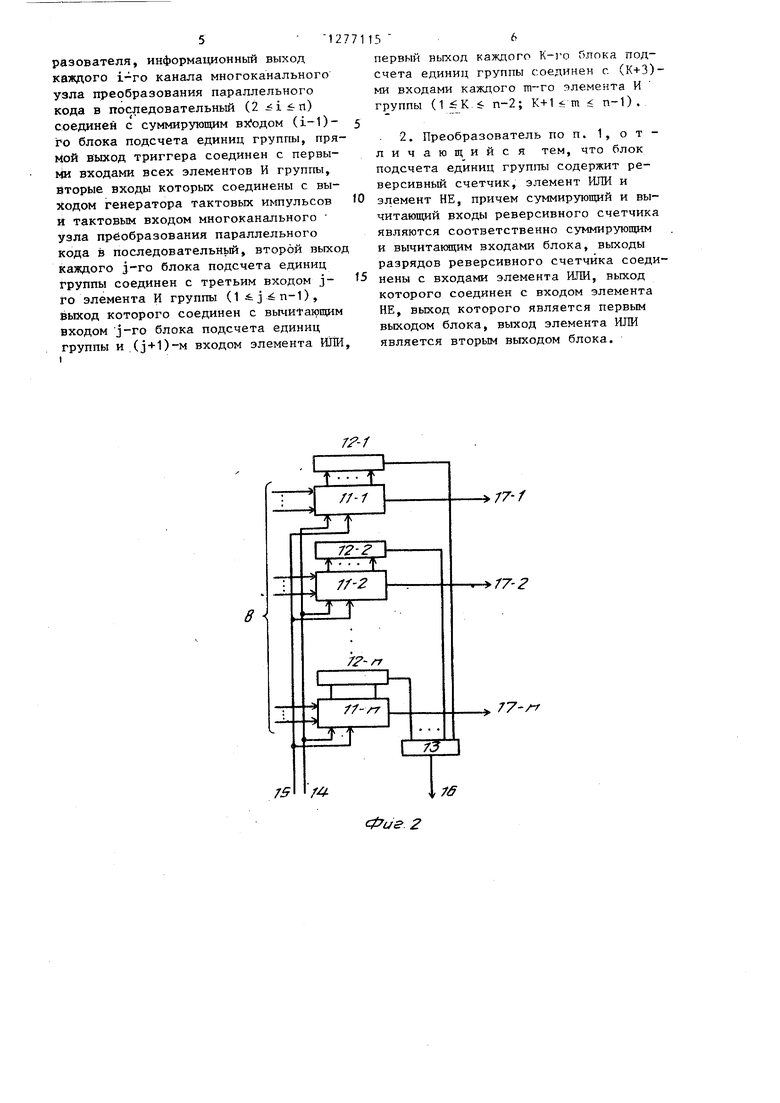

На фиг. 1 изображена структурная схема преобразователя; на фиг. 2 и 3 - структурная схема узла преобразования параллельного кода в последовательность импульсов; на фиг. 4 - структурная схема блока подсчета единиц.

Преобразователь двоичного кода в последовательность импульсов содержит (фиг. 1) генератор 1 тактовых импульсов, многоканальный узел 2 преобразования параллельного кода в последовательный, элемент HIM 3, - триггер 4, группу блоков 5-1 - 5 - (п-1) подсчета единиц,, группу злемен тон И 6-1- - 6 - (п-1), элемент И 7, группу информационных входов 8, информационный выход 9, выход 10 конца работы.

Генератор 1 тактовых импульсов соединен выходом с тактовым входом многоканального узла 2 преобразова- |ния параллельного кода в последовательный, группа информационных входов которого является группой информационных входов 8 преобразователя, выход конца работы многоканального узла преобразования параллельного кода в последовательньш соединен с единичным входом триггера 4, информационный выход первого кана- ла - с первым входом злемента МШ 3, информационный выход i-ro канала () - с суммирующим входом блока 5-(i-1) подсчета единиц, прямой выход триггера 4 соединен с первыми входами всех элементов И 6,, вторые входы которых соединены с выходом генератора 1 тактовых импульсов, второй выход блока 5-J подсчета единиц соединен с третьим входом элемента И 6.J (1 j . п-1), выход которого соединен с вычитающим в:;одом блока 5-J подсчета единиц и (j+1)-M входом элемента ИЛИ 3, первый выход каждого блока подсчета единиц 5-К соединен с ()-ми входами каждого элемента, 6-т (, K+1 m$n-1) .и j-M входом элемента И 7, вход которого соединен с выходом триггера 4, выход элемента ИЛИ 3 соединен

5

0

5

с информационным выходом 9 преобразователя, а выход элемента И 7 - с выходом 10 конца работы преобразова- те.ля.

Многоканальный узел 2 преобразования параллельного кода в последовательный содержит (фиг. 2) регистры 11-1 - 11-п сдвига, элементы И 12-1 - 12-п и элемент И 13, тактовый вход 14, вход 15 разрешения записи, вькод 16 конца работы, группу информационных выходов 17, причем тактовые входы регистров 11 сдвига соединены с тактовым входом 14 узла, а входы разрешения записи - с входом 15 разрешения записи узла, а информационные входы - с информационными входами 8 узла, вькоды (инверсные) разрядов регистра 11-i сдвига (,...,п) -соединены с входами элемента И 12-i, выходы элементов И 12 соединены с входами элемента И 13, выход которого соединен с выходом 16 конца работы узла, выход пер€;носа регистра 11-1 сдвига является информационным выходом 17-1 1-го канала многоканального узла преобразования параллельного кода в последовательный.

Многоканальный узел 2 преобразования параллельного кода в последовательный содержит (фиг. 3) распределитель 18 импульсов, группу эЛемен- .тов И 19-1 - 19-п, группу элементов ИЛИ 20-1 - 20-П5 причем тактовьй

5 вход регистра сдвига соединен с тактовым входом 14 узла, выход его последнего разряда -с выходом 16 конца работы узла, а выходы разрядов - с первыми входами элементов И 19-1 0 19-п групп, вторые входы которых соединены с информационшзми входами 8 узла, а вькоды - с входами элементов ИЛИ 20-1 - 20-п,выход элемента ИЛИ 20-1 является информационным выходом 1 7-1 1-го канала

5 многоканального узла преобразования па,- раллельного кода в последовательный. Блок 5 подсчета единиц содержит реверсивный счетчик 21, элемент ИЖ 22, элемент НЕ 23 (фиг. 4).

Функционирование устройства про0

0

исходит следующим образом.

В исходном состоянии блоки 5 подсчета единиц сброшены, на в.ыходе триггера 4 имеется нулевой логический сигнал. Преобразуемый код подан на информационные входы 8 преобразователя, а при вьтолнении многоканального узла преобразования параллельного кода в последовательный в соотвествии с фиг. 2 он записан в регистр

сдвига.

I

При поступлении тактовых импуль- сов с выхода генератора 1 на тактовый вход многоканального узла 2 преобразования параллельного кода в последовательньш, последний преобразует параллельный код на i-й группе информационных входов 8 преобразователя (,,..,п) в последовательный код на информационном выходе i-ro канала узла 2, Импульсы с информационного выхода первого канала узла 2 поступают через элемент ИЛИ непосредственно на информационный выход 9 преобразователя, а с информционного выхода i-ro канала узла 2 - на суммирующий вход блока 5-(i-2) (,,.,.,п) подсчета единиц, которы осуществляет подсчет поступающих на его суммируюп(ий вход импульсов. По окончании преобразования входного кода многоканальный узел 2 преобра- зования параллельного кода в после- довательньй самоблокируется и далее импульсов на информационных выходах каналов не формирует, прл этом на его выходе конца работы появляется сигнал, переключающий триггер 4, на выходе которого при этом появляется единичный логический сигнал. Далее происходит процесс последовательного обнуления блоков 5 подсчета единиц. Пусть 5-J - наименьший номер блока подсчета единиц, в который за время работы многоканального узла преобразования параллельного кода в последовательный поступили импульсы При этом на его первом выходе, соединенном с входом элемента И,7, имеется нулевой логический сигнал, а н втором выходе, соединенном с входом элемента И 6-j, - единичный, на {входах элемента И 6-j , соединенных с первыми выходами блоков 5-15- (J-1) подсчета единиц, также имеются единичные логические сигналы. При этом тактовые импульсы с выхода генератора 1 поступают через элемент И 6-j на вычитающий вход блока 5-j подсчета единиц и через элемент ИЛИ 3 - на информационный выход -9 преобразователя. Работа продолжается таким образом до обнуления блока 5-j подсчета единиц. В течение всего времени работы блока 5-j -подсчета единиц он нулевым логическим сигналом

на своем пер;.ом выходе блокирует прохождение тактовых импульсов на выходы элементов И 6-(j+1) - 6-(п-1) После обнуления блока 5-j подсчета единиц на его первом выходе появляется единичньй логический сигнал, разрешаюшгй прохождение тактовых импульсов на выходы элементов И 6 - (j + l) - 6-(п-1), а на втором выходе- нулевой логический сигнал, запрещающий их прохождение на выход элемента И 6-j. Аналогично обнуляется все остальные блоки 5 подсчета единиц. При обнулении последнего блока 5 на всех входах элемента И 7 оказываются единичные логические сигналы, вызьша ющие единичный логический сигнал на его выходе, поступающий на выход 10 конца работы преобразователя. Преобразование кода закончено. За это время на выходе 10 устройства сформировано число импульсов, равное числу единиц входного кода.

Формула изобретения

1. Преобразователь двоичного кода в последовательность импульсов, содержащий многоканальный узел преобразования параллельного кода в последовательный, элемент ИЛИ и генератор тактовых импульсов, причем группа информационных входов многоканального узла преобразования параллельного кода в последовательный является группой информационных входов преобразователя, информационный выход первого канала многоканального узла преобразования параллельного кода в последовательный соединен с первым входом элемента ИЛИ, выход которого является информационным выходом преобразователя, отличающийся тем, что, с целью повышения быстродействия преобразователя, в него введены группа из (п-1) элементов И (п- число каналов многоканального узла преобразования параллельного кода в последовательный), триггер, элемент

И и группа из (п-1) блоков подсчета единиц, причем выход конца работы многоканального узла преобразования параллельного кода в последователь- ый соединен с единичным входом триггера, прямой выход которого и первые выходы всех блоков подсчета единиц группы соединены с соответствующими входами элемента И, выход которого вляется выходом конца работы преоб5 427

разователя, информагщонный выход каждого i-ro канала многоканального узла преобразования параллельного кода в последовательньй (2 ) соединен с суммирующим (i-1)- го блока подсчета единиц группы, прямой выход триггера соединен с первыми входами всех элементов И группы, вторые входы которых соединены с выходом генератора тактовых импульсов и тактовым входом многоканального узла преобразования параллельного кода в последовательньй, второй выход каждого j-ro блока подсчета единиц группы соединен с третьим входом j- го элемента И группы (1 ), выход которого соединен с вычитающим входом j-ro блока подсчета единиц группы и (j+1)-M входом элемента ИЛИ,

15 6

первый выход каждого K-i o Г)лока подсчета единиц группы соединен с (К+3)- ми входами каждого га-го злемента И группы (1 :й К п-2; К+1 m п-1) .

2. Преобразователь по п. 1, о т - личающийся тем, что блок подсчета единиц группы содержит реверсивный счетчик, элемент ИЛИ и элемент НЕ, причем суммирующий и вычитающий входы реверсивного счетчика являются соответственно суммирующим и вычитающим входами блока, выходы разрядов реверсивного счетчика соединены с входами элемента ИЛИ, выход которого соединен с входом элемента НЕ, выход которого является первым выходом блока, выход элемента ИЛИ является вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401461A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401464A2 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1438006A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1427574A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1983 |

|

SU1357960A1 |

| Устройство для подсчета числа единиц двоичного кода | 1987 |

|

SU1569995A1 |

| Пороговый элемент | 1986 |

|

SU1387185A2 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для построения различных устройств обработки дискретной информации. Цель изобретения - повышение быстродействия преобразователя. В устройство, содержащее генератор 1 тактов.ых импульсов, многоканальный узел 2 преобразования параллельного кода в последовательный, элемент ШШ 3, введены триггер 4, группа блоков 5 - 1 - 5 - (п-1) подсчета единиц, группа элементов И 6 - 1 - 6 - (п-1)и элемент И 7. По окончании преобразования входного кода узел 2 самоблокируется и далее импульсов на информационных выходах каналов не формирует, при этом на его выходе конца работы появляется сигнал, переключающий триггер 4, на выходе которого при этом появляется единичный сигнал. 1 з.п. ф-лы, 4 ил. сл Ю ел

в

75 /

77-/

77,./

Фиг 2

77-7

J

1

гО-2

в-ПW l

: fi-2

8-2

77-Z

/71

I

7ff-2

&-rr

/У-/7

re

/4

с/г. 3

cp(j.4

| УСТРОЙСТВО для КОНТРОЛЯ двоичных кодовпо МОДУЛЮ 2 т+1 | 0 |

|

SU275528A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для преобразования параллельного кода в последовательный | 1979 |

|

SU785865A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-15—Публикация

1983-12-30—Подача