1 127

Изобретение относится к вычислительной технике и может быть использовано для отладки программ и сбора статистических данных о динамических параметрах структур программ, выпол- няемых на электронных вычислительных машинах.

Цель изобретения - расширение функциональных возможностей устройства за счет регистрации кода команды перехода, количества выполненных команд в цикле и на линейном участке, времени выполнения цикла и линейного участка.

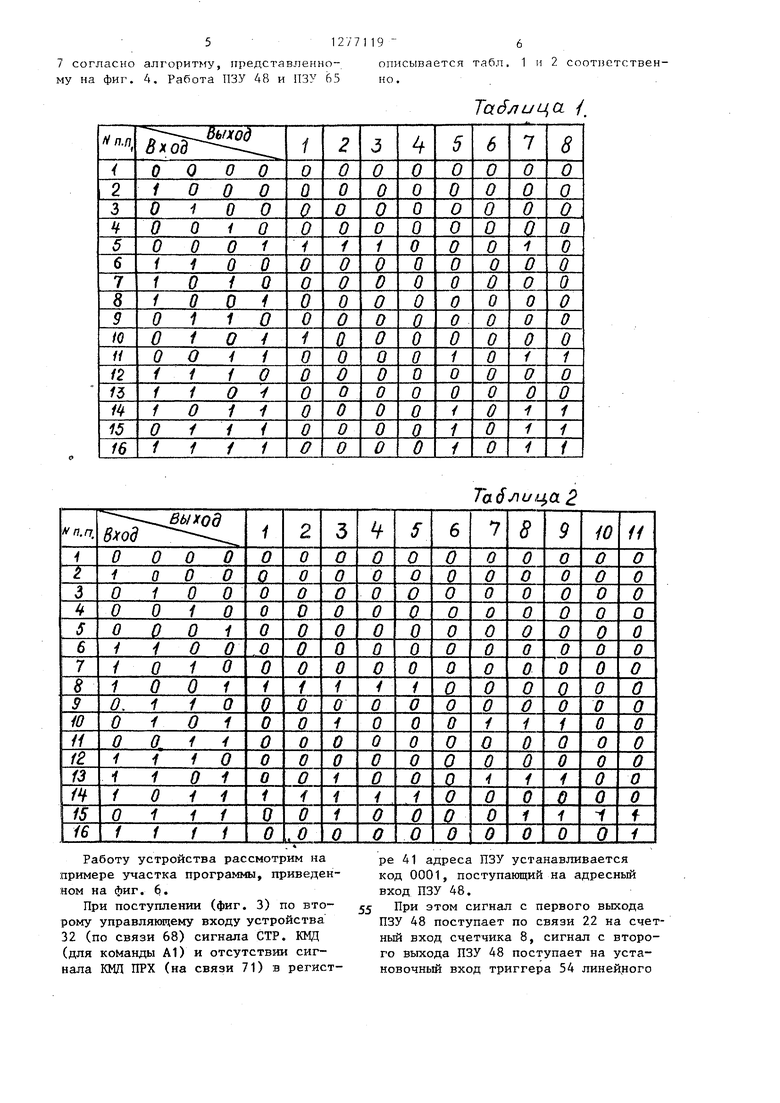

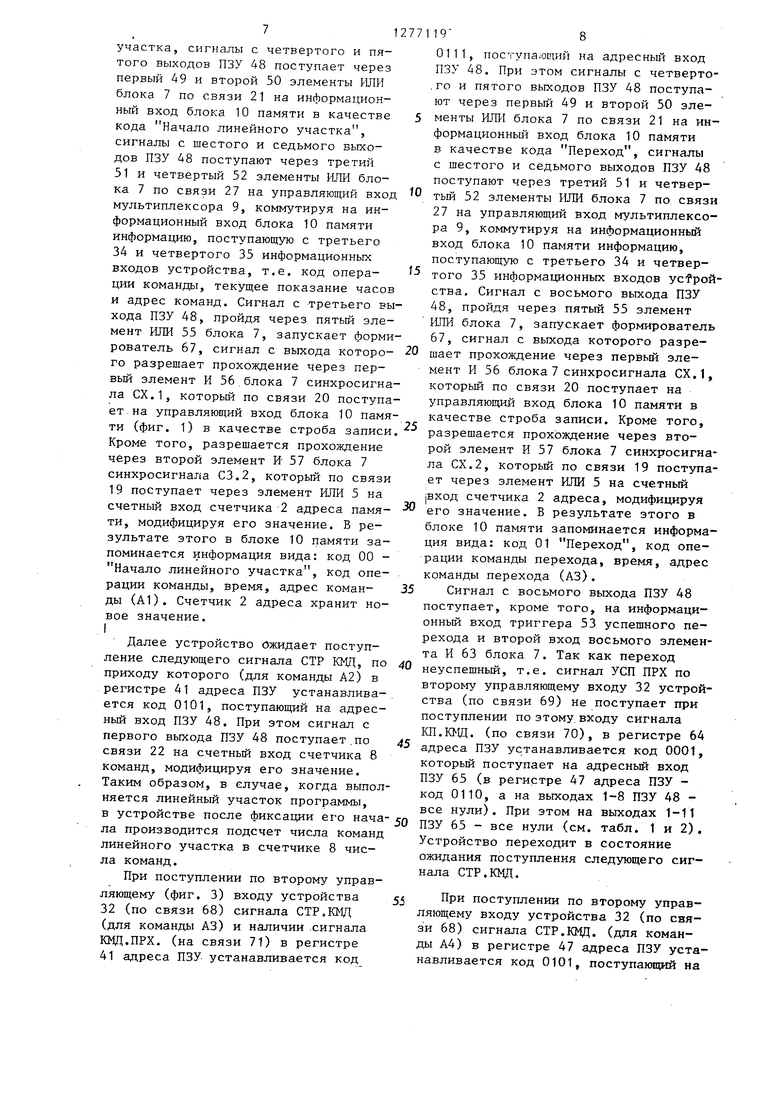

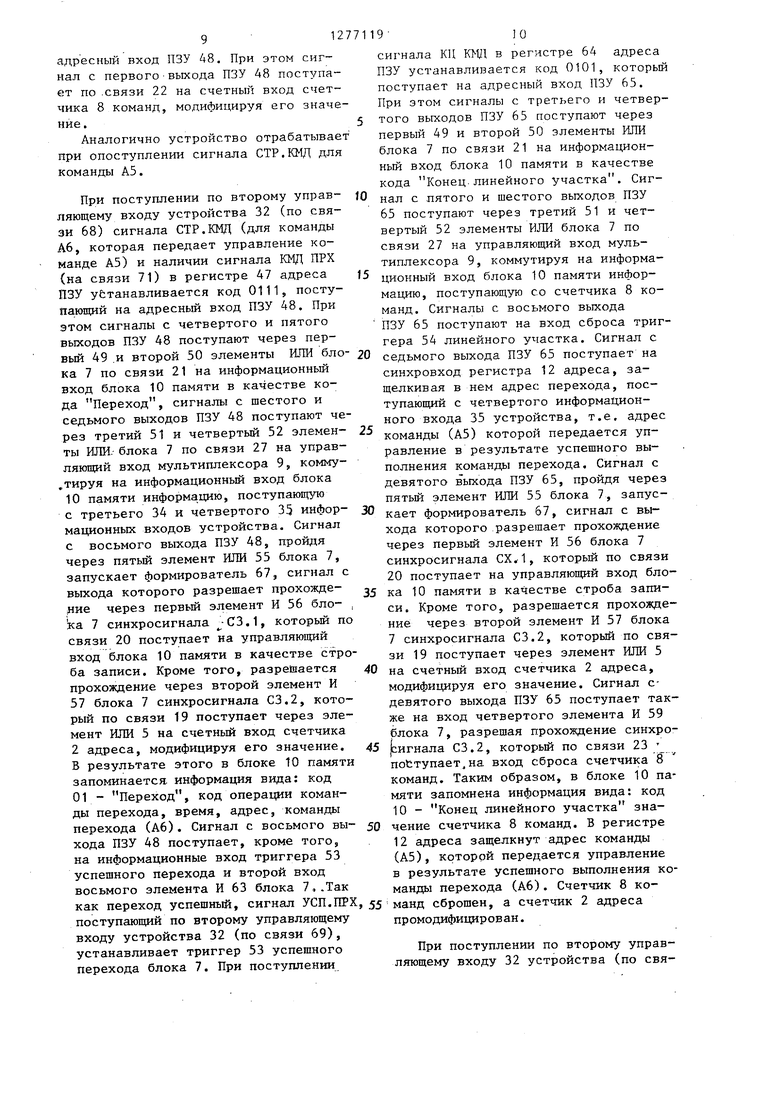

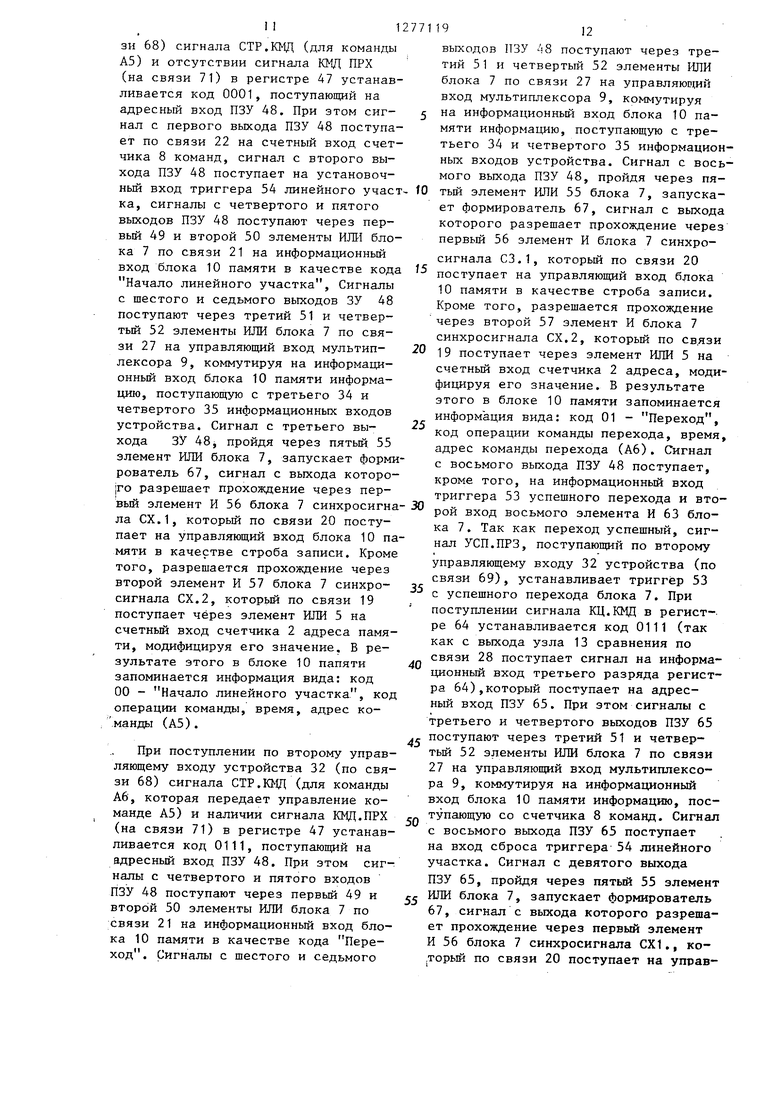

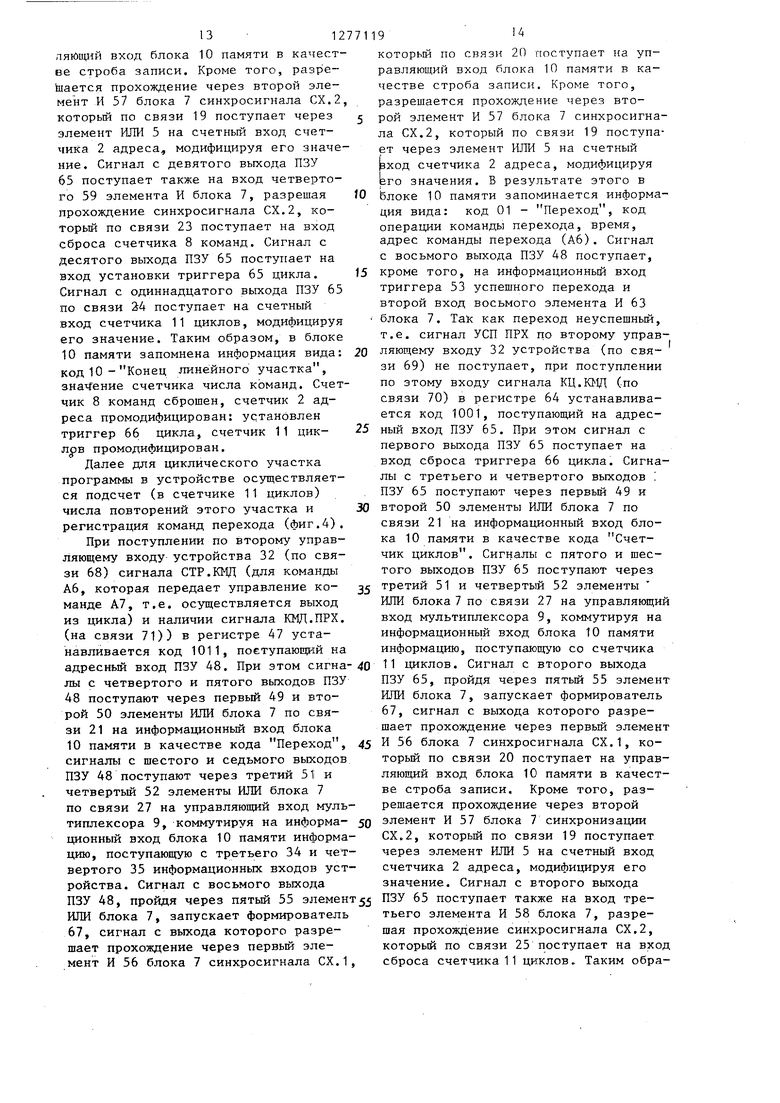

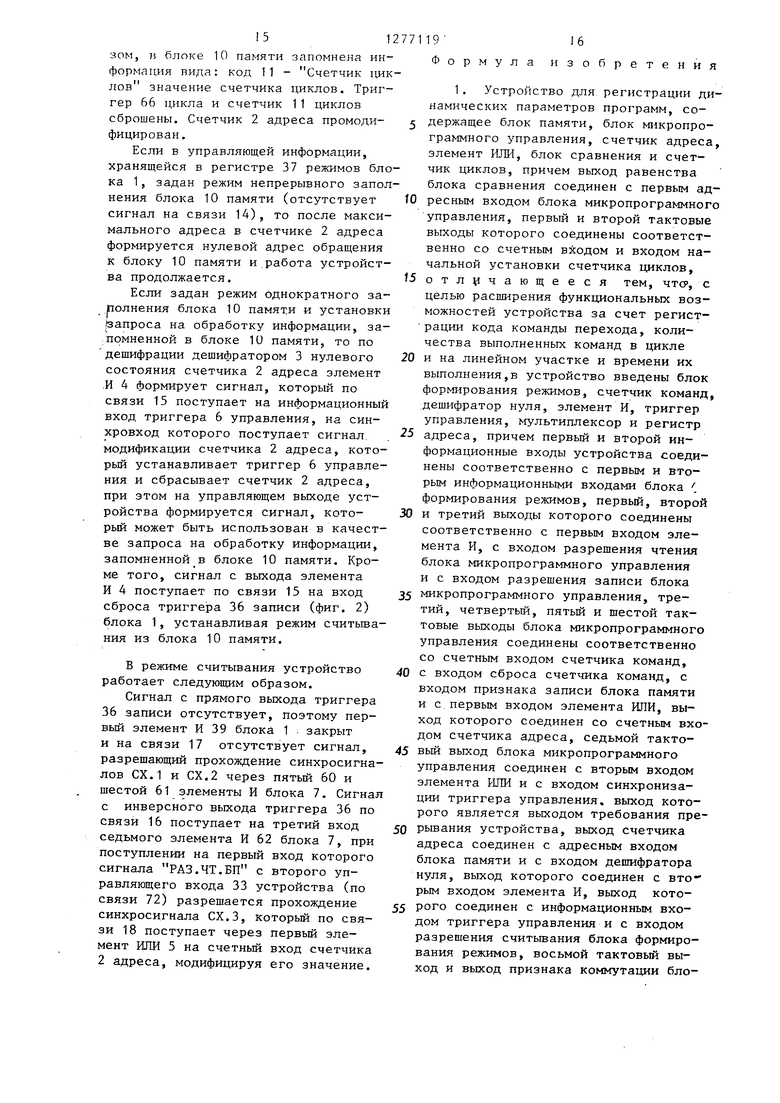

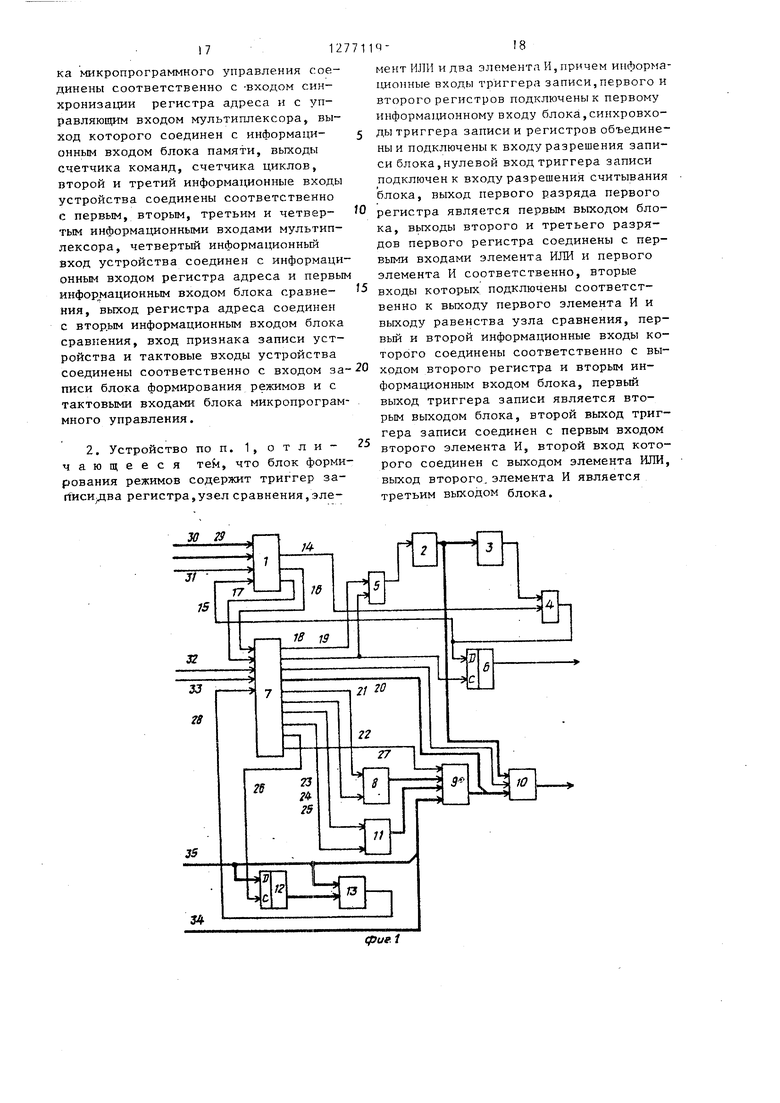

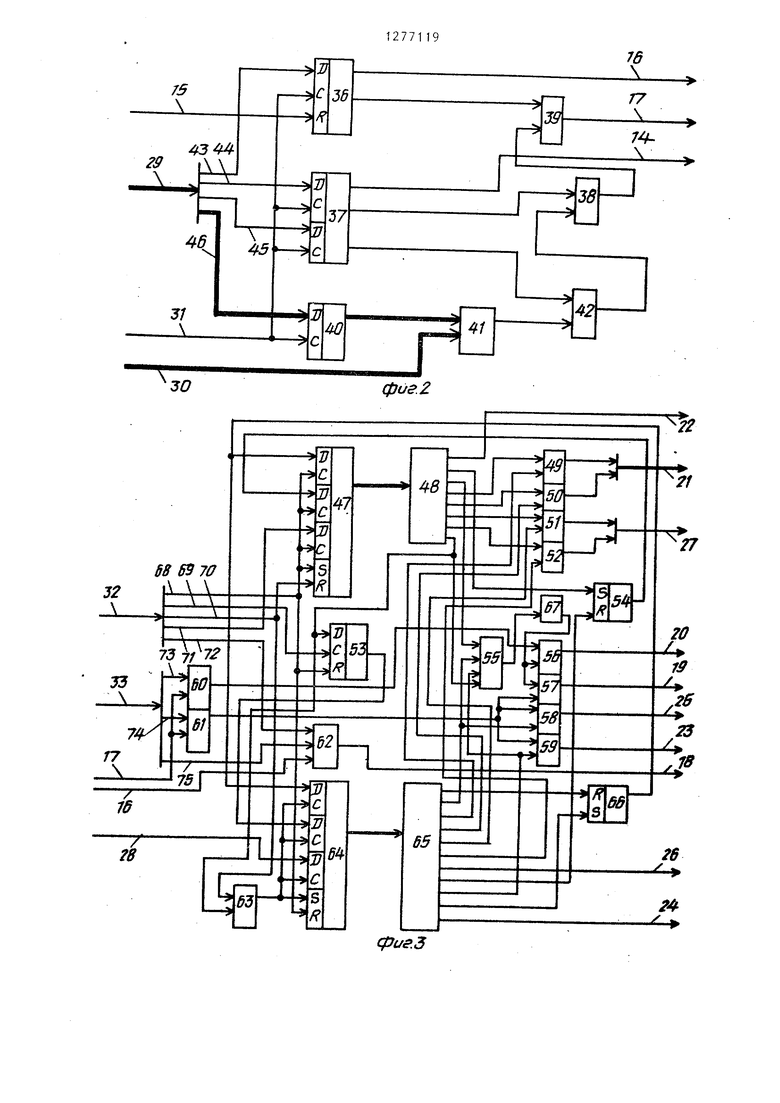

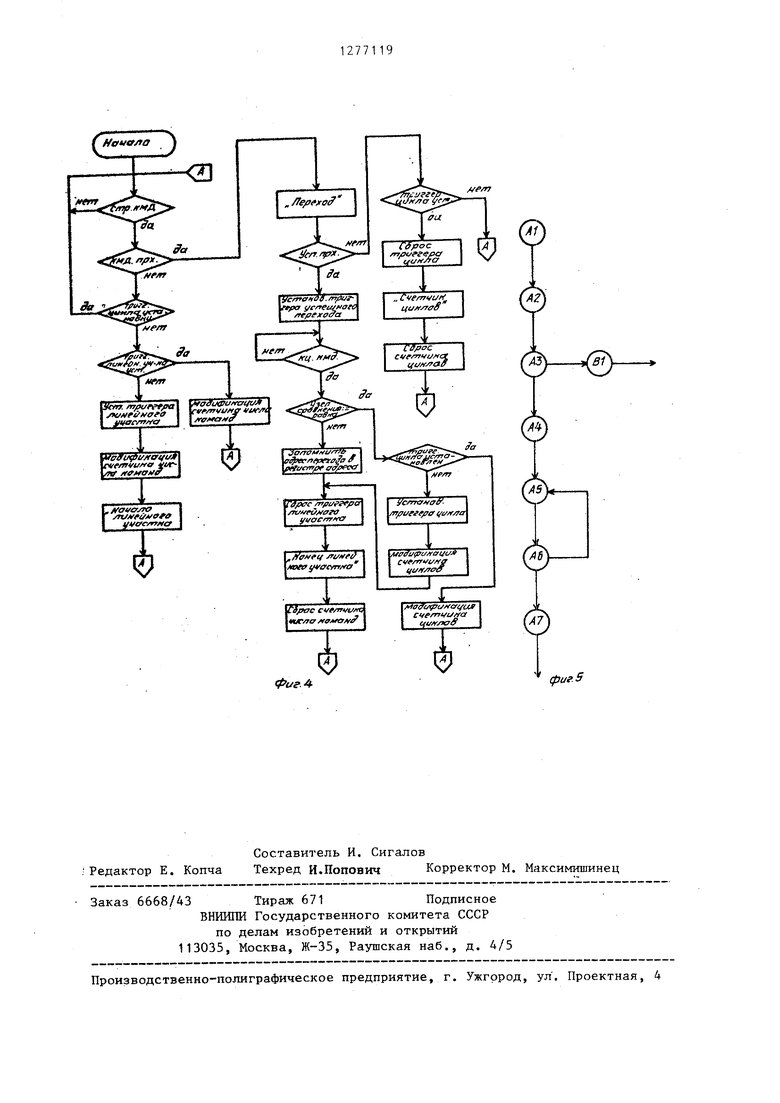

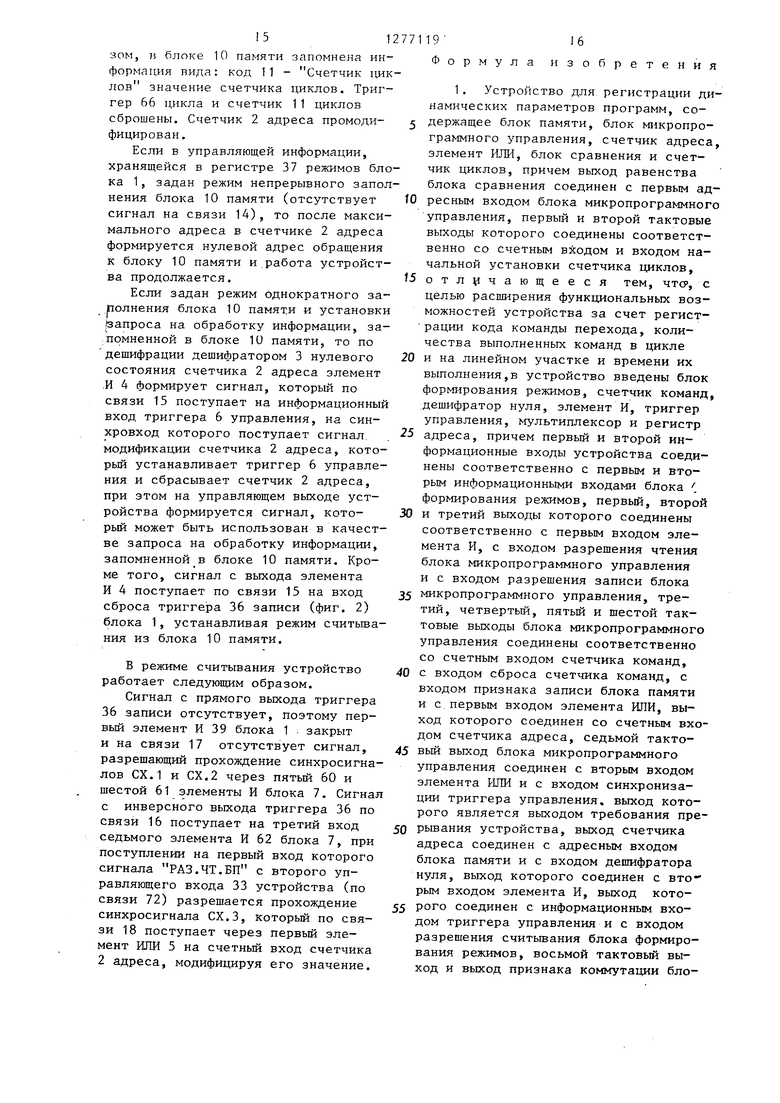

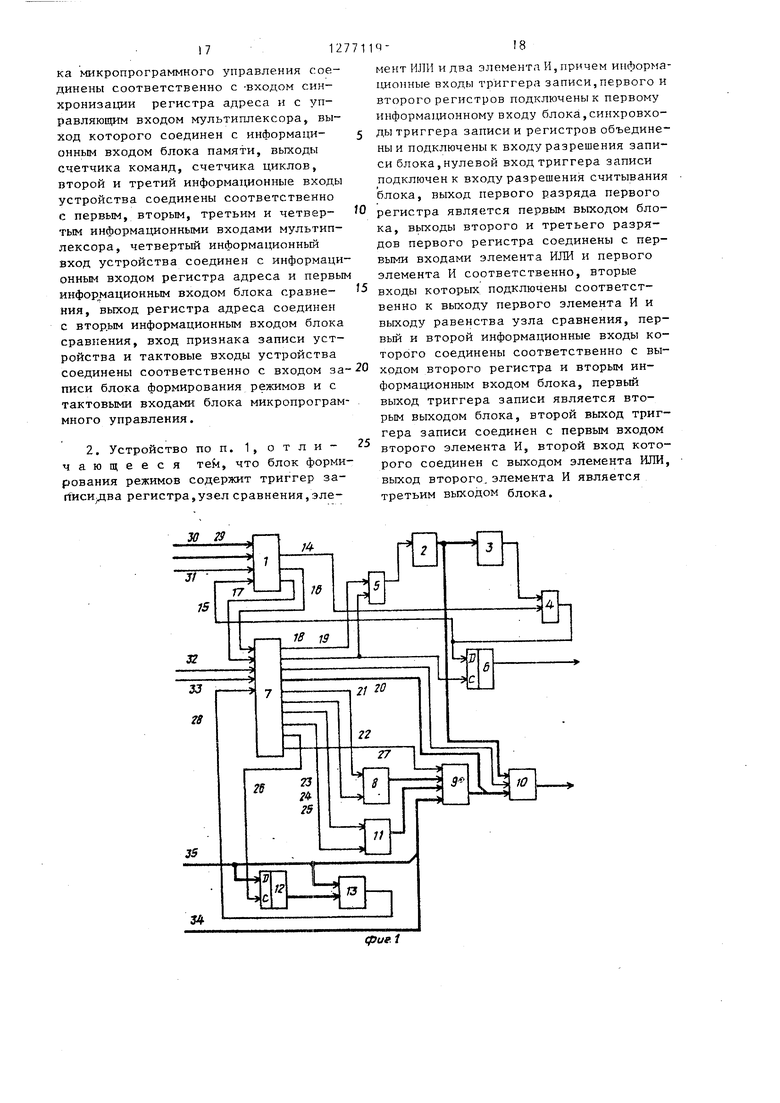

На фиг. 1 изображена функционашь- Иая схема устройства; на фиг. 2 - )функционалЬная схема блока формирования режимов; на фиг. 3 - функциональная схема блока микропрограммного управления; на фиг. 4 - алгоритм ра- боты устройства; на фиг. 5 - пример участка программы.

Устройство для регистрации динамических параметров программ (фиг.1) содержит блок 1 формирования режимов, Счетчик 2 адреса, дешифратор 3 нуля, элемент И 4, элемент ИЛИ 5, триггер 6 управления, блок 7 микропрограммного управления, счетчик 8 команд, мультиплексор 9, блок 10 памяти, . счетчик 11 циклов, регистр 12 адреса, блок 13 сравнения, выход 14 блока 1 - признак непрерывного заполнения блока памяти, выход 15 элемента И 4 , выход 16 блока 1 выход 17 блока 1 - разрешение регистрации, тактовые выходы 18 и 19 блока 7, выход 20 - признак записи, выход 21 - коды начала линейного учйстка, тактовые выходы 22 - 26 блока 7 микропрог- раммного управления, управляющий вход 27 мультиплексора 9, выход 28 блока 13 сравнения, первый 29 и второй 30 информационные входы устройства, вход 31 признака записи устройст- за, первый 32 и второй 33 тактовые входы устройства, третий 34 и четвертый 35 информационные входы устройства.

Блок 1 (фиг. 2) содержит триггер

36 записи, первый регистр 37, элемент ИЛИ 38, первый элемент И 39, второй регистр 40, узел 41 сравнения, второй элемент И 42, информационные вхо- ды A3 - 46 блока 1 (линии и связи).

Блок 7 микропрограммного управления (фиг. 3) содержит регистр 47 адреса первого ПЗУ, первое ПЗУ 48,

0

5

11

5

О

35

50

„

30

92

первый 49, второй 50, третий 51, четвертый 52 элементы ШИ, триггер 53 успешного перехода, триггер 54 линейного участка, пятый элемент ИЛИ 55, первый 56, второй 57, третий 58, четвертый 59, пятый 60, шестой 61, седьмой 62 и восьмой 63 элементы И, регистр 64 адреса второго ПЗУ, второе ПЗУ 65, триггер 66 цикла, формирователь 67, информационные и тактовые входы 68-75 (линии и связи).

На первый информационный вход 29 устройства в блок 1 (фиг.2) поступают следуюш;ие сигналы режимов: по линии 43 - сигнал режима работы блока 10 памяти (ЗП) по линии 44 - сигнал режима однократного заполнения блока 10 памяти (ОД.ЗШ1), по линии 45 - сигнал режима работы устройстзза по любой программе (любой)., по линии 46 - код ключа защиты исследуемой программы.

На первый управляющий вход 31 устройства в блок 1 поступает строб за- Ииси информации в триггер 36 записи, регистр 37 и регистр 40.

На второй информационный вход устройства 30 в блок 1 поступает код ключа защиты текущей программы.

На второй управляюш-ий вход 32 устройства в блок 7 (фиг. 3) поступают следующие сигналы управления: по линии 68 - сигнал строба команды (СТР. КМД), по линии 69 - сигнал признака успешного перехода (УСП ПРХ), по линии 70 - сигнал признака конца команды (КЦ КМД), по линии 71 - сигнал признака команды перехода (КМД.ПРХ), по линии 72 - сигнал разрешения чтения блока 10 памяти (РАЗ.ЧТ.ВЦ).

На третий управляющий вход устройства 33 в блок 7 управления поступают следующие сигналы: по линии 73 - первый синхросигнал (СХ.1), цо линии 74 - второй синхросигнал (СХ.2), по линии 75 - третий синхросигнал (СХ.З).

На третий информационный вход 34 устройства (фиг. 1) поступают код операции и текущее значение часов процессора.

На четвертый информационный вход 35 устройства поступает текущий адрес команды.

Блок 1 формирования режимов предназначен для обеспечения режимов работы устройства и выработки ряда управляющих сигналов.

Счетчик 2 адреса памяти формирует адрес обращения к блоку 10 памяти.

312

Дешифратор 3 нуля служит для вьфа ботки сигнала признака нулевого состояния счетчика 2 адреса памяти.

Триггер 6 управления предназначен для временного хранения признака то- го, что блок 10 памяти заполнен и своим выходом подключен к управляющему выходу устройства.

Блок 7 микропрограммного управления обеспечивает разворот временной диаграммы устройства.

Счетчик 8 команд предназначен для подсчета числа команд на линейном участке программы.

Счетчик 11 циклов подсчитывает число повторений циклических участков программы.

Регистр 12 адреса служит для записи и временного хранения адреса перехода .

Блок 13 сравнения обеспечивает поразрядное сравнение содержимого регистра 12 адреса и текущего значения адреса команды.

Мультиплексор 9 предназначен для коммутации информационных потоков с выхода счетчика 8 команд, счетчика 11 циклов или четвертого 35 и третьего 34 информационных входов устройст |ва на вход блока 10 памяти.

Блок 10 памяти необходим для записи и временного хранения регистрируемых данных.

Триггер 36 записи (фиг. 2) предназначен для обеспечения режима за- писи или чтения блока 10 памяти.

Регистр 37 обеспечивает режим однократного либо непрерывного заполнения блока памяти и режим работы по ключу защиты программы.

Регистр 40 предназначен для записи и хранения ключа защиты исследуемой программы.

Узел 41 сравнения осуществляет поразрядное сравнение ключа защиты текущей программы и ключа защиты исследуемой программы.

Первый элемент И 39, элемент ИЛИ 38 и второй элемент И 42 предназначены для выработки сигнала разрешения работы синхросигналов СХ.1 и СХ 2.

Регистр адреса первого ПЗУ 47 и регистр адреса второго ПЗУ 64 предназначены для формирования и времен- кого хранения адресов соответственно первого 48 и второго 65 ПЗУ.

Первое ПЗУ 48, первый 49, второй 50, третий 51, четвертый 52, пятый

19 -4

55 элемент ИЛИ, первый 56, второй 57, третий 58, четвертый 59, пятьш 60, шестой 61, седьмой 62 и восьмой 63 элеметы И, второе ПЗУ 65, формирователь 67 осуществляют выработку управляющих сигналов, обеспечивающих работу устройства.

Триггер 53 успешного перехода служит для хранения признака команды с успешным переходом.

Триггер 54 линейного участка предназначен для хранения признака линейного участка программы.

Триггер 66 цикла предназначен для хранения признака циклического участка программы.

Устройство работает следующим образом.

В исходном состоянии все триггеры, регистры и счетчики обнулены (цепи сброса не показаны).

Устройство может работать в режиме записи информации в блок 10 памяти или в режиме считьшания информации из блока 10 памяти (фиг. 1).

В режиме записи перед началом- работы в блоке 1 по первому информационному входу 29 устройства при наличии строба записи на первом управляющем входе устройства 31 устанавливается управляющая информация, определяющая режим работы устройства, реакцию на заполнение блока 10 памяти, номер ключа защиты исследуемой программы, В случае, когда в регистре 37 (фиг. 2) установлен режим регистрации по конкретному коду ключа защиты, узел 41 сравнения сравнивает установленный в регистре 40 код с кодом ключа заш;иты текущей программы, поступающим по второму информационному входу 30 устройства. Если сравнение произошло, то на третьем управляющем выходе 17 блок 1 появляется сигнал, который поступает в блок 7 (фиг. 3), разрешая прохождение первого и второго синхросигналов, поступающих с третьего управляющего входа 33 устройства, через пятый 60 и шестой 61 элементы И блока случае, когда в регистре 37 (фиг. 2) установлен режим регистрации по любому коду ключа защиты, сигнал на третьем управляющем выходе 17 блока 1 появляется независимо от результата работы узла 41 сравнения.

Далее устройство в режиме записи функционирует-под управлением блока

51277)19 6

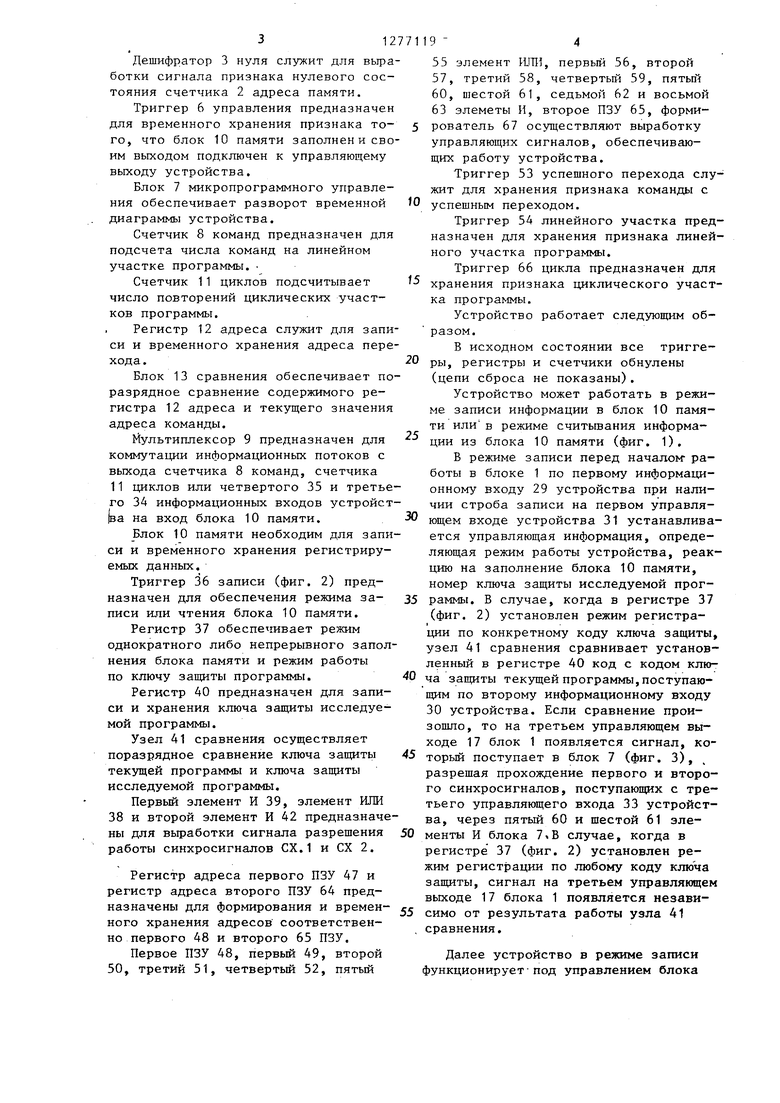

7 согласно алгоритму, представленно- описывается табл. 1 н 2 соотвстствен- му на фиг. 4. Работа ПЗУ 48 и ПЗУ 65 но..

Работу устройства рассмотрим на примере участка программы, приведенном на фиг. 6.

При поступлении (фиг. 3) по второму управляющему входу устройства 32 (по связи 68) сигнала СТР. КМД (для команды А1) и отсутствии сигнала КМД ПРХ (на связи 71) в регистТаблии а /,

. 2

ре 41 адреса ПЗУ устанавливается код 0001, поступающий на адресный вход ПЗУ 48.

55 При этом сигнал с первого выхода ПЗУ 48 поступает по связи 22 на счетный вход счетчика 8, сигнал с второго выхода ПЗУ 48 поступает на установочный вход триггера 54 линейного

участка, сигналы с четвертого и пятого выходов ПЗУ 48 поступает через первый 49 и второй 50 элементы ИЛИ блока 7 по связи 21 на информационный вход блока 10 памяти в качестве кода Начало линейного участка, сигналы с шестого и седьмого выходов ПЗУ 48 поступают через третий 51 и четвертый 52 элементы ИЛИ блока 7 по связи 27 на управляющий вход мультиплексора 9, коммутируя на информационный вход блока 10 памяти информацию, поступающую с третьего 34 и четвертого 35 информационных входов устройства, т.е. код опера- ции команды, текущее показание часов и адрес команд. Сигнал с третьего выхода ПЗУ 48, пройдя через пятый элемент ИЛИ 55 блока 7, запускает формирователь 67, сигнал с выхода которо- го разрешает прохождение через первый элемент И 56 блока 7 синхросигнала СХ.1, который по связи 20 поступает на управляющий вход блока 10 памяти (фиг. 1) в качестве строба записи Кроме того, разрешается прохождение через второй элемент И 57 блока 7 синхросигнала С3.2, который по связи 19 поступает через элемент ИЛИ 5 на счетный вход счетчика 2 адреса памя- ти, модифицируя его значение. В результате этого в блоке 10 памяти запоминается информация вида: код 00 - Начало линейного участка, код one- рации команды, время, адрес коман- ды (А1). Счетчик 2 адреса хранит новое значение. I

Далее устройство ожидает поступление следующего сигнала СТР ЩЦ, по приходу которого (для команды А2) в регистре 41 адреса ПЗУ устанавливается код 0101, поступающий на адресный вход ПЗУ 48. При этом сигнал с первого выхода ПЗУ 48 поступает.по связи 22 на счетный вход счетчика 8 команд, модифицируя его значение. Таким образом, в случае, когда выполняется линейный участок программы, в устройстве после фиксации его нача ла производится подсчет числа команд линейного участка в счетчике В числа команд.

При поступлении по второму управляющему (фиг. 3) входу устройства 32 (по связи 68) сигнала СТР.КМД (для команды A3) и наличии .сигнала ЩЦ.ПРХ. (на связи 71) в регистре 41 адреса ПЗУ устанавливается код

0111, поступаюпщй на адресный вход ПЗУ 48. При этом сигналы с четверто- . го и пятого выходов ПЗУ 48 поступают через первый 49 и второй 50 элементы ИЛИ блока 7 по связи 21 на информационный вход блока 10 памяти в качестве кода Переход, сигналы с шестого и седьмого выходов ПЗУ 48 поступают через третий 51 и четвертый 52 элементы РШИ блока 7 по связи 27 на управляющий вход мультиплексора 9, коммутируя на информационный вход блока 10 памяти информацию, поступающую с третьего 34 и четвертого 35 информационных входов ycfpoft- ства. Сигнал с восьмого выхода ПЗУ 48, пройдя через пятый 55 элемент РШИ блока 7, запускает формирователь 67, сигнал с выхода которого разрешает прохождение через первый элемент И 56 блока 7 синхросигнала СХ.1, который по связи 20 поступает на управляющий вход блока Ю памяти в качестве строба записи. Кроме того, разрешается прохождение через второй элемент И 57 блока 7 синхросигнала СХ.2, который по связи 19 поступает через элемент ИЛИ 5 на счетный |вход счетчика 2 адреса, модифицируя его значение. В результате этого в блоке 10 памяти запоминается информация вида: код 01 Переход, код операции команды перехода, время, адрес команды перехода (A3).

Сигнал с восьмого выхода ПЗУ 48 поступает, кроме того, на информационный вход триггера 53 успешного перехода и второй вход восьмого элемента И 63 блока 7. Так как переход неуспешный, т.е. сигнал УСП ПРХ по второму управляющему входу 32 устройства (по связи 69) не поступает при поступлении по этому входу сигнала KП.. (по связи 70), в регистре 64 адреса ПЗУ устанавливается код 0001, который поступает на адресньй вход ПЗУ 65 (в регистре 47 адреса ПЗУ - код 0110, а на выходах 1-8 ПЗУ 48 - все нули). При этом на выходах 1-11 ПЗУ 65 - все нули (см. табл. 1 и 2). Устройство переходит в состояние ожидания поступления следующего сигнала СТР.КМД.

При поступлении по второму управляющему входу устройства 32 (по связи 68) сигнала СТР.КМД. (для команды А4) в регистре 47 адреса ПЗУ устанавливается код 0101, поступающий на

912

адресный вход ПЗУ 48. При этом сигнал с первоговыхода ПЗУ 48 поступа- ет по .связи 22 на счетный вход счетчика 8 команд, модифицируя его значение.

Аналогично устройство отрабатывае при опоступлении сигнала СТР.КМД для команды А5.

При поступлении по второму управ- ляющему входу устройства 32 (по связи 68) сигнала СТР.КМД (для команды А6, которая передает управление команде А5) и наличии сигнала КМД ПРХ {на связи 71) в регистре 47 адреса ПЗУ уЬтанавливается код 0111, поступающий на адресный вход ПЗУ 48. При этом сигналы с четвертого и пятого выходов ПЗУ 48 поступают через первый 49 .и второй 50 элементы ИЛИ бло ка 7 по связи 21 на информационный вход блока 10 памяти в качестве кода Переход, сигналы с шестого и седьмого выходов ПЗУ 48 поступают через третий 51 и четвертьш 52 элемен- ты ИЛИ. блока 7 по связи 27 на управляющий вход мультиплексора 9, комму- .,тируя на информационный вход блока 10 памяти информацию, поступающего с третьего 34 и четвертого 35 инфор- мационных входов устройства. Сигнал с восьмого выхода ПЗУ 48, пройдя через пятый элемент ИЛИ 55 блока 7, запускает формирователь 67, сигнал с выхода которого разрешает прохозкде- ние через первый элемент И 56 бло- ка 7 синхросигнала С3.1, который по связи 20 поступает на управляющий вход блока 10 памяти в качестве строба записи. Кроме того, разрешается прохождение через второй элемент И 57 блока 7 синхросигнала С3.2, который по связи 19 поступает через элемент ИЛИ 5 на счетный вход счетчика 2 адреса, модифицируя его значение. В результате этого в блоке 10 памяти запоминается, информация вида: код 01 - Переход, код операции команды перехода, время, адрес, команды перехода (А6). Сигнал с восьмого вы- хода ПЗУ 48 поступает, кроме того, на информационные вход триггера 53 успешного перехода и второй вход восьмого элемента И 63 блока 7,.Так как переход успешный, сигнал УСП.ПРХ поступающий по второму управляющему входу устройства 32 (по связи 69), устанавливает триггер 53 успешного перехода блока 7. При поступлении

9-10

сигнала КЦ КМЛ в регистре 64 адреса ПЗУ устанавливается код 0101, который поступает на адресный вход ПЗУ 65. При этом сигналы с третьего и четвертого выходов ПЗУ 65 поступают через первый 49 и второй 50 элементы ИЛИ блока 7 по связи 21 на информационный вход блока 10 памяти в качестве кода Конец.линейного участка. Сигнал с .пятого и шестого выходов ПЗУ 65 поступают через третий 51 и четвертый 52 элементы ИЛИ блока 7 по связи 27 на управляющий вход мультиплексора 9, коммутируя на информационный вход блока 10 памяти информацию, поступающую со счетчика 8 команд. Сигналы с восьмого выхода ПЗУ 65 поступают на вход сброса триггера 54 линейного участка. Сигнал с седьмого выхода ПЗУ 65 поступает на синхровход регистра 12 адреса, защелкивая в нем адрес перехода, поступающий с четвертого информационного входа 35 устройства, т.е. адрес команды (А5) которой передается управление в результате успешного выполнения команды перехода. Сигнал с девятого выхода ПЗУ 65, пройдя через пятьм элемент ИЛИ 55 блока 7, запускает формирователь 67, сигнал с выхода которого разрешает прохождение через первый элемент И 56 блока 7 синхросигнала СХ.1, который по связи 20 поступает на управляющий вход блока 10 памяти в качестве строба записи. Кроме того, разрешается прохождение через второй элемент И 57 блока 7 синхросигнала СЭ.2, который по связи 19 поступает через элемент ИЛИ 5 на счетный вход счетчика 2 адреса, модифицируя его значение. Сигнал с- девятого выхода ПЗУ 65 поступает также на вход четвертого элемента И 59 блока 7, разрешая прохождение синхро- ригнала С3.2, которьй по связи 23 пойтупает на вход сброса счетчика 8 команд. Таким образом, в блоке 10 памяти запомнена информация вида: код 10 - Конец линейного участка значение счетчика 8 команд. В регистре 12 адреса защелкнут адрес команды (А5), Которой передается управление в результате успешного выполнения команды перехода (А6). Счетчик 8 команд сброшен, а счетчик 2 адреса промодифицирован.

При поступлении по второму управ- Л5пощему входу 32 устройства (по свя1 1

зи 68) сигнала СТР.КМД (для команды А5) и отсутствии сигнала КМД ПРХ (на связи 71) в регистре 47 устанавливается код 0001, поступающий на адресный вход ПЗУ 48. При этом сиг- нал с первого выхода ПЗУ 48 поступает по связи 22 на счетный вход счетчика 8 команд, сигнал с второго выхода ПЗУ 48 поступает на установочный вход триггера 54 линейного участ ка, сигналы с четвертого и пятого выходов ПЗУ 48 поступают через первый 49 и второй 50 элементы ИЛИ блока 7 по связи 21 на информационный вход блока 10 памяти в качестве кода Начало линейного участка. Сигналы с шестого и седьмого выходов ЗУ 48 поступают через третий 51 и четвертый 52 элементы ИЛИ блока 7 по связи 27 на управляющий вход мультип- лексора 9, коммутируя на информационный вход блока 10 памяти информацию, поступающую с третьего 34 и четвертого 35 информационных входов устройства. Сигнал с третьего вы- хода ЗУ 48j пройдя через пятый 55 элемент ИЛИ блока 7, запускает формирователь 67, сигнал с выхода которо- |го разрешает прохождение через первый элемент И 56 блока 7 синхросигна ла СХ.1, который по связи 20 поступает на управляющий вход блока 10 памяти в качестве строба записи. Кроме того, разрешается прохождение через второй элемент И 57 блока 7 синхро- сигнала СХ.2, который по связи 19 поступает через элемент ИЛИ 5 на счетный вход счетчика 2 адреса памяти, модифицируя его значение, В результате этого в блоке 10 папяти запоминается информация вида: код 00 - Начало линейного участка, код операции команды, время, адрес ко- манды (А5).

При поступлении по второму управляющему входу устройства 32 (по связи 68) сигнала СТР.КМД (для команды А6, которая передает управление команде А5) и наличии сигнала КМД.ПРХ (на связи 71) в регистре 47 устанавливается код 0111, поступающий на адресный вход ПЗУ 48. При этом сигналы с четвертого и пятого входов ПЗУ 48 поступают через первый 49 и второй 50 элементы ИЛИ блока 7 по связи 21 на информационный вход блока 10 памяти в качестве кода Переход . Сигналы с шестого и седьмого

1912

выходов ПЗУ 48 поступают через третий 51 и четвертый 52 элементы ИЛИ блока 7 по связи 27 на управляювщй вход мультиплексора 9, коммутируя на информационный вход блока 10 памяти информацию, поступающую с третьего 34 и четвертого 35 информационных входов устройства. Сигнал с восьмого выхода ПЗУ 48, пройдя через пятый элемент ИЛИ 55 блока 7, запускает формирователь 67, сигнал с выхода которого разрешает прохождение через первый 56 элемент И блока 7 синхросигнала С3.1, который по связи 20 поступает на управляющий вход блока 10 памяти в качестве строба записи. Кроме того, разрешается прохождение через второй 57 элемент И блока 7 синхросигнала СХ.2, которьш по связи 19 поступает через элемент ИЛИ 5 на счетный вход счетчика 2 адреса, модифицируя его значение. В результате этого в блоке 10 памяти запоминается информация вида: код 01 - Переход, код операции команды перехода, время адрес команды перехода (А6). Сигнал с восьмого выхода ПЗУ 48 поступает, кроме того, на информационный вход триггера 53 успешного перехода и второй вход восьмого элемента И 63 блока 7. Так как переход успешный, сигнал УСП.ПРЗ, поступающий по второму

управляющему входу 32 устройства (по связи 69), устанавливает триггер 53 с успешного перехода блока 7. При поступлении сигнала КЦ.КМД в регистре 64 устанавливается код 0111 (так как с выхода узла 13 сравнения по связи 28 поступает сигнал на информационный вход третьего разряда регистра 64),который поступает на адресный вход ПЗУ 65. При этом сигналы с третьего и четвертого выходов ПЗУ 65 поступают через третий 51 и четвертый 52 элементы ИЛИ блока 7 по связи 27 на управляющий вход мультиплексора 9, коммутируя на информационный вход блока 10 памяти информацию, поступающую со счетчика 8 команд. Сигнал с восьмого выхода ПЗУ 65 поступает на вход сброса триггера 54 линейного участка. Сигнал с девятого выхода ПЗУ 65, пройдя через пятый 55 элемент ИЛИ блока 7, запускает формирователь 67, сигнал с выхода которого разрешает прохождение через первый элемент И 56 блока 7 синхросигнала СХ1., ко- .торый по связи 20 поступает на управ13 12

nniouj ifi вход блока 10 памяти в качестве строба записи. Кроме того, paapie- Шается прохождение через второй элемент И 57 блока 7 синхросигнала СХ.2, который по связи 19 поступает через элемент ИЛИ 5 на счетный вход счетчика 2 адреса, модифицируя его значение. Сигнал с девятого выхода ПЗУ 65 поступает также на вход четвертого 59 элемента И блока 7, разрешая прохождение синхросигнала СХ.2, который по связи 23 поступает на вход сброса счетчика 8 команд. Сигнал с десятого выхода ПЗУ 65 поступает на вход установки триггера 65 цикла. Сигнал с одиннадцатого выхода ПЗУ 65 по связи 24 поступает на счетный вход счетчика 11 циклов, модифицируя его значение. Таким образом, в блоке 10 памяти запомнена информация вида: код 10 - Конец линейного участка, счетчика числа команд. Счетчик 8 команд сброшен, счетчик 2 адреса промодифицирован: установлен триггер 66 цикла, счетчик 11 цик- лрв промодифидирован.

Далее для циклического участка программы в устройстве осуществляется подсчет (в счетчике 11 циклов) числа повторений этого участка и регистрация команд перехода (фиг,4). При поступлении по второму управляющему входу устройства 32 (по связи 68) сигнала СТР.КМД (для команды А6, которая передает управление ко- манде А7, т,е. осуществляется выход из цикла) и наличии сигнала КМД.ПРХ. (на связи 71)) в регистре 47 устанавливается код 1011, поступающий на адресный вход ПЗУ 48, При этом сигна лы с четвертого и пятого выходов ПЗУ 48 поступают через первый 49 и второй 50 элементы ИЛИ блока 7 по связи 21 на информационный вход блока 10 памяти в качестве кода Переход, сигналы с шестого и седьмого выходов ПЗУ 48 поступают через третий 51 и четвертый 52 элементы ИЛИ блока 7 по связи 27 на управляющий вход мультиплексора 9, коммутируя на информа- ционный вход блока 10 памяти информацию, поступающую с третьего 34 и четвертого 35 информационных входов устройства. Сигнал с восьмого выхода ПЗУ 48, пройдя через пятый 55 элемен ИЛИ блока 7, запускает формирователь 67, сигнал с выхода которого разрешает прохождение через первый элемент И 56 блока 7 синхросигнала СХ,1

91

который по связи 20 поступает на управляющий вход блока 10 памяти в качестве строба записи. Кроме того, разрешается прохождение через второй элемент И 57 блока 7 синхросигнала СХ,2, который по связи 19 поступает через элемент ЩЖ 5 на счетный вход счетчика 2 адреса, модифицируя его значения, В результате этого в блоке 10 памяти запоминается информация вида: код 01 - Переход, код операции команды перехода, время, адрес команды перехода (А6). Сигнал с восьмого выхода ПЗУ 48 поступает, кроме того, на информационный вход триггера 53 успешного перехода и второй вход восьмого элемента И 63

блока 7, Так как переход неуспешный, т,е, сигнал УСП ПРХ до второму управляющему входу 32 устройства (по свя- зи 69) не поступает, при поступлении по этому входу сигнала КЦ,К1 Щ (по связи 70) в регистре 64 устанавливается код 1001, поступающий на адресный вход ПЗУ 65, При этом сигнал с первого выхода ПЗУ 65 поступает на вход сброса триггера 66 цикла. Сигналы с третьего и четвертого выходов . ПЗУ 65 поступают через первый 49 и второй 50 элементы ИЛИ блока 7 по связи 21 на информационный вход блока 10 памяти в качестве кода Счетчик циклов, Сигналы с пятого и шестого выходов ПЗУ 65 поступают через третий 51 и четвертый 52 элементы ИЛИ блока 7 по связи 27 на управляющий вход мультиплексора 9, коммутируя на информационный вход блока 10 памяти информацию, поступающую со счетчика 11 циклов. Сигнал с второго выхода ПЗУ 65, пройдя через пятый 55 элемент ИЛИ блока 7, запускает формирователь 67, сигнал с выхода которого разрешает прохождение через первый элемент И 56 блока 7 синхросигнала СХ.1, который по связи 20 поступает на управ- ляюш;ий вход блока 10 памяти в качестве строба записи. Кроме того, разрешается прохождение через второй элемент И 57 блока 7 синхронизации СХ.2, который по связи 19 поступает через элемент ИЛИ 5 на счетный вход счетчика 2 адреса, модифицируя его значение. Сигнал с второго выхода ПЗУ 65 поступает также на вход третьего элемента И 58 блока 7, разрешая прохождение синхросигнала СХ,2, который по связи 25 поступает на вход сброса счетчика 11 циклов. Таким обра 512

зом, в блоке 10 памяти запомнена информация вида: код 11 - Счетчик циклов значение счетчика циклов. Триггер 66 цикла и счетчик 11 циклов сброшены. Счетчик 2 адреса промоди- фицирован.

Если в управляющей информации, хранящейся в регистре 37 режимов блока 1, задан режим непрерывного заполнения блока 10 памяти (отсутствует сигнал на связи 14), то после максимального адреса в счетчике 2 адреса формируется нулевой адрес обращения к блоку 10 памяти и работа устройства продолжается.

Если задан режим однократного заполнения блока 10 памяти и установки запроса на обработку информации, запомненной в блоке 10 памяти, то по дешифрации дешифратором 3 нулевого состояния счетчика 2 адреса элемент .И 4 формирует сигнал, который по связи 15 поступает на информационный вход триггера 6 управления, на син

хровход которого поступает сигнал.

модификации счетчика 2 адреса, который устанавливает триггер 6 управления и сбрасывает счетчик 2 адреса, при этом на управляющем выходе устройства формируется сигнал, кото- рый может быть использован в качестве запроса на обработку информации, запомненной в блоке 10 памяти. Кроме того, сигнал с выхода элемента И 4 поступает по связи 15 на вход сброса триггера 36 записи (фиг. 2) блока 1, устанавливая режим считьгоа ния из блока 10 памяти.

В режиме считывания устройство работает следующим образом.

Сигнал с прямого выхода триггера 36 записи отсутствует, поэтому первый элемент И 39 блока 1 . закрыт и на связи 17 отсутствует сигнал, разрешающий прохождение синхросигналов СХ.1 и СХ.2 через пятый 60 и шестой 61 элементы И блока 7. Сигна с инверсного выхода триггера 36 по связи 16 поступает на третий вход седьмого элемента И 62 блока 7, при поступлении на первый вход которого сигнала РАЗ.ЧТ.БП с второго управляющего входа 33 устройства (по связи 72) разрешается прохождение синхросигнала СХ.З, которьш по связи 18 поступает через первый элемент ИЛИ 5 на счетный вход счетчика 2 адреса, модифицируя его значение.

O -5

0

5

0 5

0

5 0

19 16

Формула изобретения

1. Устройство для. регистрации динамических параметров программ, содержащее блок памяти, блок мнкропро- rpaNWHoro управления, счетчик адреса, элемент ИЛИ, блок сравнения и счетчик циклов, причем выход равенства блока сравнения соединен с первым адресным входом блока микропрограммного управления, первый и второй тактовые выходы которого соединены соответственно со счетным входом и входом начальной установки счетчика циклов, oтл чaющeecя тем, ЧТСР, с целью расширения функциональных возможностей устройства за счет регистрации кода команды перехода, количества выполненных команд в цикле и на линейном участке и времени их выполнения,в устройство введены блок формирования режимов, счетчик команд, дешифратор нуля, элемент И, триггер управления, мультиплексор и регистр адреса, причем первый и второй информационные входы устройства соединены соответственно с первым и вторым информационными входами блока -1 формирования режимов, первый, второй и третий выходы которого соединены соответственно с первым входом элемента И, с входом разрешения чтения блока микропрограммного управления и с входом разрешения записи блока микропрограммного управления, третий, четвертый, пятый и шестой тактовые выходы блока микропрограммного управления соединены соответственно со счетным входом счетчика команд, с входом сброса счетчика команд, с входом признака записи блока памяти и с первым входом элемента ИЛИ, выход которого соединен со счетным входом счетчика адреса, седьмой такто- вьм выход блока микропрограммного управления соединен с вторым входом элемента ИЛИ и с входом синхронизации триггера управления, выход которого является выходом требования прерывания устройства, выход счетчика адреса соединен с адресным входом блока памяти и с входом дешифратора нуля, выход которого соединен с вторым входом элемента И, выход которого соединен с информационным входом триггера управления и с входом разрешения считывания блока формирования режимов, восьмой тактовый выход и выход признака коммутации бло17

12771

ка микропрограммного управления соединены соответственно с -входом синхронизации регистра адреса и с управляющим входом мультиплексора, выход которого соединен с информационным входом блока памяти, выходы Счетчика команд, счетчика циклов, второй и третий информационные входы устройства соединены соответственно с первым, вторым, третьим и четвертым информационными входами мультиплексора, четвертый информационный вход устройства соединен с информационным входом регистра адреса и первым

информационным входом блока сравнения, выход регистра адреса соединен с втор.ым информационным входом блока сравнения, вход признака записи устройства и тактовые входы устройства соединены соответственно с входом записи блока формирования режимов и с тактовыми входами блока микропрограммного управления.

2. Устройство по п. 1, о т л и - чающееся тей, что блок формирования режимов содержит триггер за- г1йси ва регистра,узел сравнения,эле

5

0

5

iq-18

ИЛИ и два элемента И, причем ииформа- 1щонные входы триггера записи,первого и второго регистров подключены к первому информагщонному входу блока,синхровхо- ды триггера записи и регистров объединены и подключены к входу разрешения записи блока,нулевой вход триггера записи подключен к входу разрешения считывания блока, выход первого разряда первого регистра является первым выходом блока, вьгходы второго и третьего разрядов первого регистра соединены с первыми входами элемента ИЛИ и первого элемента И соответственно, вторые входы которых подключены соответственно к выходу первого элемента И и выходу равенства узла сравнения, первый и второй информационные входы которого соединены соответственно с выходом второго регистра и вторым информационным входом блока, первый выход триггера записи является вторым выходом блока, второй выход триггера записи соединен с первым входом второго элемента И, второй вход которого соединен с выходом элемента ИЛИ, выход второго.элемента И является третьим выходом блока.

30

фае. 2

сригЗ

(

Начало

За

9а

toyif t//(aFifi/M

- «1ЛГ

Г

t

ffiac cvf/yTvt//ai

«/Ur/rcr ffOMOff

фиг. 4Ф

меа7

f/rtA

фиг 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для запоминания состояний процессора | 1985 |

|

SU1278858A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство управления загрузкой микропрограмм | 1983 |

|

SU1119019A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1170457A1 |

Изобретение относится к области вычислительйой техники и предназначено для отладки программ и сбора статистических данных о динамических параметрах структур программ, выполняемых на электронных вычислительных машинах. Цель изобретения - расширение функциональных возможностей устройства за счет регистрации кода команды перехода, количества выполняемых команд в цикле и линейном участке, времени выполнения цикла и линейного участка. Устройство для регистрации динамических параметров структур программ содержит блок памяти и счетчик циклов. Сущность изобретения заключается в том, что для любого участка программы (линейного или цикла) фиксируются не только его границы в адресном пространстве программы с подсчетом , но также и код команды перехода, количество выполненных команд и время выполнения участка. С этой целью устройство дополнительно содержит блок формирования режимов, счетчик адреса памяти, дешифратор нуля, элемент И, элемент ИЛИ, триггер управления, блок управления, счетчик числа команд, мультиплексор, регистр адерса и узел сравнения. 2 табл., 1 з.п. ф-лы. 5 ил § сл to ч|

Редактор Е. Копча

Составитель И. Сигалов

Техред И.Попович Корректор М. Максимишинец

Заказ 6668/43 Тираж 671Подписное

ВНИИ1Ш Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул . Проектная, 4

| Авторское свидетельство СССР № 913386, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля хода программ | 1980 |

|

SU1057949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-15—Публикация

1985-05-07—Подача