ел

оэ

Ј

00

4

СО

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная вычислительная система | 1985 |

|

SU1277129A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Система сбора и обработки информации | 1987 |

|

SU1424024A1 |

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| Многопроцессорная система | 1988 |

|

SU1605247A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Устройство управления сегментированной памятью многопроцессорной системы | 1990 |

|

SU1753477A1 |

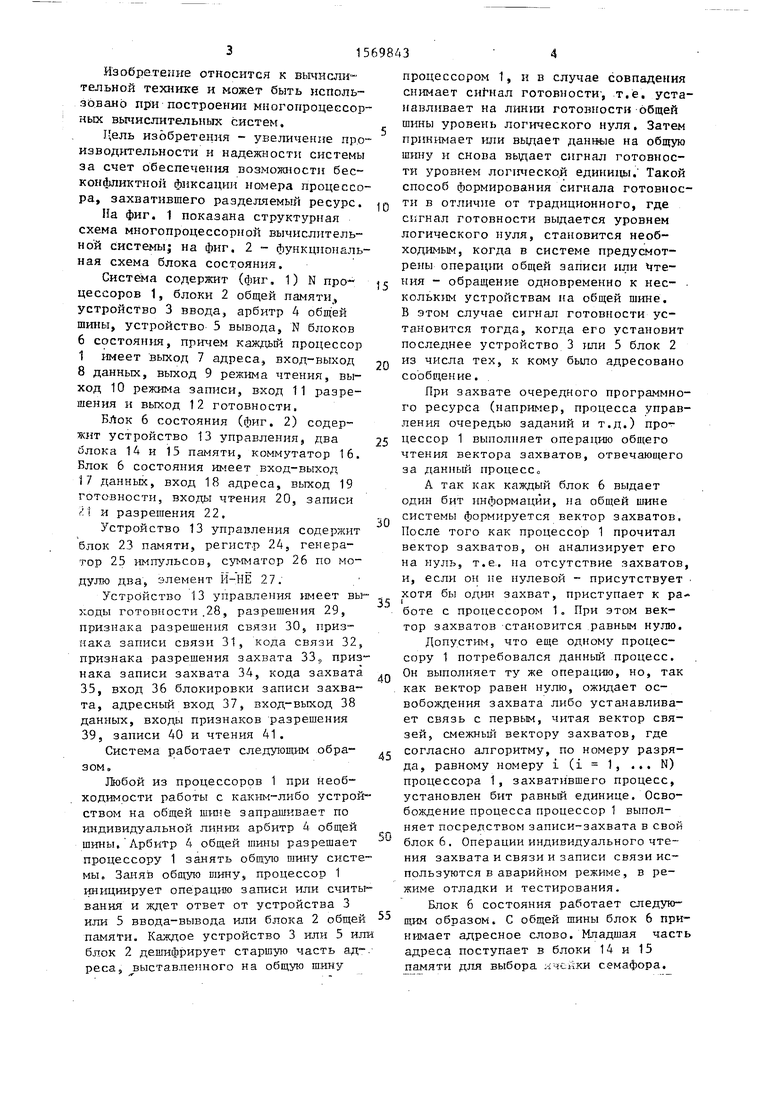

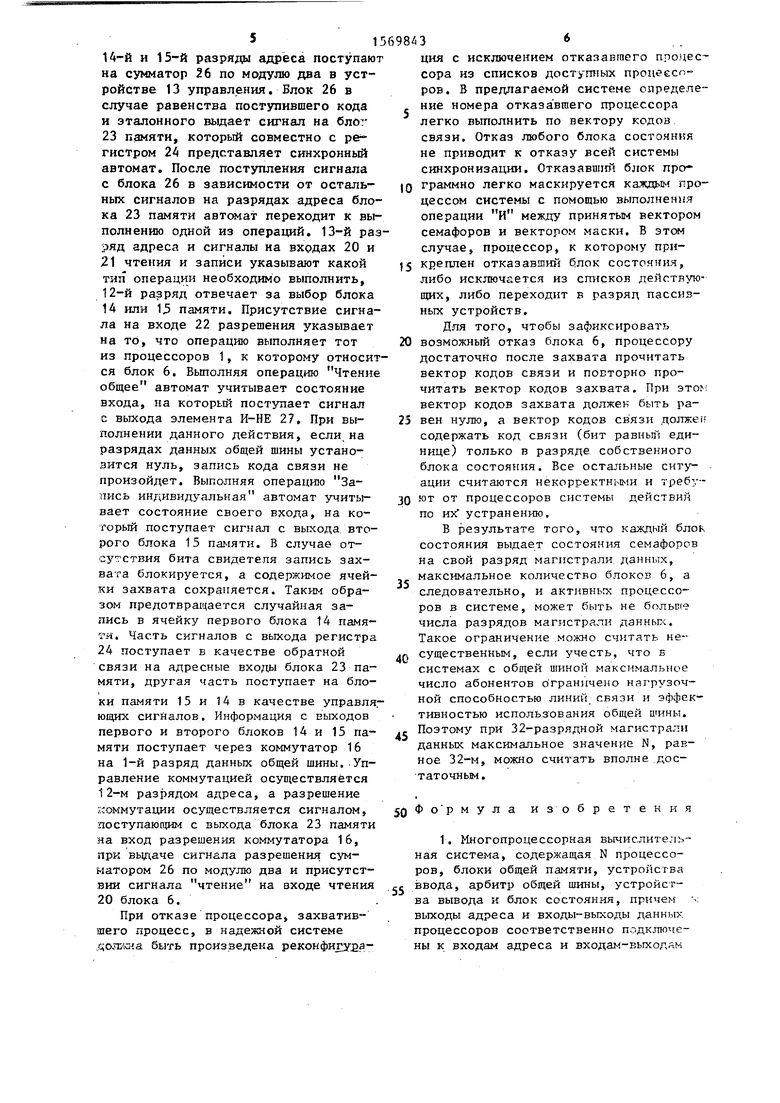

Изобретение относится к вычислительной технике и может быть использовано при построении многопроцессорных вычислительных систем. Цель изобретения - увеличение производительности и надежности системы за счет обеспечения возможности бесконфликтной фиксации номера процессора, захватившего разделяемый ресурс. Цель достигается тем, что система содержит N процессоров 1, блоки 2 общей памяти, устройства 3 ввода, арбитр 4 общей шины, устройства 5 вывода и N блоков 6 состояния. Причем каждый процессор имеет выход 7 адреса, вход-выход 8 данных, выходы режима чтения 9 и режима записи 10, а также вход 11 разрешения и выход 12 готовности. 2 з.п. ф-лы, 2 ил.

Фиг1

.«&.

31

Изобретение относится к вычислительной технике и может быть использовано при построении многопроцессорных вычислительных систем.

Цель изобретения - увеличение производительности и надежности системы за счет обеспечения возможности бесконфликтной фиксации номера процессора, захватившего разделяемый ресурс.

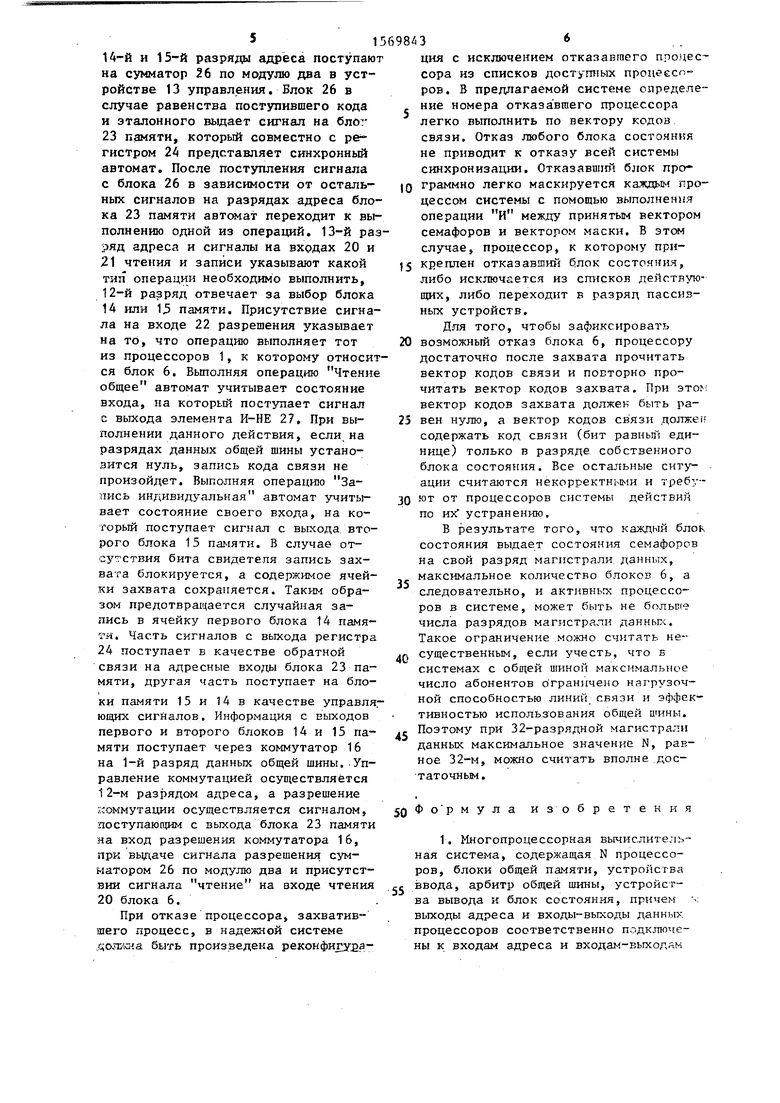

На фиг. 1 показана структурная схема многопроцессорной вычислительной системы; на фиг. 2 - функциональная схема блока состояния.

Система содержит (фиг. 1) N процессоров 1, блоки 2 общей памяти, устройство 3 ввода, арбитр 4 общей

шины, устройство 5 вывода, N блоков

6 1

состояния, причем каждый процессор

имеет выход 7 адреса, вход-выход 8 данных, выход 9 режима чтения, выход 10 режима записи, вход 11 разрешения и выход 12 готовности.

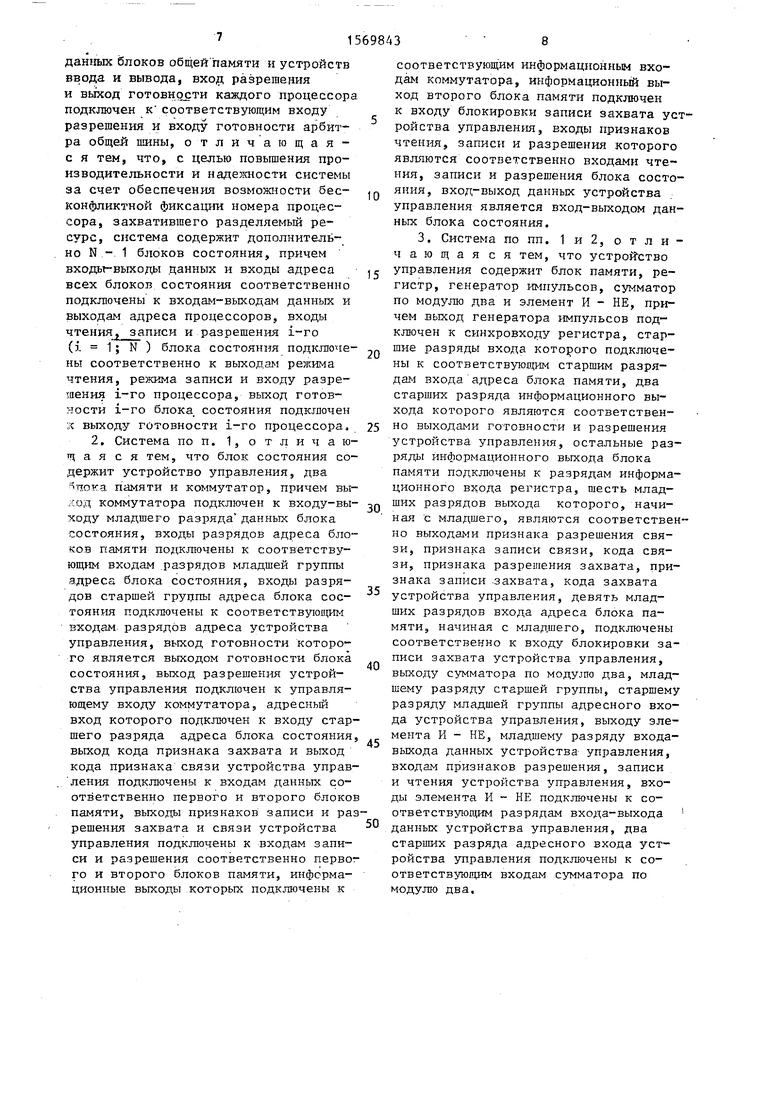

Блок 6 состояния (фиг. 2) содержит устройство 13 управления, два Олока 14 и 15 памяти, коммутатор 16. Блок 6 состояния имеет вход-выход 17 данных, вход 18 адреса, выход 19 готовности, входы чтения 20, записи - I и разрешения 22.

Устройство 13 управления содержит блок 23 памяти, регистр 24, генератор 25 импульсов, сумматор 26 по модулю два, элемент И-НЁ 27.

Устройство 13 управления имеет выходы готовности .28, разрешения 29, признака разрешения связи 30, признака записи связи 31, кода связи 32, признака разрешения захвата 33, признака записи захвата 34, кода захвата 35, вход 36 блокировки записи захвата, адресный вход 37, вход-выход 38 данных, входы признаков разрешения 39, записи 40 и чтения 41.

Система работает следующим образом.

Любой из процессоров 1 при необходимости работы с каким-либо устройством на общей шине запрашивает по индивидуальной линии арбитр 4 общей шины. Арбитр 4 общей шины разрешает процессору 1 занять общую шину системы. Заняв общую шину, процессор 1 инициирует операцию записи или считывания и ждет ответ от устройства 3 или 5 ввода-вывода или блока 2 общей памяти. Каждое устройство 3 или 5 ил блок 2 дешифрирует старшую часть адреса, выставленного на общую шину

0

5

0

5

0

5

0

5

0

процессором 1, и в случае совпадения снимает сигнал готовности, т.е. устанавливает на линии готовности общей шины уровень логического нуля. Затем принимает или выдает данные на общую шину и снова выдает сигнал готовности уровнем логической единицы. Такой способ формирования сигнала готовности в отличие от традиционного, где сигнал готовности выдается уровнем логического нуля, становится необходимым, когда в системе предусмотрены операции общей записи или чтения - обращение одновременно к нес- . кольким устройствам на общей шине. В этом случае сигнал готовности установится тогда, когда его установит последнее устройство 3 или 5 блок 2 из числа тех, к кому было адресовано сообщение.

При захвате очередного программного ресурса (например, процесса управления очередью заданий и т.д.) процессор 1 выполняет операцию общего чтения вектора захватов, отвечающего за данный процесс„

А так как каждый блок 6 выдает один бит информации, на общей шине системы формируется вектор захватов. После того как процессор 1 прочитал вектор захватов, он анализирует его на нуль, т.е. па отсутствие захватов, и, если он не нулевой - присутствует . хотя бы один захват, приступает к работе с процессором 1. При этом вектор захватов становится равным нулю.

Допусти, что еще одному процессору 1 потребовался данный процесс. Он выполняет ту же операцию, но, так как вектор равен нулю, ожидает освобождения захвата либо устанавливает связь с первым, читая вектор связей, смежный вектору захватов, где согласно алгоритму, по номеру разряда, равному номеру i (i 1, ... N) процессора 1, захватившего процесс, установлен бит равный единице. Освобождение процесса процессор 1 выполняет посредством записи-захвата в свой блок 6. Операции индивидуального чтения захвата и связи и записи связи используются в аварийном режиме, в режиме отладки и тестирования.

Блок 6 состояния работает следующим образом. С общей шины блок 6 принимает адресное слово. Младшая часть адреса поступает в блоки 14 и 15 памяти для выбора л --к лки семафора.

51

14-й и 15-й разряды адресе поступаю на сумматор 26 по модулю два в устройстве 13 управления. Блок 26 в случае равенства поступившего кода и эталонного выдает сигнал на бло 23 памяти, который совместно с регистром 24 представляет синхронный автомат. После поступления сигнала с блока 26 в зависимости от остальных сигналов на разрядах адреса блока 23 памяти автомат переходит к выполнению одной из операций. 13-й разряд адреса и сигналы на входах 20 и 21 чтения и записи указывают какой тип операции необходимо выполнить, 12-й разряд отвечает за выбор блока 14 или 15 памяти. Присутствие сигнала на входе 22 разрешения указывает на то, что операцию выполняет тот из процессоров 1, к которому относится блок 6. Выполняя операцию Чтение общее автомат учитывает состояние входа, на который поступает сигнал с выхода элемента И-НЕ 27. При выполнении данного действия, если на разрядах данных общей шины установится нуль, запись кода связи не произойдет. Выполняя операцию Запись индивидуальная автомат учитывает состояние своего входа, на который поступает сигнал с выхода второго блока 15 памяти. В случае от- jy-стния бита свидетеля запись захвата блокируется, а содержимое ячейки захвата сохраняется. Таким образом предотвращается случайная запись в ячейку первого блока 14 памя- .-и. Часть сигналов с выхода регистра 24 поступает в качестве обратной связи на адресные входы блока 23 памяти, другая часть поступает на блоки памяти 15 и 14 в качестве управляющих сигналов. Информация с выходов первого и второго блоков 14 и 15 памяти поступает через коммутатор 16 на 1-й разряд данных общей шины. Управление коммутацией осуществляется 12-м разрядом адреса, а разрешение /коммутации осуществляется сигналом, поступающим с выхода блока 23 памяти на вход разрешения коммутатора 16, при выдаче сигнала разрешения сумматором 26 по модулю два и присутствии сигнала чтение на входе чтения 20 блока 6.

При отказе процессора, захватившего процесс, в надежной системе й,олжна быть произведена реконфигув3

9843

ция с исключением отказавшего процессора из списков доступных пропеесг- ров. В предлагаемой системе определение номера отказавшего процессора легко выполнить по вектору кодов связи. Отказ любого блока состояния не приводит к отказу всей системы синхронизации. Отказавший блок про- Ю граммно легко маскируется каждым процессом системы с помощью выполнение операции И между принятым вектором семафоров и вектором маски. В этом случае, процессор, к которому прн- 15 креплен отказавший блок состояния, либо исключается из списков действующих, либо переходит в разряд пассивных устройств.

Для того, чтобы зафиксировать 20 возможный отказ блока 6, процессору достаточно после захвата прочитать вектор кодов связи и повторно прочитать вектор кодов захвата. При это вектор кодов захвата должен быть ра- 25 вен нулю, а вектор кодов связи должен содержать код связи (бит равный единице) только в разряде собственного блока состояния. Все остальные ситуации считаются некорректными и тррбл- 30 ют от процессоров системы действии по их устранению.

В результате того, что каждый блок состояния выдает состояния семафорсв на свой разряд магистрали данных, максимальное количество блоков 6, а следовательно, и активных процессоров в системе, может быть не болыпе числа разрядов магистрали данные. Такое ограничение можно счнтатг- не- Q существенным, если учесть, что в системах с общей шиной максимальное число абонентов ограничено нагрузочной способностью линии святи и эффективностью использования общей шины. Поэтому при 32-разрядной магистрали данных максимальное значение N, равное 32-м, можно считать вполне достаточны.

5

5

Формула изобретения

данных блоков общей памяти и устройств ввода и вывода, вход разрешения и выход готовности каждого процессора подключен к соответствующим входу разрешения и входу готовности арбитра общей шины, отличающая- с я тем, что, с целью повышения производительности и надежности системы за счет обеспечения возможности бесконфликтной фиксации номера процессора, захватившего разделяемый ресурс, система содержит дополнительно N - 1 блоков состояния, причем входы-выходы цанных и входы адреса всех блоков состояния соответственно подключены к входам-выходам данных и выходам адреса процессоров, входы чтения, записи и разрешения 1-го (х 1; N ) блока состояния подключены соответственно к выходам режима чтения, режима записи и входу разрешения 1-го процессора, выход готовности 1-го блока состояния подключен с выходу готовности 1-го процессора.

0

5

0

5

0

5

0

соответствующим информационным входам коммутатора, информационный выход второго блока памяти подключен к входу блокировки записи захвата устройства управления, входы признаков чтения, записи и разрешения которого являются соответственно входами чтения, записи и разрешения блока состояния, вход-выход данных устройства управления является вход-выходом данных блока состояния.

11

18

Фиг. г

| Электроника, №11, с | |||

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

| Многопроцессорная вычислительная система | 1985 |

|

SU1277129A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-07—Публикация

1988-07-14—Подача