Изобретение относится к вычислительной технике, в частности к запоминающим устройствам со встроенными аппаратными средствами контроля йотладки, и может быт1. использовано в j мяти, хранящей один разряд. С выхода

качестве оперативной памяти ЭВМ.

Цель изобретения - повьЕпение быстродействия устройства,

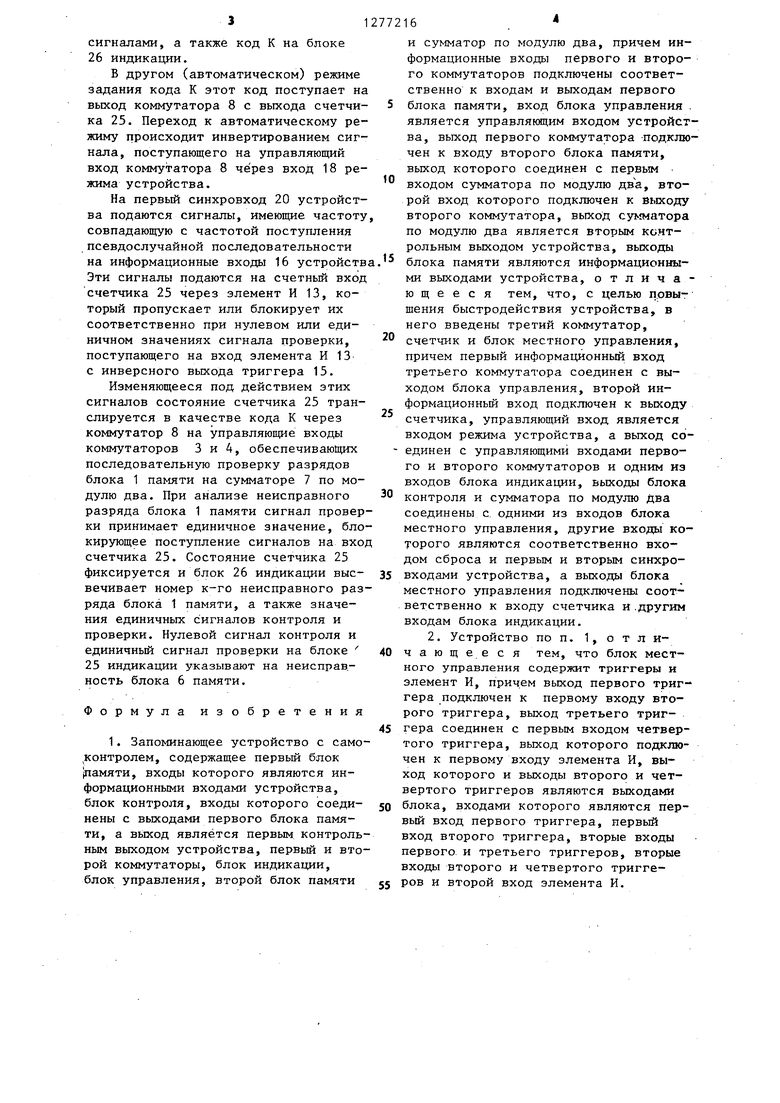

На чертеже представлена структурная схема устройства.

Устройство содержит первый блок 1 памяти, блок 2 контроля, первый коммутатор 3, второй коммутатор 4, блок 5 управления, второй блок 6 памяти, сумматор 7 по модулю два, третий ком мутатор 8, блок 9 местного управления, в который входят первый триггер 10, второй триггер 11, имеющий выход 12 элемент И 13, третий триггер 14, четвертый трип ер 15, информационные входы 16 устройства, управляющий вход 17 устройства, вход режима 18 устройства,, вход 19 сброса устройства, первый спнхровход 20 устройства, второй синхро1 ход 21 устройства информационные входы 22 устройства, первьй контрольный выход 23 устройства, второй контрол1)Ный выход 24 устройства. Устройстве) также содержит счетчик 25 и блок 26 индикации.

Устройство работает следу1.ж;им образом.

В начальный момент времени на вход 19 сброса устройства поступает сигнал сброса, устанавливающий триггеры 11 и 15 в состояние отсутствия ошибки.

Б блок 1 памяти записывается псевдослучайная последовательность слов, включающая как информационные разряды, так и соответствующие им вычисленные ранее контрольные разряды, например, по модулю три. Считываемая из блока 1 памяти информация поступает на информационные выходы 22 устройства, а также на входы блока 2 контроля, сопоставляющего информационную и кон ;7рольную часть сло и вырабатывающего сигнал контроля, поступающий на первый контрольный выход 23 устройства. В блоке 5 управления, реализованном, например, в виде тумблерных переключателей, имеющих два положения О и 1, задается двоичный код К. Этот код поступает на вход коммутатора 8. С выхода коммутатора 8 код К поступает на адресные входы коммутаторов 3 и 4, выбирающих при этом сигналы с входа и

выхода к-го разряда блока 1 памяти. С выхода коммутатора 3 сигнал заносится в одноразрядный блок 6 памяти, устроенный подобно части блока 1 па

0

5

0

5

0

5

O

коммутатора 4 и выхода блока 6 памяти поступают на входы сумматора 7 по модулю два, вырабатьюакщего сигнал проверки К -го разряда блока 1 памяти. Этот сигнал поступает на контрольный выход 24 устройства.

Сигналы контроля и проверки с выходов блока 2 контроля и сумматора 7 по модулю два поступают также на одни из входов соответственно первого 10 и третьего 14 триггеров (например, выполненные в микросхеме 133 ТМ2). На другие входы этих триггеров поступают (через второй 21 синхровход устройства) синхросигналы, имеющие частоту, совпадающую с частотой пос тупления слов псевдослучайной последовательности на информационные входы 16 устройства.

Запись сигналов контроля и проверки в первый 10 и третий 14 триггеры происходит по завершению переходных процессов переключения в блоке 2 контроля и сумматоре 7 по модулю два. С выходов первого 10 и третьего 14 триггеров сигналы контроля и проверки поступают на установочные входы соответственно второго 11 и четвертого 15 триггеров.

Второй 11 и четвертый 15 триггеры вапоми1шют значения этих сигналов при обнаружении ошибки на первом 23 и втором 24 контрольных выходах устройства и по/|;ают их, а также код К с выхода кoм ryтaтopa 8 на вход 26 индикации. Блок индикации высвечивает состояния сигналов контреля и проверки к-го разряда блока 1 памяти, а также код К при единичном значении сигнала контроля (сигналы контроля и проверки имеют единичное значение при наличии ошибки).

Задание кода К посредством блока 5 (в соответствуюш,ем режиме) позволяет определить значения сигнала проверки для всех интересующих пользователя разрядов К блока 1 памяти (при многократном повторении псевдо случайной последовательности), проанализировать вид сигналов проверки и контроля, подключая осциллограф к второму 24 и первому 23 контрольным выходам устройства, увидеть наличие ошибки,, регистрируемой этими

сигналаьш, а также код К на блоке 26 индикации.

В другом (автоматическом) режиме задания кода К этот код поступает на выход коммутатора 8 с выхода счетчи- ка 25. Переход к автоматическому режиму происходит инвертированием сигнала, поступающего на управляющий вход коммутатора 8 через вход 18 режима устройства.

На первый синхровход 20 устройства подаются сигналы, имеющие частоту совпадающую с частотой поступления псевдослучайной последовательности на информационные входы 16 устройств Эти сигналы подаются на счетный вход счетчика 25 через элемент И 13, который пропускает или блокирует их соответственно при нулевом или единичном значениях сигнала проверки, поступающего на вход элемента И 13 с инверсного выхода триггера 15.

Изменяющееся под действием этих сигналов состояние счетчика 25 транслируется в качестве кода К через коммутатор 8 на управляющие входы коммутаторов 3 и 4, обеспечивающих последовательную проверку разрядов блока 1 памяти на сумматоре 7 по модулю два. При анализе неисправного разряда блока 1 памяти сигнал проверки принимает единичное значение, блокирующее поступление сигналов на вход счетчика 25. Состояние счетчика 25 фиксируется и блок 26 индикации вые- вечивает номер к-го неисправного разряда блока 1 памяти, а также значения единичных сигналов контроля и проверки. Нулевой сигнал контроля и единичньй сигнал проверки на блоке 25 индикации указывают на неисправ.- ность блока 6 памяти.

Формула изобретения

1. Запоминающее устройство с самоконтролем, содержащее первьш блок ртамяти, входы которого являются информационными входами устройства, блок контроля, входы которого соеди- нены с выходами первого блока памяти, а выход является первым контрольным выходом устройства, первый и второй коммутаторы, блок индикации, блок управления, второй блок памяти

5

0 5 0

5

0 j

и сумматор по модулю два, причем информационные входы первого и второго коммутаторов подключены соответственно к входам и выходам первого блока памяти, вход блока управления . является управлякщим входом устройства, выход первого коммутатора -подключен к входу второго блока памяти, выход которого соединен с первым входом сумматора по модулю два, второй вход которого подключен к выходу второго коммутатора, выход сумматора по модулю два является вторым контрольным выходом устройства, выходы блока памяти являются информационными выходами устройства, отличающееся тем, что, с целью повы- щения быстродействия устройства, в него введены третий коммутатор, счетчик и блок местного управления, причем первый информационный вход третьего коммутатора соединен с выходом блока управления, второй информационный вход подключен к выходу счетчика, управляющий вход является входом режима устройства, а выход соединен с управляющими входами первого и второго коммутаторов и одним из входов блока индикации, выходы блока контроля и сумматора по модулю два соединены с одними из входов блока местного управления, другие входы которого являются соответственно входом сброса и первым и вторым синхро- входами устройства, а выходы блока местного управления подключены соответственно к входу счетчика и.другим входам блока индикации.

2. Устройство по п. 1, о т л и- чающееся тем, что блок местного управления содержит триггеры и элемент И, причем выход первого триггера подключен к первому входу второго триггера, выход третьего триггера соединен с первым входом четвертого триггера, выход которого подключен к первому входу элемента И, выход которого и выходы второго и четвертого триггеров являются выходами блока, входами которого являются первый вход первого триггера, первый вход второго триггера, вторые входы первого и третьего триггеров, вторые входы второго и четвертого триггеров и второй вход элемента И.

17 18

fi

li

г

t

/

Редактор M. Товтин

Составитель В. Рудаков Техред А.Кравчук

Заказ 6687/48 Тираж 543Подписное

БНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, К-ЗЗ, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

/2

2B

Корректор. А. Зимокосов

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дискретных объектов | 1984 |

|

SU1242958A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для контроля высоковольтного тиристорного вентиля | 1983 |

|

SU1153374A1 |

| Устройство для обнаружения ошибок в блоках интегральной оперативной памяти | 1988 |

|

SU1605281A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для измерения параметра динамического процесса и управления им с самоконтролем | 1986 |

|

SU1423985A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

Изобретение относится, к вычислительной технике, в частности к запоминающим устройствам со встроенными аппаратными средствами контроля и отладки, и может быть использовано в качестве оперативной памяти ЭВМ. Цель изобретения - повышение быстродействия устройства за счет уменьшения времени локализации неисправности устройства. Устройство содержит блоки памяти, блок контроля, коммутаторы, блок управления, сумматор по модулю два, счетчик, блок индикации и блок местного управления. 1 з.п. ф-лы, 1 ил. с (О СЛ

| Запоминающее устройство с самоконтролем | 1977 |

|

SU696545A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-12-15—Публикация

1985-05-16—Подача