Изобретение относится к вычислительной технике и может быть применено для аппаратурной реализации операции вычисления квадратного корня.

Цель изобретения - сокрашение ап- паратур ных затрат.

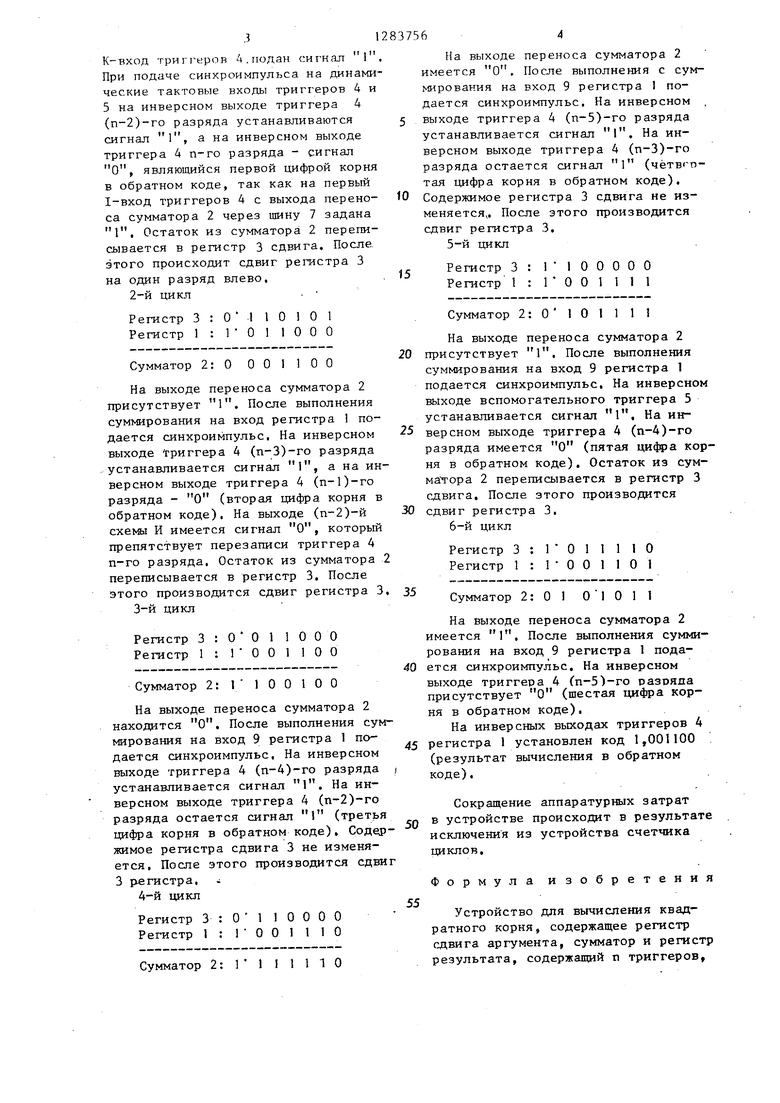

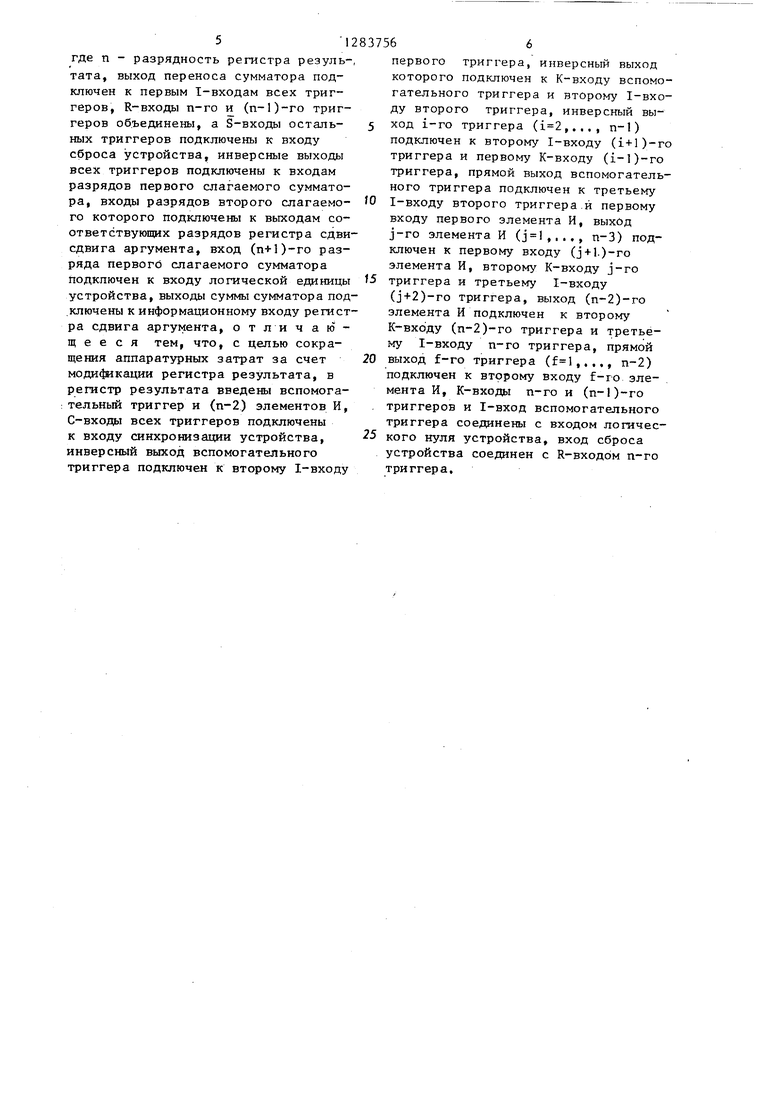

На фиг. 1 представлена блок-схема устройства ДД1Я вычисления квадратного корняJ на фиг. 2 - функциональная схема регистра результата,

Устройство для вычисления квадратного корня содержит регистр 1 результата, сумматор 2 и регистр 3 сдвига аргумента

Регистр , результата содержит п 1К-триггеров 4, вспомогательный

ГК-триггер 5; элементы И 6 вход 7 переноса, вход 8 сброса и вход 9 си1-1хронизации,

Для вы шсления квадратного корн из числа, содержащего п двоичных разрядов с п разряднои. точностью сумматор 2 и регистр 3 сдвига должны иметь по (п+) разрядово

Вычисление квадратного корня,осществляется следующим образоМв

I

Подкоренное выражение заносится

в регистр 3,

В иЬходном состоякии в старшем (левом) разряде (п+1)-го регистра 3 сдвига аргумента записан О в и (п- -)м разрядах регистра

, а в остал

результата записана ньп;; разрядах регистра I записаны О, На вход старшего (n+l)-го разряда первого слагаемого сумматора подана 1.

Сначала производится вычисление квадратного корня из старпшх цвук цифр подкоренного вырагкення. Для этого с помощью сумматора 2 произ водится сложение содер}кимого регисра I и содержимого регистра 3, Есл на выходе сумматора 2 образуется сигнал переноса 1 % то первая цифра корня равна % если сигнала переноса нет О,

Для получения второй цифры корн на вход 9 синхронизадии регистра подается синхроимпульс. При этом первая цифра корня заносится в обратном к оде в п-й разряд регистра

1, а 1 с выхода триггера 4 () разряда регистра I переписывается триггер 4 (п-2)-го разряда этого ргистра,, Если первая цифра корня - едишща, то в сумматоре 2 сформиро

0

ван остаток, который переписывается в регистр 3, Если цифра корня - ноль, то подкоренное выражение, записанное в регистре 3, остается без изменения. Затем производится сдвиг регистра 3 на один разряд влево.

Далее процесс вычисления выполняется как и для первой цифры корня.

После получения второй цифры кор-, ня на вход 9 синхронизации 1 результата подается синхроимпульс. В (п-)-й разряд регистра 1 записывается вторая цифра корня (в обратном коде) Единица с выхода триггера 4 (п- 5 2)-го разреза регистра 1 переписывается в триггер 4 ()го разряда этого регистра Затем производится сдвиг регистра 3 на один разряд влево и определяется третья цифра корня.

После выполнения п циклов в регистре 1 записывается результат вычисления квадратного корня в обратном коде.

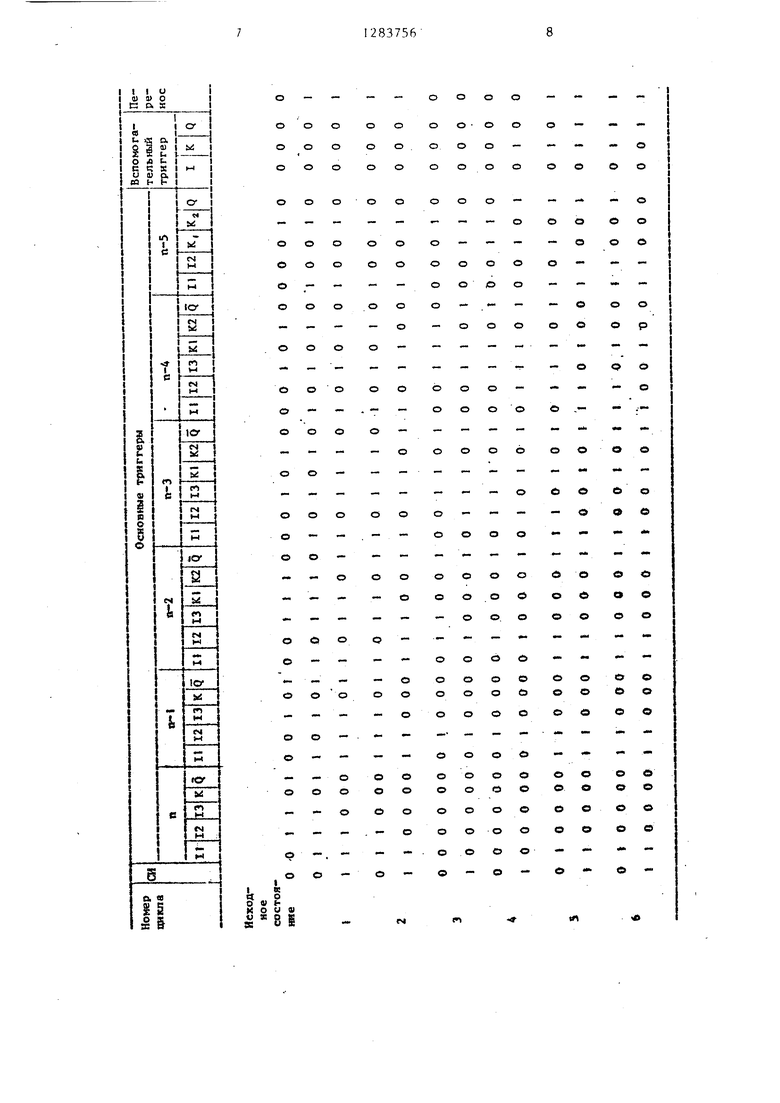

П р и м е р. Вычисление квадратного корня из числа 0,101010.

В таблице приведены значения логических сигналов на информационных входах и выходах триггеров 4 и 5 для данного примера.

Сигнал начальной установки поступает через вход 8 ре.гистра 1 на входы сброса триггеров 4 п-гои ()-го разрядов, устанавливая на их инверсных выходах 1, и на входы установил 1 триггеров 4 остальных разрядов и вспомогательного триггера 5, устанавливая на их инверсных выходах О, 1-й цикл.

Регистр 3; О 1 О 1

Регистр 1: 1 1 1

0

5

0

О 1 О 0000

5

j ряда подан сигнал

Сумматор 2: О О i 1 О 1 О

На выходе переноса сумматора 2 1, После выполнения

0

присутствует

суммирования содержимых регистров 1 и 3 на вход синхронизации 9 регистра 1 подается синхроимпульс.

На второй 1-вход триггера 4 п-го разряда подан сигнал на втором 1 входе триггеров 4 остальных разрядов на третьем 1-входе триггеров 4 всех разрядов - 1. На первый К-вход триггера 4 (п-2)-го раз1 ; на первый Квход триггеров 4 остальных разрядов и триггера 5 - О. К-входы триггеров 4 п-го и (п-1)-го разрядов соединены с общей шиной На второй

3

К-вход триггеров (людан сигнал 1 При подаче синхроимпульса на динамические тактовые входы триггеров 4 и 5 на инверсном выходе триггера 4 (п-2)-го разряда устанавливаются сигнал 1, а на инверсном выходе триггера 4 п-го разряда - сигнал О, являющийся первой цифрой корня в обратном коде, так как на первый 1-вход триггеров 4 с выхода переноса сумматора 2 через шину 7 задана 1, Остаток из сумматора 2 переписывается в регистр 3 сдвига. После этого происходит сдвиг peiTicTpa 3 на один разряд влево.

2-й цикл.

Регистр 3 : О 1 10101 Регистр 1 : 1 О 1 1000

Сумматор 2: О 001100

На выходе переноса сумматора 2 присутствует 1. После выполнения суммирования на вход регистра 1 подается синхроимпульс. На инверсном выходе триггера 4 (п-З)-го разряда устанавливается сигнал 1, а на инверсном выходе триггера 4 (п-1)-го разряда - О (вторая цифра корня в обратном коде). На выходе (п-2)-й

схеъи И имеется сигнал О, который препятствует перезаписи триггера 4 п-го разряда. Остаток из сумматора переписывается в регистр 3. После этого производится сдвиг регистра 3

3-й цикл

Регистр 3 Регистр 1

0 О 1 1000

1 О О 1 100

Сумматор 2: I 100100

На выходе переноса сумматора 2 находится О, После выполнения суммирования на вход 9 регистра 1 подается синхроимпульс. На инверсном выходе триггера 4 (п-4)-го разряда устанавливается сигнал 1. На инверсном выходе триггера 4 (п-2)-го разряда остается сигнал 1 (третья цифра корня в обратном коде), Содержимое регистра сдвига 3 не изменяется. После этого производится сдвиг 3 регистра, 4-й цикл

Регистр 3:0 110000 Регистр 1 : 1 О О 1 1 10

Сумматор 2: Г 1 I 1 1 1 О

837564

На выходе переноса сумматора 2 имеется О, После выполнения с суммирования на вход 9 регистра 1 подается синхроимпульс. На инверсном .

5 выходе триггера 4 (п-5)-го разряда устанавливается сигнал 1. На инверсном выходе триггера 4 (п-З)-го разряда остается сигнал 1 (чётвгп- тая цифра корня в обратном коде).

10 Содержимое регистра 3 сдвига не изменяется,. После зтого производится сдвиг регистра 3. 5-й цикл

Регистр 3 Регистр 1

1 1 О О О О О Г О О 1 1 1 1

Сумматор 2: О 1 О 1 1 1 1

На выходе переноса сумматора 2 присутствует 1. После выполнения суммирования на вход 9 регистра 1 подается синхроимпульс. На инверсном выходе вспомогательного триггера 5 устанавливается сигнал 1. На И1Г версном выходе триггера 4 (п-4)-го разряда имеется О (пятая ци4фа корня в обратном коде). Остаток из сумматора 2 переписывается в регистр 3 сдвига. После этого производится сдвиг регистра 3.

6-й цикл

Регистр 3 Регистр 1

1 О 1 1 1 1 О 1-001 101

5

0

5

Сумматор 2:01 О 1 О 1 1

На выходе переноса сумматора 2 имеется 1. После выполнения суммирования на вход 9 регистра 1 подается синхроимпульс. На инверсном выходе триггера 4 (п-5)-го разряда присутствует О (шестая цифра корня в обратном коде).

На инверсных выходах триггеров 4 регистра 1 установлен код 1,001100 (результат вычисления в обратном коде).

Сокращение аппаратурных затрат в устройстве происходит в результате исключения из устройства счетчика

циклов.

Формула изобретения

Устройство для вычисления квадратного корня, содержащее регистр сдвига аргумента, сумматор и регистр результата, содержащий п триггеров.

где n - разрядность регистра резуль-, тата, выход переноса сумматора подключен к первым 1-входам всех триггеров, R-входы п-го и (n-l)-ro триггеров объединены, а S-входы остальных триггеров подключены к входу сброса устройства, инверсные выходы всех триггеров подключены к входам разрядов первого слагаемого сумматора, входы разрядов второго слагаемого которого подключены к выходам соответствующих разрядов регистра сдви- сдвига аргумента, вход (п+1)-го разряда первогй слагаемого сумматора подключен к входу логической единицы устройства, выходь суммы сумматора под- .ключены к информационному входу регистра сдвига аргумента, отличающееся тем, что, с целью сокращения аппаратурных затрат за счет модификации регистра результата, в регистр результата введены вспомога- : тельный триггер и (п-2) элементов И, С-входы всех триггеров подключены к входу синхронизации устройства, инверсный выход вспомогательного триггера подключен к второму 1-входу

первого триггера, инверсный выход которого подключен к К-входу вспомогательного триггера и второму 1-входу второго триггера, инверсный выход i-ro триггера (,.,., п-1)

подключен к второму 1-входу (i+1)-го триггера и первому К-входу (i-l)-ro триггера, прямой выход вспомогательного триггера подключен к третьему

1-входу второго триггера.и первому входу первого элемента И, выход j-ro элемента И (,..,, п-3) подключен к первому входу (j + l.)-ro элемента И, второму К-входу j-ro

триггера и третьему 1-входу

(j+2)-ro триггера, выход (п-2)-го элемента И подключен к второму К-входу (п-2)-го триггера и третьему 1-входу п-го триггера, прямой

выход f-ro триггера (,..., п-2) подключен к второму входу f-ro элемента И, К-входы п-го и (п-1)-го триггеров и 1-вход вспомогательного триггера соединены с входом логического нуля устройства, вход сброса устройства соединен с R-входом п-го триггера.

2./

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня | 1988 |

|

SU1501051A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1140118A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Арифметическое устройство | 1979 |

|

SU860065A1 |

| Устройство для вычисления квадратного корня | 1987 |

|

SU1481753A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1132289A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1008736A1 |

Изобретение относится к области вычислительной техники и может быть использовано для аппаратурной реализации операции извлечения квадратного корня. Цель изобретения - сокращение аппаратурных затрат - достигается за счет модификации регистра 1 результата. Устройство содержит ре.- гистр 3 сдвига аргумента, сумматор 2 и регистр 1 результата, содержаний (п+1) 1К-триггеров и п - 2 ahe- ментов И (где п - разрядность регистра 1). Принцип работы устройства основан на поразрядных операциях с использованием сдвига. 2 ил., 1 табл.

n-t

7«r

fi-i

ft-4

fff

aif

| Устройство для вычисления квадратного корня | 1979 |

|

SU877529A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО для ВЫЧИСЛЕНИЯ КВАДРАТНОГО КОРНЯ | 0 |

|

SU239665A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1140118A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-15—Публикация

1985-07-17—Подача