Изобретение относится к вычислительной технике и может быть использовано в системах обмена данными в - качестве устройства буферной памяти.

Цель изобретения - расширение функциональных возможностей за счет обеспечения многократного считывания необходимой области блока памяти.

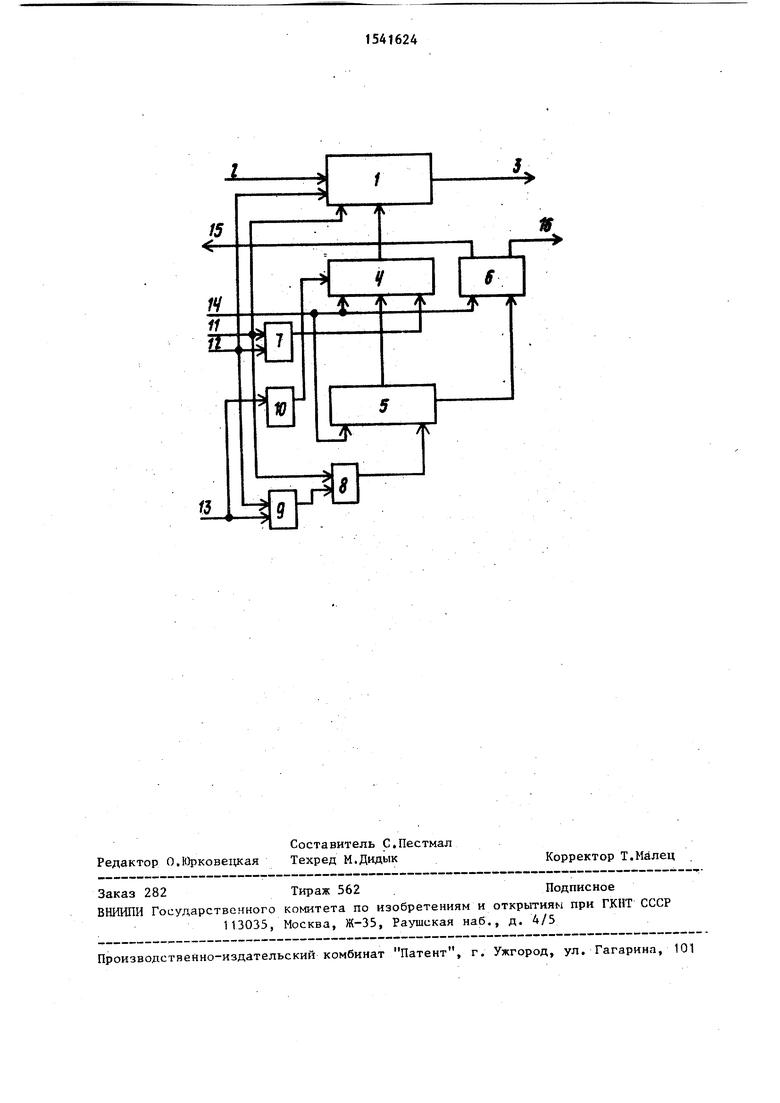

На чертеже приведена структурная схема устройства.

Устройство содержит блок 1 памяти, информационные входы 2 и выходы 3, счетчики 4 и 5, триггер 6, элементы ИЛИ 7 и 8, элемент И 9, одновибра- тор 10, входы 11-14 и выходы 15 и 16.

Устройство работает следующим образом.

Перед началом работы сигналом по входу 14 установки устанавливаются в нулевое состояние счетчики 4 и 5 и триггер 6.

Высокий уровень сигнала на нулевом выходе триггера 6, т.е. на выходе 15, свидетельствует о том, что устройство находится в режиме записи информации. Записываемые данные

поступают на вход 2 устройства в сопровождении сигнала на входе 11, который, поступая на вход синхронизации записи блока 1 памяти, осуществляет запись данных по адресу, сформированному на выходах счетчика 4. Задним фронтом сигнала на входе 11, проходящего через элементы ИЛИ 7 и 8, осуществляется модификация содержимого (добавляется единица) счетчиков 4 и 5. Запись последующих информационных слов в блок 1 памяти осуществляется аналогично. Это происходит до тех пор, пока на выходе переполнения счетчика 5 не появится сигнал, который поступает на счетный вход триггера 6 и своим задним фронтом устанавливает его в единичное состояние. При этом низкий уровень сигнала на нулевом выходе триггера 6, т.е. на выходе 15 устройства, запрещает передатчику информации формировать .запросы на запись данных. В то же время высокий уровень сигнала на единичном выходе триггера 6, т.е. на выходе 16 устройства, свидетельству(Я

ел

Јь ОЭ

ю

Јь

ет о том, что устройство готово к выполнению операции чтения данных. Запрос на чтение данных поступает от приемника информации по вхо 12 и на вход стробирования чтения данных блока 1 памяти. При этом на информационные выходы 3 устройства считываются данные по адресу, сформированному на выходах счетчика 4. Задним фронтом сигнала на входе 12 устройства, проходящего через элемент ИЛИ 7, модифицируется содержимое счетчика 4. Этим же сигналом (при высоком уровне сигнала на входе 13), проходящим через элементы И 9 и ИЛИ 8, производится модификация содержимого счетчика 5. При низкой уровне сигнала на входе 13 устройства модификация содержимого счетчика 5 не производится. Если приемнику информации требуется считать данные, хранящиеся в блоке 1 памяти один раз, то в режиме чтения приемник информации поддерживае на входе 13 устройства высокий уровень сигнала. При этом чтение информации с блока 1 памяти производится по запросам приемника информации по входу 12 устройства до тех пор, пока на выходе переполнения счетчика 5 не появится сигнал, по заднему фронту которого триггер 6 устанавливается в нулевое состояние, переводя тем самым устройство в режим записи. Если приемнику информации требуется считать какую- либо область блока 1 памяти несколько раз, например, для вывода одних и тех же данных на различные регистрирующие устройства, то по достижении счетчиком 4 (и счетчиком 5) начальной границы этой области приемник информации устанавливает на входе 13 устройства низкий уровень сигнала, который запрещает дальнейшую модификацию содержимого счетчика 5 при выполнении запросов на чтение, поступающих по входу 12. По окончании первого считывания данных, хранящихся в данной области памяти, приемник информации устанавливает высокий уровень сигнала на входе 13 управления, по переднему фронту которого одновибратор 10 формирует на выходе импульс, который переписывает в счетчик 4 по информационным входам начпльнуп паницу

0

5

0

5

0

5

0

5

0

5

требуемой области памяти из счетчика 5. Формула изобретения

Устройство для буферизации информации, содержащее блок памяти, первый счетчик, триггер, первый элемент ИЛИ, элемент И, причем информационные вход и выход блока памяти являются входом и выходом устройства для подключения соответственно к информационному выходу источника информации и информационному входу приемника информации, нулевой и единичный выходы триггера являются выходами устройства для подключения соответственно к входу разрешения записи источника информации и к входу разрешения чтения приемника информации, при этом выход первого счетчика соединен с адресным входом блока памяти, о т л и чающе еся тем, что, с целью расширения функциональных возможностей за счет обеспечения многократной выдачи одной и той же информации, в устройство введены второй счетчик, второй элемент ИЛИ, одновибратор, причем первьй вход первого элемента ИЛИ соединен с первым входом второго элемента ИЛИ, с входом записи блока памяти и является входом устройства для подключения к выходу синхронизации записи источника информации, второй вход первого элемента ИЛИ соединен с первым входом элемента И, с входом чтения блока памяти и является входом устройства для подключения к выходу синхронизации чтения приемника информации, второй вход элемента И соединен с входами запуска одновибрато- ра и является входом устройства для подключения к разрешающему выходу приемника информации, нулевой вход триггера соединен с установочными входами первого и второго счетчиков и является установочным входом устройства, при этом выход элемента И соединен с вторым входом второго элемента ИЛИ, выход которого соединен со счетным входом второго счетчика, выход переполнения юторого соединен со счетным входом триггера, счетный и информационный входы и вход записи первого счетчика соединены соответственно с выходом первого элемента ИЛИ, с выходом второго счетчика и с выходом одновибратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1376091A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1658160A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1647579A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1381530A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1571596A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278979A2 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1416988A1 |

| Устройство для контроля блоков буферной памяти | 1987 |

|

SU1501175A1 |

| Устройство для ввода информации | 1987 |

|

SU1472912A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обмена данными в качестве буферной памяти. Цель изобретения - расширение функциональных возможностей за счет обеспечения многократного считывания необходимой области блока памяти. Устройство содержит блок памяти, два счетчика, триггер, одновибратор, два элемента ИЛИ, элемент И. 1 ил.

| Устройство сопряжения | 1982 |

|

SU1019428A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1236491A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-07—Публикация

1988-05-30—Подача