Изобретение относится к вычислительной технике и может быть использовано в качестве устройства буферной памяти систем обработки информации.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности обмена информацией блоками переменной длины.

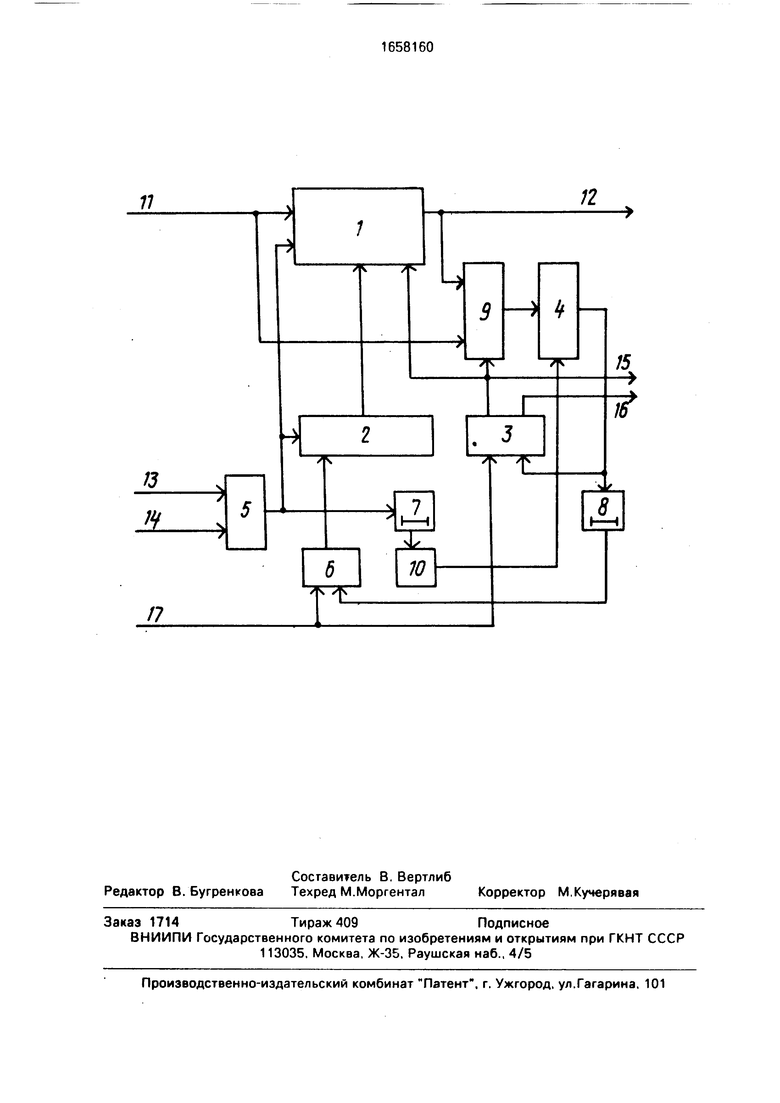

На чертеже приведена функциональная схема устройства.

Устройство содержит блок 1 памяти, счетчик 2, триггер 3, дешифратор 4, элементы ИЛИ 5 и 6, элементы 7 и 8 задержки, мультиплексор 9, одновибратор 10, инфор- мационгные входы 11 и выходы 12, входы 13 и 14 синхронизации записи и чтения, выходы 15 и 16 разрешения записи и чтения, вход 17 установки устройства.

Устройство работает следующим образом.

Перед началом работы сигналом по входу 17 установки счетчик 2 и триггер 3 устанавливаются в нулевое состояние.

Низкий уровень сигнала на прямом выходе триггера 3, т. е. на выходе 15, устанавливает для блока 1 памяти режим записи и запрещает приемнику информации обращаться с запросами на чтение данных. Высокий уровень сигнала на инверсном выходе триггера 3 и на выходе 16 разрешает источнику информации обращаться с запросами на запись данных.

Записываемые данные поступают на вход 11 устройства в сопровождении сигнала на входе 13 синхронизации, который поступает через элемент ИЛИ 5 на вход синхронизации обращения блока 1 памяти и осуществляет запись данных с входов 11 в блок 1 памяти по адресу, сформированному на счетчике 2. Задним фронтом сигнала синхронизации по входу 13 производится модификация содержимого счетчика 2, т. е.

(Е

О

о а

о

к его содержимому добавляется,единица. Запись последующих информационных слов в устройстве выполняется аналогично. При записи каждого информационного слова анализируется его содержимое с целью фиксации появления признака Конец информационного блока. Этот анализ выполняется на дешифраторе 4. В режиме записи низкий уровень сигнала на прямом выходе триггера 3, воздействуя на вход управления мультиплексора 9, обеспечивает подключение к входу дешифратора 4 информационного входа 11. На вход строЬирования дешифратора 4 поступает выходной сигнал одновибратора 10, который формирует сигнал по переднему фронту сигнала на выходе элемен га ИЛИ 5, задержанного на элементе 7 задержки. При появлении на информационных входах 11 признака Конец информационного блока и его записи в блок 1 памяти в момент стробирования дешифратора 4 на его выходе появляется сигнал, по заднему фронту которого триггер 3 изменяет на противоположное свое состояние (в данном случае устанавливается в единичное состояние), тем самым подготавливает устройство для работы в режиме чтения. Выходной сигнал дешифратора 4, проходя через элемент 8 задержки и элемент ИЛИ 6,устанавливает счетчик 2 в нулевое состояние. Высокий уровень сигнала на прямом выходе триггера 3. т, е. на выходе 15 устройства, разрешает приемнику информации обращаться с запросами на чтение данных, низкий уровень сигнлла на инверсном выходе триггера 3, т. е. ня выходе 16 устройства, запрещает источнику информации обращаться к устройству с запросами на запись.

В режиме чтения каждого информационного слова запрос приемника информации поступает на вход 14 синхронизации и, проходя через элемьнт ИЛ И 5, воздействует на вход синхронизации обращения блока 1 памяти, что приводит к появлению на информационном выходе 12 информационного слова, считанного из блока 1 памяти по адресу, сформированному на выходах счетчика 2. Чтение последующих слов информационного блока в устройстве выполняется аналогично. В режиме чтения, точно так же, как и в режиме записи, производится поиск признака Конец информационного блока. В этом случае к дешифратору 1 через мультиплексор 9, на входе управления которого присуУствует в данный момент высокий уро- вень сигнала, подключаются выходные сигналы блока 1 памяти. При чтении из блока 1

памяти информационного слова, содержащего признак Конец информационного блока, триггер 3 и счетчик 2 устанавливаются в нулевое состояние, т. е устройство подготавливается к работе в режиме записи

данных.

Формула изобретения Устройство для сопряжения источника и приемника информации, содержащее блок

памяти, информационный вход и выход которого являются соответственно информационными входом и выходом устройства, первый элемент задержки, соединенный входом с выходом первого элемента ИЛИ и

счетным входом счетчика, выход которого подключен к адресному входу блока памяти, синхронизирующим входом подключенного к выходу первого элемента ИЛИ, первый и второй входы которого являются соответственно входами синхронизации записи и чте- ния, и дешифратор, выход которого соединен со счетным входом триггера, прямой выход которого подключен к входу записи-чтения блока памяти и является

выходом разрешения записи устройства, а инверсный выход и вход сброса являются соответственно выходом разрешения чтения и входом начальной установки устройства, отличающееся тем, что, с целью

расширения функциональных возможностей устройства за счет обеспечения возможности обмена информацией блоками переменной длины, в устройство введены мультиплексор, второй элемент ИЛИ, второй элемент задержки и одновибратор, причем первый и второй информационные входы мультиплексора подключены соответственно к информационному входу и выходу устройства, а управляющий вход и

выход - соответственно к прямому выходу триггера и информационному входу дешифратора, стробирующим входом соединенного через одновибратор с выходом первого элемента задержки, а выходом - через второй элемент задержки - с первым входом второго элемента ИЛИ, выход и второй вход которого соединены соответственно с установочным входом счетчика и входом начальной установки устройства.

77

-

n

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источника и приемника информации | 1990 |

|

SU1718224A1 |

| Устройство для сопряжения источника и приемника информации | 1989 |

|

SU1730630A2 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1647579A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1381530A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1416988A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

Изобретение может быть использовано при построении устройств сопряжения систем обработки информации. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности обмена информацией блоками переменной длины. Это позволяет повысить эффективндсть организации передачи данных между источником и приемником информации. Цель достигается введением в устройство, содержащее блок памяти, дешифратор, счетчик, первый элемент ИЛИ, триггер и первый элемент задержки, мультиплексора, второго элемента ИЛИ, второго элемента задержки и одновибратора. 1 ил.

/J

1

щ

б

/5

TL

5

;0

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1571596A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1236491A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1991-06-23—Публикация

1988-12-20—Подача