1

Изобретение относится .к запоминающим устройствам и может быть применено в системах обмена данными, автоматике и вычислительной технике,

Целью изобретения является расширение области применения буферного запоминающего устройства за счет сокращения времени хранения информации.

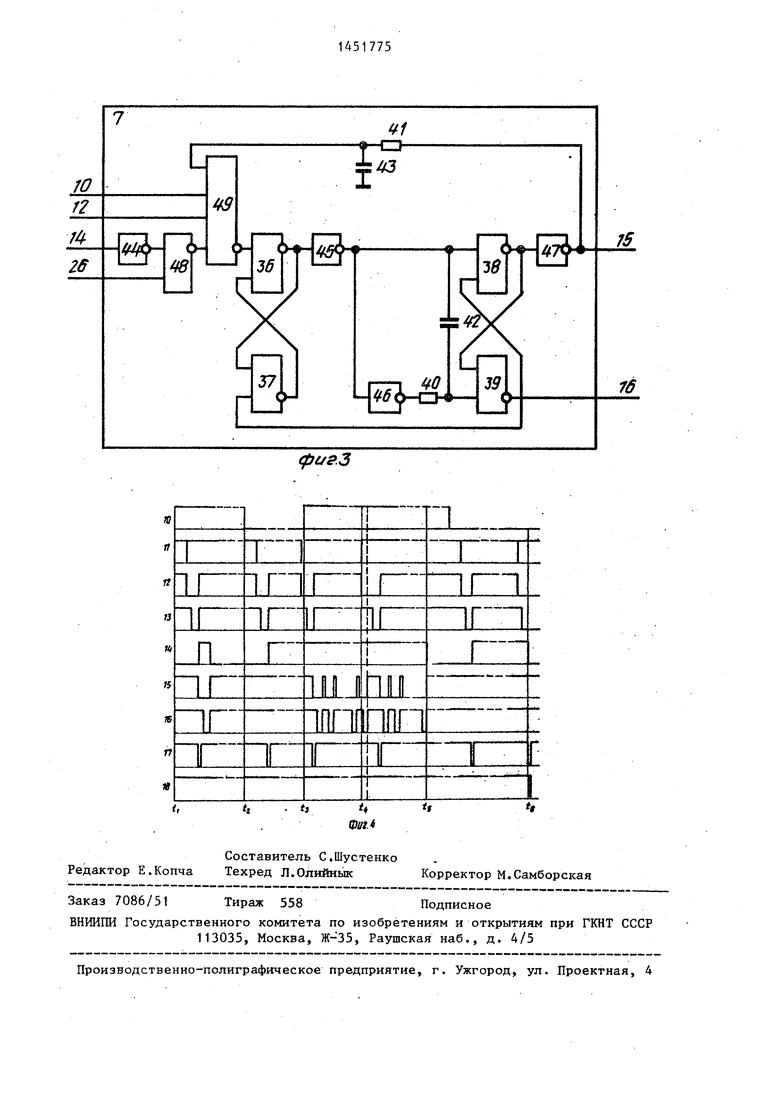

На фиг.1 изображена функциональная схема предлагаемого устройства; на фиг.2 и 3 - принципиальные схемы одновибратора и управляемого ге- .нератора,соответственно;на фиг.4 - временные диаграммы, поясняющие работу устройства.

Устройство содержит блок 1 памяти, счетчик 2 адресов записи,счетчик 3 адресов чтения, блок 4 сравнения, коммутатор 5, одновибратор 6, управляемьй генератор 7, одновибра- тор 8,триггер 9, вход 10 готовности, вход 11 обращения, выходы 12 и 13 одновибратора 6, выход 14 блока 4 сравнения, выходы 15 и 16 управляемого генератора 7, выход 17 одновибратора 8, выход 18 переполнения, выходы 19 и 20 счетчиков 2 и 3, выход 2Г коммутатора 5, информационный вход 22, информационный выход 23 устройства, вход 24 сброса, вход 25 счетных импульсов, вход 26 принудительного пуска и вход сброса.

Одновибратор 6 (см. фиг.2) содержит элементы И-НЕ 27-30, резистор 31, конденсатор 32, элементы И-НБ 33, элемент И 34 и элемент НЕ 35. При поступлении запускающего импульса на вход 11 на выходе 12 выра- батьшается импульс логического О, запрещающий дальнейщую генерацию импульсов считьшания. Затем в отсутствие сигнала задержки (логическая 1 на выходе 15) на выходе 13 вырабатывается более короткий импульс записи, поступающий на вход блока 1. При наличии сигнала задержки (логический О на входе 15) выдача импульса на выходе 13 задерживается до появления на выходе 15 логической 1. Импульсы на выходах 12 и 13 заканчиваются одновременно.

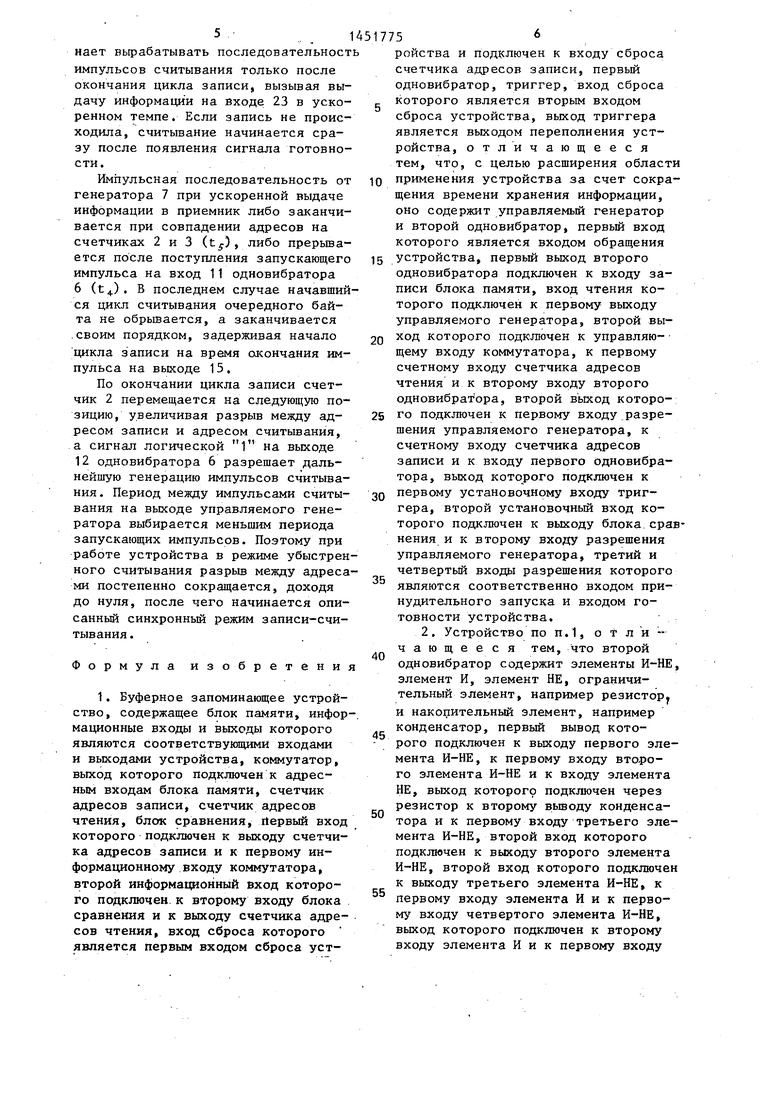

Управляемый генератор 7 (см. фиг.З) содержит элементы И-НЕ 36-39 резисторы 40 и 41, конденсаторы 42 и 43, элементы НЕ 44-47, элемент И-НЕ 48 и элемент И-НЕ 49. При нали

1

10

15

20

25

5530

35

40

45

50

517752

чии на входе 10 и выходах 12 и 14 сигналов логической 1 управляемый генератор вырабатывает на выходах 15 и 16 последовательность импульсов с периодом следования, соответствующим максимальной скорости обмена данными с приемником. При установке хотя бы одного из указанных сигналов в логический О управляемый генератор заканчивает формирование последнего импульса считывания и затем прекращает свою работу. При подаче короткого импульса логического О на вход 26 управляемый генератор 7 вьщает импульсы на выходах 15 и 16 даже при наличии логического О на выходе 14. Б начале цикла считьшания генерируется импульс логического О на выходе 15, а затем более короткий импульс на выходе 16. Оба указанные импульса заканчиваются одновременно .

Адреса записи и считьшания вырабатываются счетчиками 2 и 3 на выходах 19 и 20 соответственно. Изменение состояния счетчиков происходит на задних фронтах импульсов, поступающих на выходы 12 и 15.Кроме того, состояние счетчика 3 может измениться при подаче импульсов на вход 25.

Блок 4 сравнения при совпадении адресов вырабатывает на выходе 14 сигнал логического О, запрещающий генерацию импульсов считывания и поступающий также на вход триггера 9.

Ком У1утатор 5 передает на выход 21.адрес от счетчика 2, если сигнал на выходе 15 равен логической 1. В противном случае на выход 21 поступает адрес от счетчика 3.

Одновибратор 8 при поступлении на выход 12 импульса от одновибратора 6 по его заднему фронту вырабатывает на выходе 17 короткий импульс для установки триггера 9.

Устройство работает следующим образом.

В исходный момент (t,) счетчики 2 и 3, а также триггер 9 устанавливаются в нулевое состояние, при этом логический О на выходе 14 блока 4 сравнения запрещает работу управляемого генератора 7, а логическая 1 на выходе 15 разрешает запуск одно- вибратора 6 .

При поступлении на вход 11 импульса от передатчика вначале на выходе

12 одновибратора 6 вырабатьшается импульс логического О, запрещающий работу управляемого генератора 7, а затем на выходе 13 - более короткий импульс, которым информация на входе 22 записьгоается в блок 1 памяти по адресу от счетчика 2 адресов записи.

По окончании импульса на выходе 12 счетчик 2 изменяет свое состояние. При этом блок 4 сравнения фиксирует несовпадение адресов и вы- рабатьшает на выходе 14 сигнал логической 1, который совместно с сигналами логической 1 на выходе 12 одновибратора 6 и на входе 10 рарешают генерацию импульсов считывания.

Управляемый генератор 7 аналогично одновибратору 6 вначале вырабатывает импульс логического О на выходе 15 для коммутации адреса от счетчика считьшания на выход 21 и задержки запуска одновибратора 6 при поступлении запускающего импульса во время генерации импульсов считывания. Затем на выходе 16 вы- рабатывается более короткий импульс осуществляющий считывание информации из блока 1 памяти по выходу 23. При этом по выходу 16 импульс считывания проходит в приемник, сигнализируя о появлении этой информации .

По окончании цикла считывания счетчик 3 перемещается в следующзпо позицию, при этом адреса сравниваются и сигнал на выходе 14 блока 4 сравнения становится равньм логическому О, запрещая дальнейшую генерацию импульсов считывания.

Описанньм цикл записи-считывания повторяется каждый раз при поступлении на вход 11 запускающего импульса до тех пор, пока на входе 10 готовности имеется логическая 1.

Однако, когда приемник вьщает сигнал неготовности (например, при записи накопленного блока информации на магнитную ленту), режим работы предлагаемого устройства изменяется (t:) .

Логический О на входе 10 запрещает генерацию импульсов считывания но не препятствует записи. При этом счетчик 3 считывания остается в неизменном состоянии, а счетчик 2 записи продолжает перемещаться.

10

15

0

25

0

5

0

5

0

5

Если сигнал готовности не примет значения логической 1 до переполнения блока 1 памяти, т.е. до того момента, когда вследствие изменения счетчика 2 адреса совпадут (t), импульс на выходе 17 элемента задержки поступит на вход триггера 9 в тот момент времени, когда сигнал на выходе 14 блока 4 сравнения равей логическому О. При этом триггер 9 установится в единичное состояние (логический О на выходе 18), сигнализируя об аварийном состоянии, а вьщача передатчиком запускающих импульсов по входу 11 должна пре- . кратиться.

Информация, записанная к этому моменту в блоке 1, не пропадает и при появлении логической 1 на входе Ю готовности может быть считана в приемник посредством подачи одиночного короткого импульса на вход 26 управляемого генератора 7. При этом после считывания первого слова сигнал равенства адресов на выходе блока 4 сравнения становится равньм логической 1, разрешая дальнейшую работу управляемого генератора без принудительного запуска. Таким образом, информация из блока 1 слово за словом передается в приемник. При неготовности приемника эта выдача приостанавливается, но после появления сигнала готовности возобновляется.

Процесс автоматической выдачи информации происходит до тех пор, пока все содержимое блока 1 не перепишется в приемник, т.е. когда адрес считывания станет равным адресу записи.

При необходимости триггер переполнения может быть сброшен,-, и процесс записи возобновлен сразу же после считывания в приемник первого слова,

В случае, когда новая информация является более ценной, чем старая, допустимо после переполнения продолжить запись в блок 1, одновременно подтягивая адрес считывания импульсами от передатчика, подаваемыми на вход 25 счетчика 3. При этом теряется наиболее старая информация.

Сигнал готовности на входе 10 появляется до переполнения блока 1 (Сз). В этом случае, если начался цикл записи (логический О на выходе 12)управляемый генератор 7 начине проис- начинается ера- сигнала готовнонает вьфабатывать последовательност импульсов считывания только после окончания цикла записи, вызывая выдачу информаци и на входе 23 в ускоренном темпе. Если запись ходила, считывание зу после появления сти.

Импульсная последовательность от генератора 7 при ускоренной выдаче информации в приемник либо заканчивается при совпадении адресов на счетчиках 2 и 3 (t), либо прерьюа- ется после поступления запускающего импульса на вход 11 одновибратора 6 (t). В последнем случае начавшийся цикл считывания очередного байта не обрьшается, а заканчивается .своим порядком, задерживая начало цикла записи на время окончания импульса на выходе 15,

По окончании цикла записи счетчик 2 перемещается на следующую позицию, увеличивая разрыв между адресом записи и адресом считывания, а сигнал логической 1 на выходе 12 одновибратора 6 разрешает дальнейшую генерацию импульсов считывания . Период между импульсами считывания на выходе управляемого генератора выбирается меньшим периода запускающих импульсов. Поэтому при работе устройства в режиме убыстренного считывания разрьш между адресами постепенно сокращается, доходя до нуля, после чего начинается описанный синхронный режим записи-считывания .

Формула изобретени

1. Буферное запоминающее устройство, содержащее блок памяти, инфор мационные входы и выходы которого являются соответствующими входами и выходами устройства, коммутатор, выход которого подключен к адресным входам блока памяти, счетчик адресов записи, счетчик адресов чтения, блок сравнения, йервый вход которого подключен к выходу счетчика адресов записи и к первому информационному входу коммутатора, второй информационный вход которого подключен к второму входу блока сравнения и к выходу счетчика адре- сов чтения, вход сброса которого является первым входом сброса уст

5

0

5

0

5

0

5

0

5

ройства и подключен к входу сброса счетчика адресов записи, первый одновибратор, триггер, вход сброса которого является вторым входом сброса устройства, выход триггера является выходом переполнения устройства, отличающееся тем, что, с целью расширения области применения устройства за счет сокращения времени хранения информации, оно содержит управляемый генератор и второй одновибратор, первьй вход которого является входом обращения устройства, первый выход второго одновибратора подключен к входу записи блока памяти, вход чтения которого подключен к первому выходу управляемого генератора, второй выход которого подключен к управляющему входу коммутатора, к первому счетному входу счетчика адресов чтения и к второму входу второго одновибрат ора, второй выход которого подключен к первому входу.разрешения управляемого генератора, к счетному входу счетчика адресов записи и к входу первого одновибратора, выход которого подключен к первому установочному входу триггера, второй установочный вход которого подключен к выходу блока.сравнения и к второму входу разрешения управляемого генератора, третий и четвертый входы разрешения которого являются соответственно входом принудительного запуска и входом готовности устройства.

2. Устройство по П.1, о т ли - чающееся тем, что второй одновибратор содержит элементы И-НЕ, элемент И, элемент НЕ, ограничительный элемент, например резистор, и накопительный элемент, например конденсатор, первый вывод которого подключен к выходу первого элемента И-НЕ, к первому входу вто.ро- го элемента И-НЕ и к входу элемента НЕ, выход которого подключен через резистор к второму вьшоду конденсатора и к первому входу третьего элемента И-НЕ, второй вход которого подключен к выходу второго элемента И-НЕ, второй вход которого подключен к выходу третьего элемента И-НЕ, к первому входу элемента И и к первому входу четвертого элемента И-НЕ, выход которого подключен к второму входу элемента Ник первому входу

пятого элемента И-НЕ, выход которого подключен к второму входу .четвертого элемента И-НЕ и первому входу первого элемента И-НЕ, второй вход первого элемента И-НЕ, второй вход пятого элемента И-НЕ, выход третьего элемента И-НЕ и выход элемента И являются соответственно вторым входом, первым входом, первым выходом и вторым выходом второго одновибратора.

3. Устройство по п.1, о т л и - чающееся тем, что управляемый генератор содержит элементы И-НЕ, элементы НЕ, ограничительные элементы, например резисторы, и накопительные элементы, например конденсаторы, первый выход первого из которых подключен к первому входу первого элемента И-НЕ, к выходу первого элемента НЕ и к входу второго элемента НЕ, выход которого подключен через первый резистор к второму выводу первого конденсатора и к первому входу второго элемента И-НЕ, второй вход которого подключен к входу третьего элемента НЕ и к выходу первого элемента И-НЕ, второй

8

вход которого является первым выходом управляемого генератора и подключён к выходу второго элемента И-НЕ и к первому входу третьего элet мента И-НЕ, выход которого подключей к первому входу четвертого элемента И-НЕ, выход которого подключен.к второму входу третьего элемента И-НЁ

и к входу первого элемента НЕ, выход третьего элемента НЕ является вторым выходом управляемого генератора и подключен через второй резистор к первому выводу второго конденсатора и к первому входу пятого элемента И-НЕ, выход которого подключен к второму входу четвертого элемента И-НЕ, второй вход пятого элемента И-НЕ подключен к выходу шестого элемента И-НЕ, первый вход которого подключен к выходу четвертого элемента НЕ, второй вывод второго конденсатора подключен к общей шине, третий и четвертый входы пятого элемента И-НЕ, вход четвертого элемента НЕ и второй вход шестого элемента И-НЕ являются соответственно четвертым, третьим, вторым и первым входами разрешения управляемого генератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с внешним устройством | 1989 |

|

SU1755286A2 |

| Устройство для сопряжения абонента с магистралью | 1989 |

|

SU1679494A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для диагностического контроля оперативной памяти | 1991 |

|

SU1807525A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Многопроцессорная система | 1989 |

|

SU1686455A1 |

| Устройство для регистрации результатов контроля | 1985 |

|

SU1406596A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

Изобретение относится к запоминающим устройствам. Целью изобретения является расширение области применения устройства за счет сокращения времени хранения информации. Буферное запоминающее устройство содержит блок 1 памяти, счетчик 2 адресов записи, счетчик 3 адресов чтения, блок 4 сравнения, коммутатор 5, одновибратор 6, управляемый генератор 7, осуществляющий выдачу информации из блока 1 между циклами записи при готовности приемника, а также одновибратор 8 и триггер 9. Для согласования работы одновибратора 6 и управляемого генератора 7 при появлении внешнего сигнала записи во время считывания информации запуск одновибратора 6 задерживается на время завершения происходящего в этот момент цикла считывания (время задержки много меньше периода импульсов записи), после чего осуществляется вьщача одновибратором импульс сов записи с одновременным запрещением работы генератора 7. Тем самым обеспечивается максимальное сокращение, времени работы буферного устройства в режиме хранения информации. 2 з.п. ф-лы, 4 шт. su сл i4i СП -ч -ч СП fBtoiR/

(pus.Z

(pejf.3

| Буферное запоминающее устройство | 1976 |

|

SU583476A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1048515A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-01-15—Публикация

1987-06-04—Подача