Изобретение относится к вычислительной технике и может быть использовано для аппаратной реализации операции вычисления квадратного корня в универсальных и специализированных вычислительных устройствах.

Цель изобретения - повышение помехоустойчивости устройства за счет совмещения вычисления квадратного корня с выполнением оператора сглаживания.

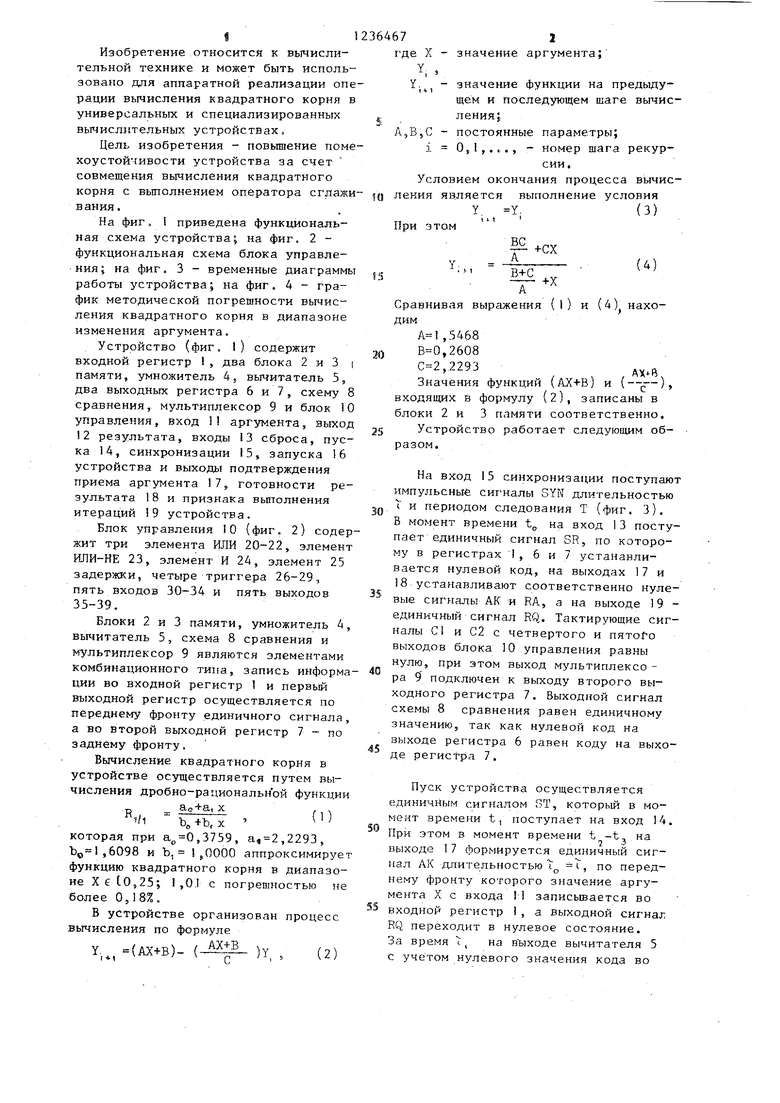

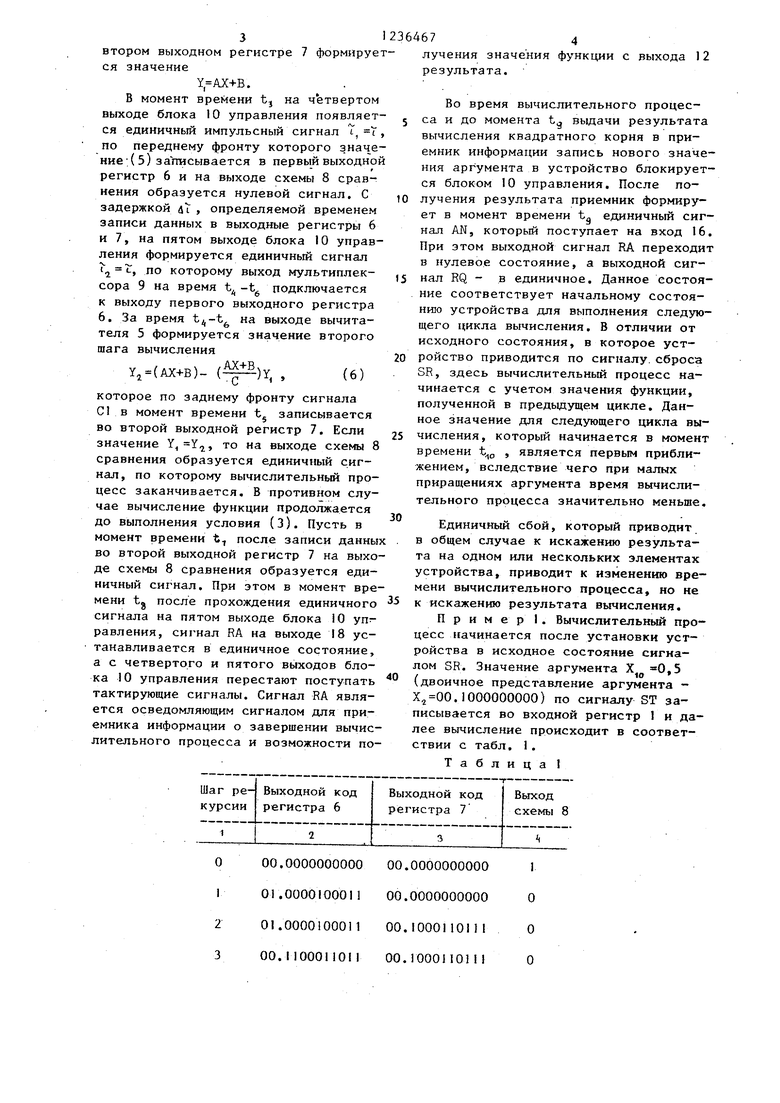

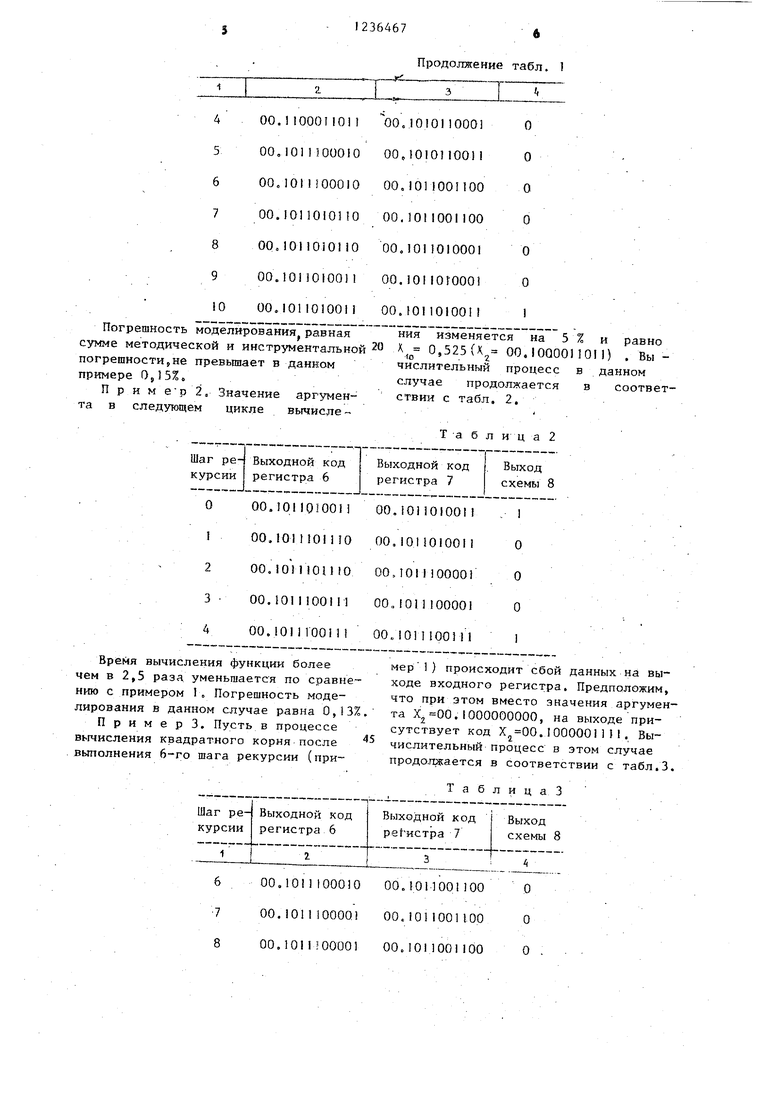

На фиг. I приведена функциональная .схема устройства, на фиг. 2 - функциональная схема блока управле- ния; на фиг. 3 - временные диаграммы работы устройства; на фиг. 4 график методической погрешности вычисления квадратного корня в диапазоне изменения аргумента.

Устройство (фиг, I) содержит входной регистр , два блока 2 и 3 i памяти, умножитель 4, вьгчитатель 5, два выходных регистра 6 и 7, схему 8 сравнения, мультиплексор 9 и блок 10 управления, вход 1 аргумента, выход 2 результата, входы 13 сброса, пуска 14, синхронизации 15, запуска 16 устройства и выходы подтверждения приема аргумента 17, готовности результата 18 и признака выполнения итераций 9 устройства.

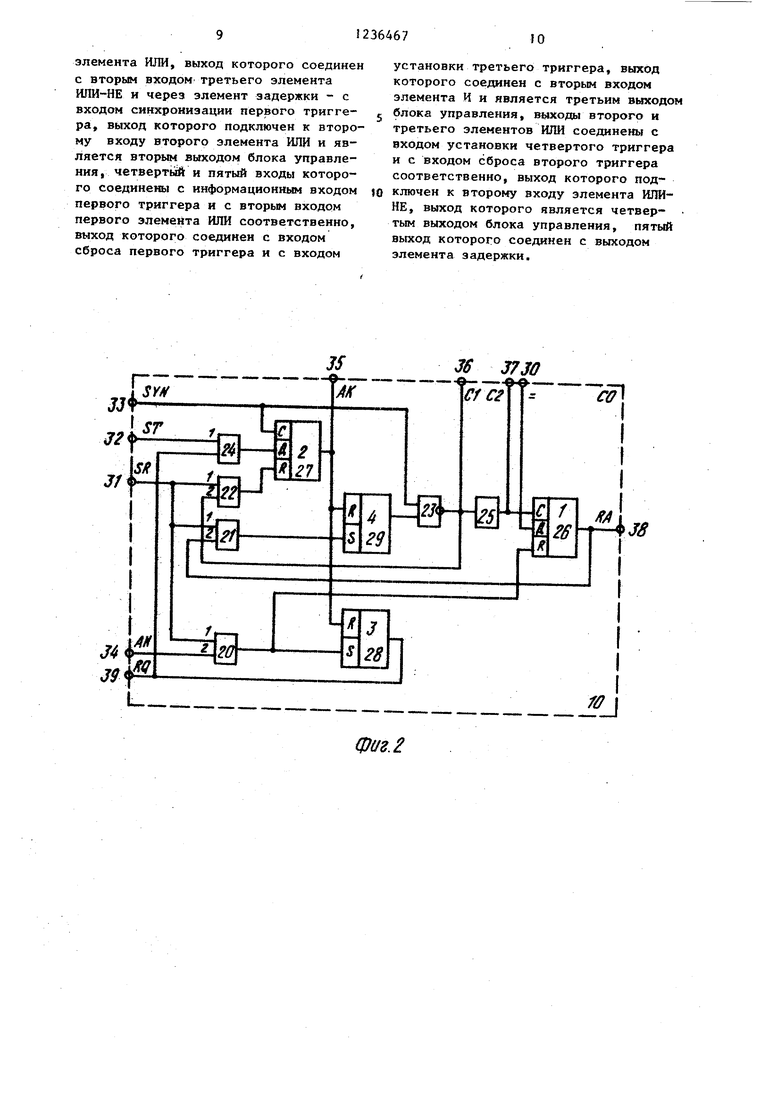

Блок управления 0 (фиг. 2) содержит три элемента ИЛИ 20-22, элемент ИЛИ-НЕ 23, элемент И 24, элемент 25 задержки, четыре триггера 26-29, пять входов 30-34 и пять выходов 35-39.

Блоки 2 и 3 памяти, умножитель 4, вычитатель 5, схема 8 сравнения и мультиплексор 9 являются элементами комбинационного типа, запись информации во входной регистр 1 и первьй выходной регистр осуществляется по переднему фронту единичного сигнала, а во второй выходной регистр 7 - по заднему фронту.

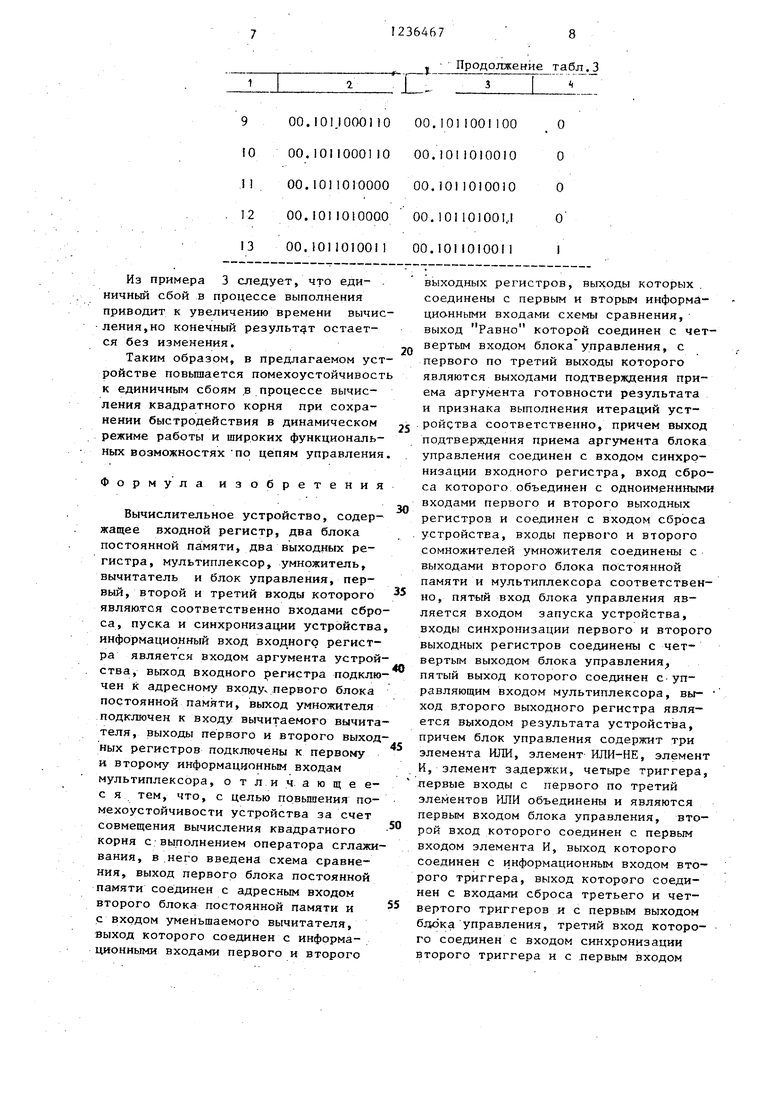

Вычисление квадратного корня в устройстве осуществляется путем вычисления дробно-рациональн ой функции R - а.0 а, X , ч /1 которая при ,3759, а,2,2293, Ь)1,6098 и Ъ ,0000 аппроксимирует функцию квадратного корня в диапазоне X е tOj25; 1,0.1 с погрешностью не более 0518%.

В устройстве организован процесс вычисления по формуле

У,, (АХ+В)- {- )у. „ (2)

где X - значение аргумента;

,

Y. - значение функции на предыду-

щем и последующем шаге вычисления;AjBjC - постоянные параметры;

i 0,1,.,., - номер шага рекурсии.

Условием окончания процесса вычисления является выполнение условия

,м i

При этом

BG Л

3

0

0

0

+СХ

в+с

А

(4;

+Х

Сравнивая выргикения ( I ) и (4 ) находим

А,5468 Q ,2608

,2293 , , , , Значения функций (АХ+В) и (), входящих в формулу (2), записаны в блоки 2 и 3 памяти соответственно. 5 Устройство работает следующим образом.

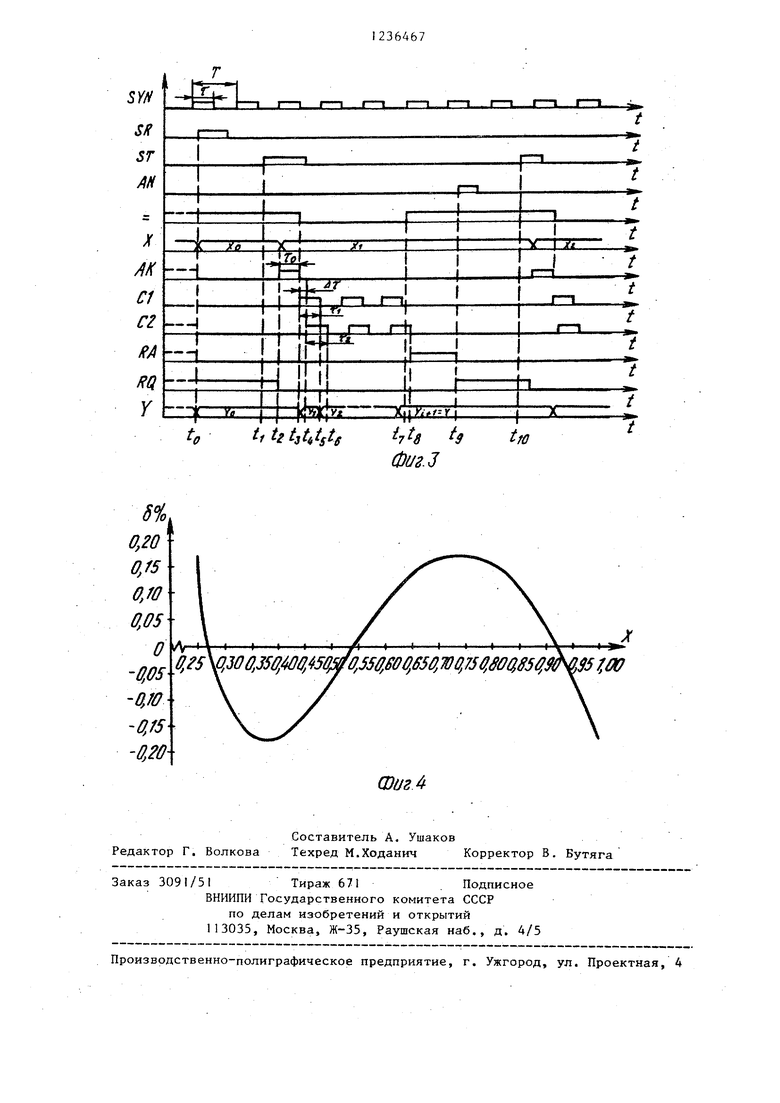

На вход 15 синхронизации поступают импульсные сигналы SYN длительностью Т и периодом следования Т (фиг. 3). В момент времени t на вход 13 поступает единичный сигнал SR, по которому Б регистрах , 6 и 7 устанавливается нулевой код, на выходах 17 и

18 устанавливают соответственно нуле- 1

- вые сигналы АК и RA, а на выходе 19 единичный сигнал RQ. Тактирующие сигналы С1 и С2 с четвертого и выходов блока 10 управления равны нулю, при этом выход мультиплексо - ра 9 подключен к выходу второго выходного регистра 7. Выходной сигнал схемы 8 сравнения равен единичному значению, так как нулевой код на выходе регистра 6 равен коду на выходе регистра 7.

Пуск устройства осуществляется единичным сигналом ST, который в момент времени t., поступает на вход 14.

При этом в момент времени t -t на выходе 17 формируется единичный сигнал АК длительностью Т -1, по переднему фронту которого значение аргу- Me}fTa X с входа 11 записьюается во входной регистр I , а выходной сигнал; RQ переходит в нулевое состояние. За время t, на выходе вычитателя 5 с учетом нулевого значения кода во

втором выходном регистре 7 формируется значение

.

В момент времени tj на четвертом выходе блока 10 управления появляет- ся единичный импульсный сигнал , Т по переднему фронту которого значение ;( 5) загтасывается в первый выходной регистр 6 и на выходе схемы 8 сравнения образуется нулевой сигнал. С задержкой at , определяемой временем записи данных в выходные регистры 6 и 7, на пятом выходе блока 10 управления формируется единичный сигнал 1, по которому выход мультиплек- сора 9 на время t. -t, подключается

ц о

к ВЫХОДУ первого выходного регистра 6, За время ti-t, на выходе вычитаЧ о

теля 5 формируется значение второго шага вычисления

АХ+В,

Y, (AX4-B)- ,

(6)

t 2 - J-i-/V А- / - ,-,

которое по заднему фронту сигнала

5

С1 в момент времени t записывается во второй выходной регистр 7. Если значение Y, Y, то на выходе схемы 8 сравнения образуется единичный сигнал, по которому вычислительный процесс заканчивается. В противном случае вычисление функции продолжается до выполнения условия (З). Пусть в момент времени t после записи данных во второй выходной регистр 7 на выходе схемы 8 сравнения образуется единичный сигнал. При этом в момент времени tj после прохождения единичного сигнала на пятом выходе блока 10 управления, сигнал RA на выходе 18 устанавливается в единичное состояние, а с четвертого и пятого выходов блока 10 управления перестают поступать тактирующие сигналы. Сигнал RA является осведомляющим сигналом для приемника информации о завершении вычислительного процесса и возможности поО

00.0000000000 00.0000000000

101.000010001 00.0000000000 о

201.0000100011 00.10001101П о

300.1100011011 OO.iOOOJlOlIl о

Q ,с

20

х 25

30

35

40

лучения значения функции с выхода 12 результата.

Во время вычислительного процесса и до момента tg выдачи результата вычисления квадратного корня в приемник информации запись нового значения аргумента в устройство блокируется блоком 10 управления. После получения результата приемник формирует в момент времени t единичный сигнал AN, который поступает на вход 16. При этом выходной сигнал RA переходит в нулевое состояние, а выходной сигнал RQ - в единичное. Данное состояние соответствует начальному состоянию устройства для выполнения следующего цикла вычисления. В отличии от исходного состояния, в которое устройство приводится по сигналу, сброса SR, здесь вычислительный процесс начинается с учетом значения функции, полученной в предыдущем цикле. Данное значение для следующего цикла вычисления, который начинается в момент времени t , является первым приближением, вследствие чего при малых приращениях аргумента время вычислительного процесса значительно меньше.

Единичный сбой, который приводит в общем случае к искажению результата на одном или нескольких элементах устройства, приводит к изменению времени вычислительного процесса, но не к искажению результата вычисления.

Пример. Вычислительный процесс начинается после установки устройства в исходное состояние сигналом SR. Значение аргумента X 0,5 (двоичное представление аргумента - .1000000000) по сигналу ST записывается во входной регистр 1 и далее вычисление происходит в соответствии с табл. 1.

Таблица 1

Погрешность моделирования равная ния изменяется на 5 % и равно сумме методической и инструментальной 0 Х 0,525(Х2 00,1000011011) . Вы числительный процесс в данном случае продолжается в соответствии с табл. 2.

погрешности,не превышает в данном примере Dj}5%,,

П р и м е р2. Значение аргумента в следующем цикле вычислеВремя вычисления функции болеемер 1) происходит сбой данных на вычем в 2,5 раза уменьшается по сравне-ходе входного регистра. Предположим,

нию с примером 1 Погрешность моде-что при этом вместо значения аргуменлирования в данном случае равна 0,13%.та X.., 00. 1000000000, на выходе приП р и м е р 3. Пусть в процессесутствует код X 00.10000011П. Вывычисления квадратного корня после числительный процесс в этом случае

вьтолнения 6-го шага рекурсии (при600.101П00010 ОО.ШПООПОО

700.101110000 00.1011001100

800.101IfOOOO 00.1011001100

1236467 4

Продолжение табл. 1

Т а б л и ц а 2

продо.пжается в соответствии с табл.3.

Т а б л и ц а 3

О О О .

Из примера 3 следует, что еди- . ничный сбой в процессе выполнения приводит к увеличению времени вычисления, но конечный результат остается без изменения.

Таким образом, в предлагаемом устройстве повышается помехоустойчивост к единичным сбоям в процессе вычисления квадратного корня при сохранении быстродействия в динамическом режиме работы и широких функциональных возможностях ПО цепям управления

Формула изобретения

Вычислительное устройство, содержащее входной регистр, два блока постоянной памяти, два выходных регистра, мультиплексор, умножитель, вычитатель и блок управления, первый, второй и третий входы которого являются соответственно входами сброса, пуска и синхронизации устройства информационный вход входного регистра является входом аргумента устройства, выход входного регистра подключен к адресному входу, первого блока постоянной памяти, выход умножителя подключен к входу вычитаемого вычита теля, выходы первого и второго выходных регистров подключены к первому и второму информационным входам мультиплексора, о т л и ч а ю щ е е- с я тем, что, с целью повьшения помехоустойчивости устройства за счет совмещения вычисления квадратного корня с выполнением оператора сглаживания, в него введена схема сравнения, выход первого блока постоянной памяти соединен с адресным входом второго блока постоянной памяти и с входом уменьшаемого вычитателя, выход которого соединен с информационными входами первого и второго

. Продолжение табл.3

20

5

0

5

0

5

0

выходных регистров, выходы которых . соединены с первым и вторым информационными входами схемы сравнения, выход Равно которой соединен с четвертым входом блока управления, с первого по третий выходы которого являются выходами подтверждения приема аргумента готовности результата и признака выполнения итераций уст- .ройства соответственно, причем выход подтверждения приема аргумента блока управления соединен с входом синхронизации входного регистра, вход сброса которого объединен с одноимениными входами первого и второго выходных регистров и соединен с входом сброса устройства, входы первого и второго сомножителей умножителя соединены с выходами второго блока постоянной памяти и мультиплексора соответственно, пятый вход блока управления является входом запуска устройства, входы синхронизации первого и второго выходных регистров соединены с четвертым выходом блока управления пятый выход которого соединен с-управляющим входом мультиплексора, вы- ход второго выходного регистра является выходом результата устройства, причем блок управления содержит три элемента ИЛИ, элемент ИЛИ-НЕ, элемент И, элемент задержки, триггера, первые входы с первого по третий элементов ИЛИ объединены и являются первьЕм входом блока управления, второй вход которого соединен с первым входом элемента И, выход которого соединен с информационным входом второго триггера, выход которого соединен с входами сброса третьего и четвертого триггеров и с первым выходом блока управления, третий вход которого соединен с входом синхронизации второго триггера и с лервым входом

элемента ИЛИ, выход которого соединен с вторым входом третьего элемента Ш1И-НЕ и через элемент задержки - с входом синхронизации первого триггера, выход которого подключен к второму входу второго элемента ИЛИ и является вторым выходом блока управления, четвертый и пятый входы которого соединены с информационным входом первого триггера и с вторым входом первого элемента ИЛИ соответственно, выход которого соединен с входом сброса первого триггера и с входом

Я

установки третьего триггера, выход которого соединен с вторым входом элемента И и является третьим выходом

блока управления, выходы второго и третьего элементов ИЛИ соединены с входом установки четвертого триггера и с входом сброса второго триггера соответственно, выход которого подключен к второму входу элемента Ш1И- НЕ, выход которого является четвертым выходом блока управления, пятый выход которого соединен с выходом элемента задержки.

jy 3730

фиг. г

10

о,го

0,Г5

о.го

0,05

-0.05 -OJO 0,Г5 -0,20

Редактор Г. Волкова

Составитель А, Ушаков

Техред М.Ходанич Корректор В. Бутяга

Заказ 3091/51 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| Преобразователь координат | 1990 |

|

SU1742816A2 |

| Устройство для вычисления полинома @ -ой степени | 1985 |

|

SU1305670A1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Устройство для воспроизведения функций | 1986 |

|

SU1348828A1 |

| Устройство для вычисления степенной функции | 1986 |

|

SU1348831A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1361547A1 |

| Система управления вибростендом | 1984 |

|

SU1275396A1 |

Изобретение относится к вычислительной технике и предназначено для аппаратной реализации операции вычисления квадратно о корня, при этом единичные сбои в процессе итера- ционшлх вычислений не вызывают искажений в конечном результате. Устройство содержит входной регистр I, два блока 2 и 3 памяти, умножитель 4, вы- читатель 5, два выходных регистра 6 и 7, схему 8 сравнения, мультиплексор 9 и блок IО управления. В устройстве реализован рекурсивный процесс вычисления по формуле Y (М+В)- -(AX+B)/CYj , где А, В, С - постоянные параметры, X - аргумент, поступающий на вход II устройства, Y ,- У- - значения функции на предыдущем и последующем шагах вычисления, формирующиеся на выходе I2.устройст-, ва, ,1,..., - номер шага вычисления. Блок 10 управления формирует сигналы, которые, кроме управления устройством, позволяют осуществить гибкое сопряжение устройства с различными вычислителями. 4 ил., 3 табл. Q % л ю ее О5 4 о:

Авторы

Даты

1986-06-07—Публикация

1984-11-05—Подача