Изобретение относится к вычислительной технике и может быть использовано для быстрого преобразования двоично-десятичного кода в двоичный код и обратно.

Известно устройство для преобразования двоично-десятичного кода в двоичный код, построенное по однотактному принципу и содержащее блок суммирования, состоящий из многовходовых одноразрядных сумматоров.

Недостатками известного устройства являются относительно низкое быстродействие и ограниченные функциональные, возможности из-за невозможности обратного преобразования кодов.

Известно также устройство для преобразования двоично-десятичного кода в двоичный код и обратно, построенное по однотактному принципу и содержащее регистр двоичного числа и последовательно соединенные каскады преобразования, каждый из которых содержит блок выделения старшей единицы, сумматор, шифратор двоично-десятичных чисел, формирователь двоичного эквивалента, девять элементов ИЛИ, девять схем сравнения и дешифратор двоично-десятичного кода.

Недостатками известного устройства являются относительное низкое быстродействие и большое количество аппаратуры.

Наиболее близким к предлагаемому является устройство для преобразования двоично-десятичного кода в двоичный код и обратно, построенное по многотактному принципу и содержащее двоичный регистр, две группы коммутаторов, группу формирователей тетрадных эквивалентов, блок суммирования, блок сравнения и распределитель импульсов, причем шины двоичного числа соединены с первыми информационными входами коммутаторов первой группы, вторые информационные входы которых соединены с выходами распределителя ИМПУЛЬСОВ, ВЫХОДЫ KOMMVT3TO(Л

С

XJ

сл ел со

XI

сл

ров первой группы соединены с информационными входами двоичного регистра, выходы которого соединены с первыми информационными входами коммутаторов второй группы, вторые информационные входы которых соединены с выходами распределителя импульсов, выходы коммутаторов второй группы соединены с входами формирователей эквивалентов группы, выходы которых соединены с информационными входами блока суммирования, выходы которого соединены с информационными входами первой группы блока сравнения, информационные входы второй группы которого соединены с шинами двоично-десятичного числа, управляющие входы коммутаторов первой и второй группы соединены с входом задания режима устройства.

Недостатком известного устройства является низкое быстродействие.

Цель изобретения - повышение быстродействия устройства

Поставленная цель достигается тем, что в устройство для преобразования двоично- десятичного кода в двоичный код и обратно, содержащее группу формирователей тетрадных эквивалентов, группу коммутаторов и блок суммирования, причем выход блока суммирования является выходом устройства, вход задания режима которого соединен с управляющими входами коммутаторов группы, введены группа узлов тетрадного суммирования и группа узлов преобразования двоичногб кода в десятичный код, причем информационные входы группы устройства соединены с информационными входами соответствующих формирователей тетрадных эквивалентов группы, выходы которых соединены с входами соответствующих узлов тетрадного суммирования группы, выходы которых соединены с первыми информационными входами соответствующих коммутаторов группы и входами соответствующих узлов преобразования двоичного кода в десятичный код группы, выходы которых соединены с вторыми информационными входами соответствующих коммутаторов группы, выходы которых соединены с входами соответствующих слагаемых блока суммирования, вход задания режима которого соединен с входами задания режима формирователей тетрадных эквивалентов группы и с входом задания режима устройства

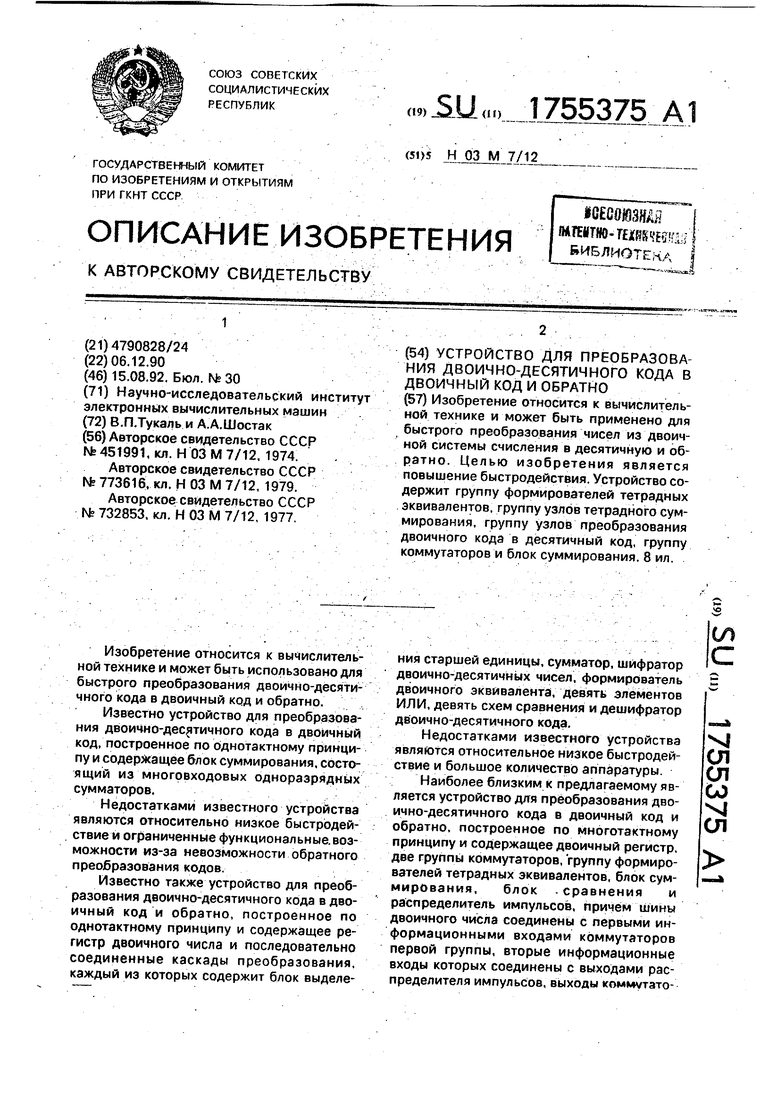

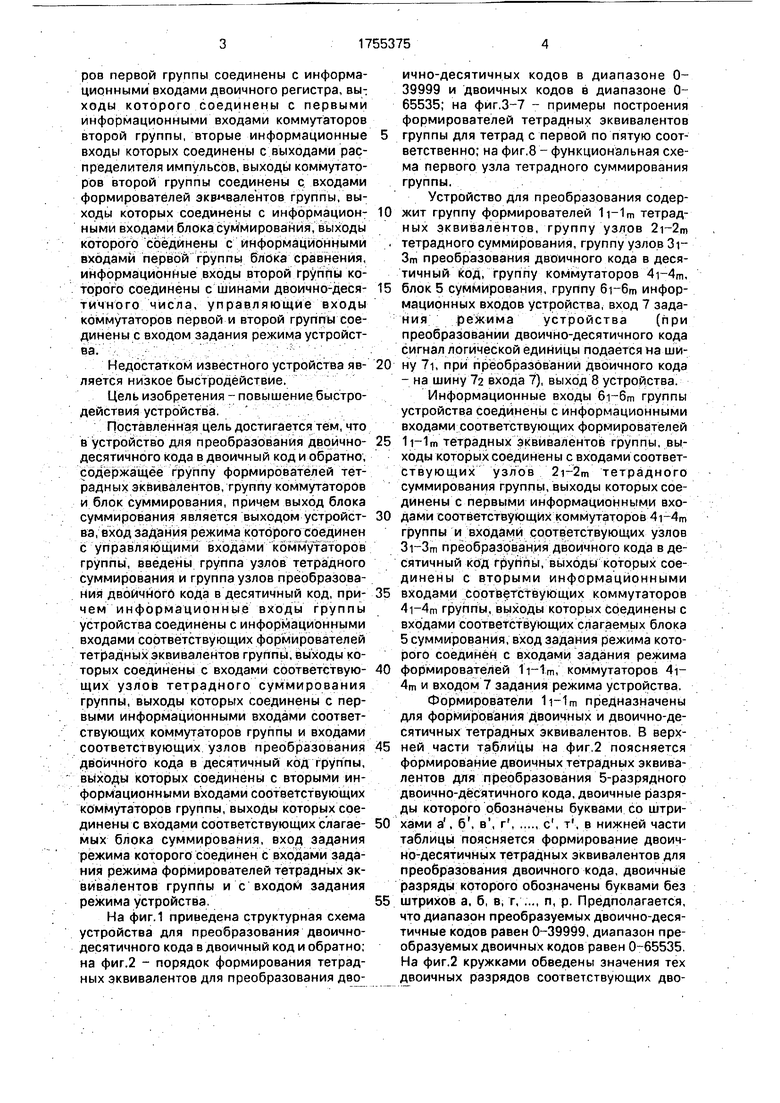

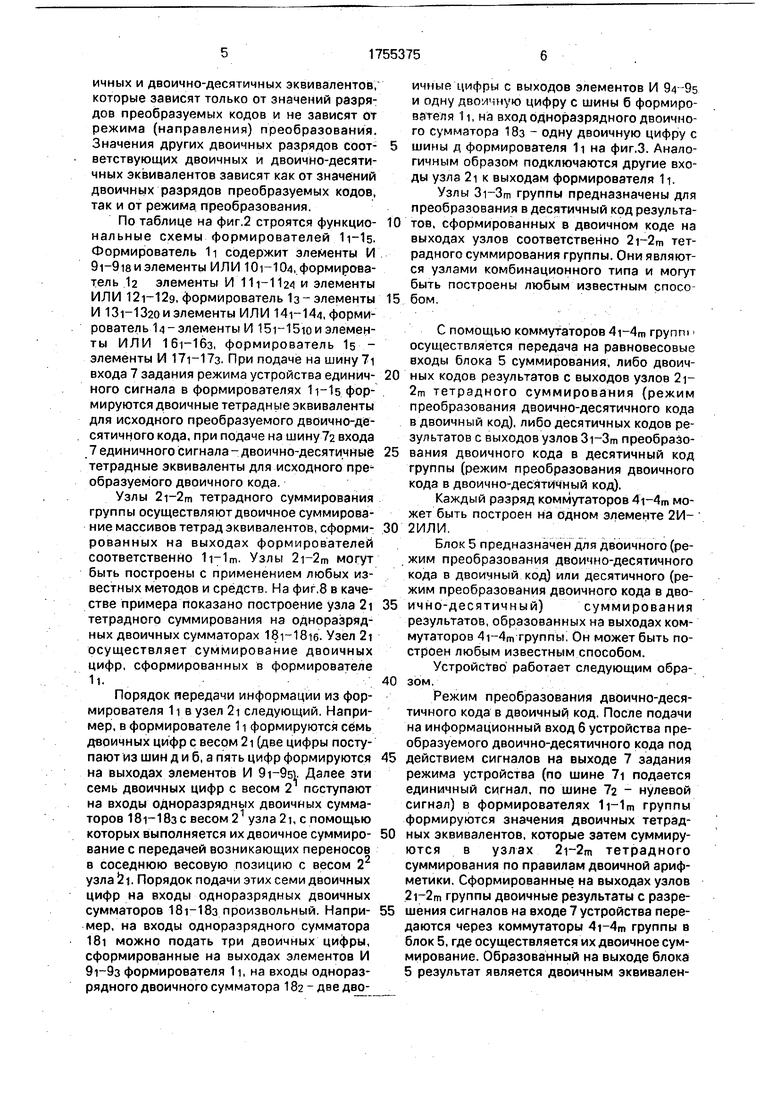

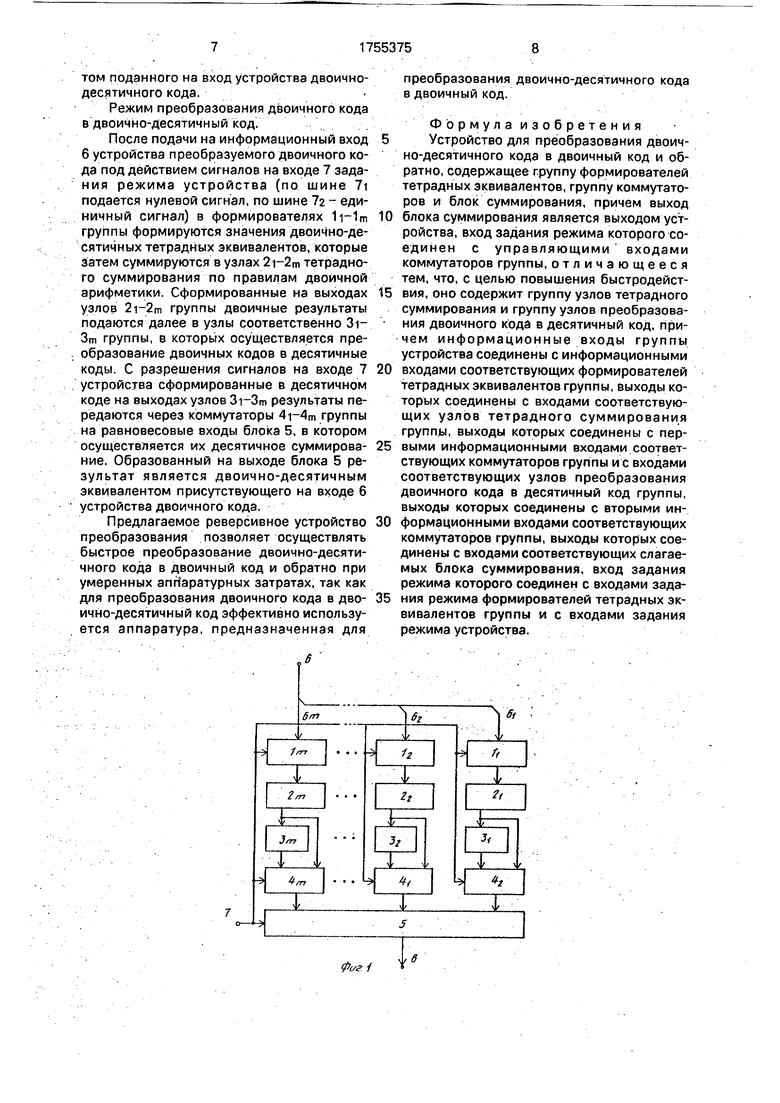

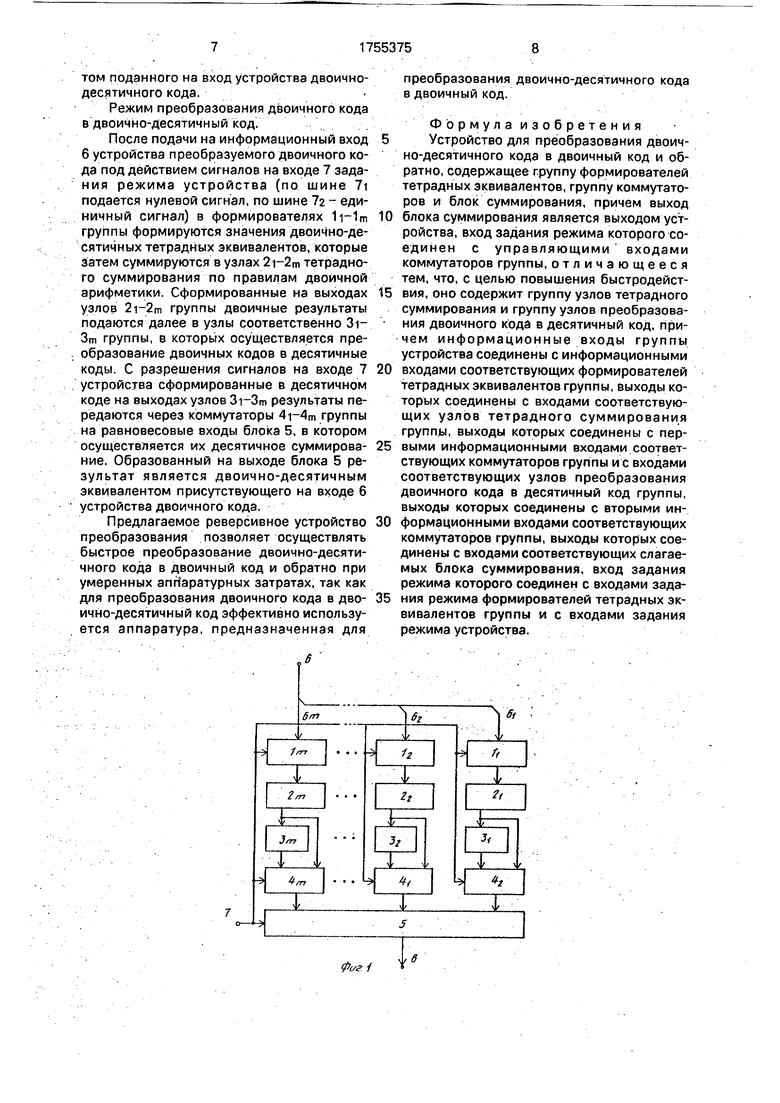

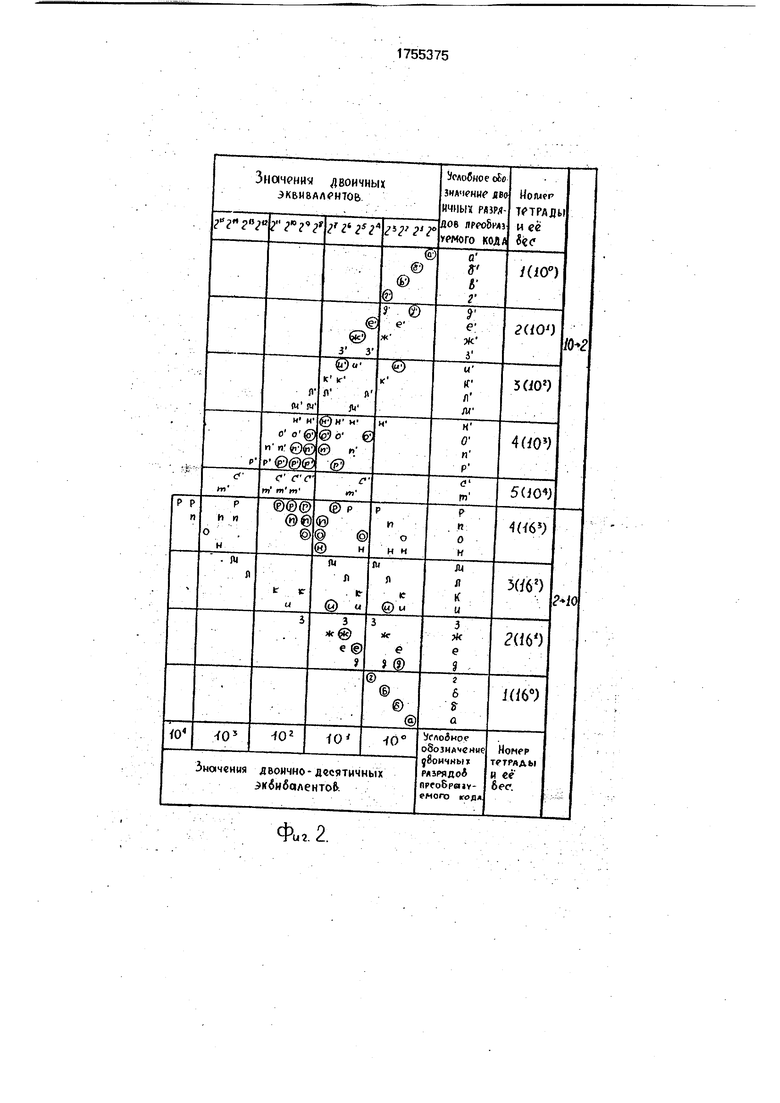

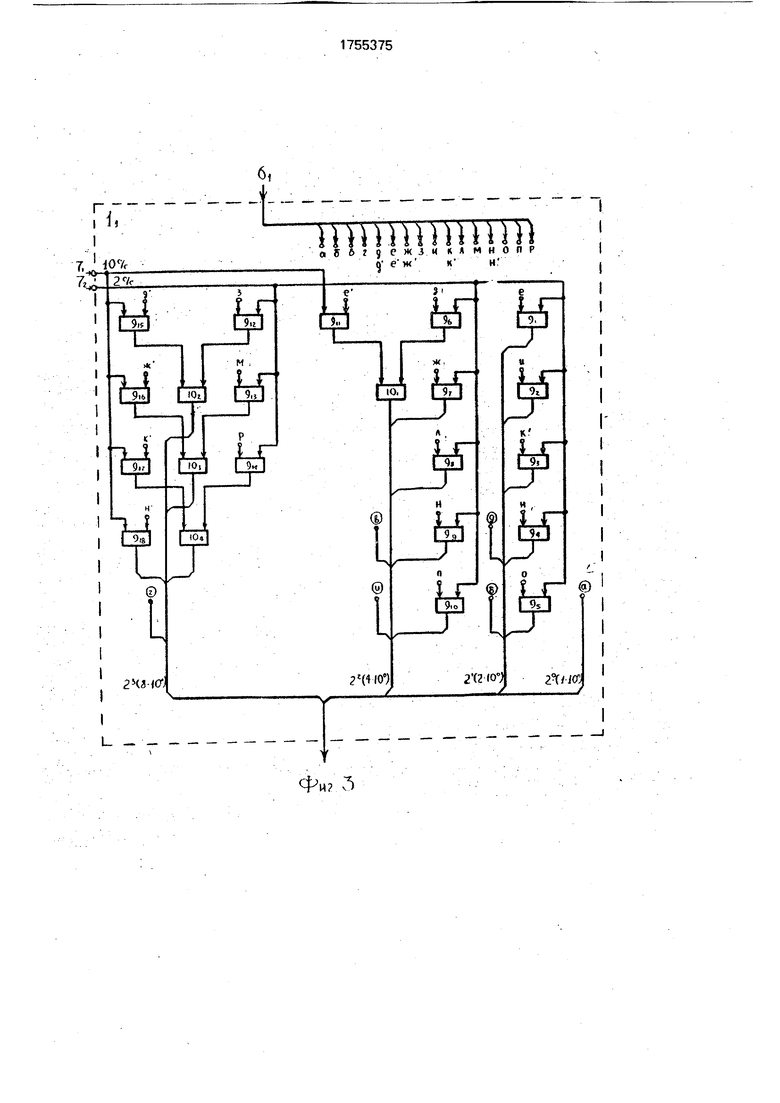

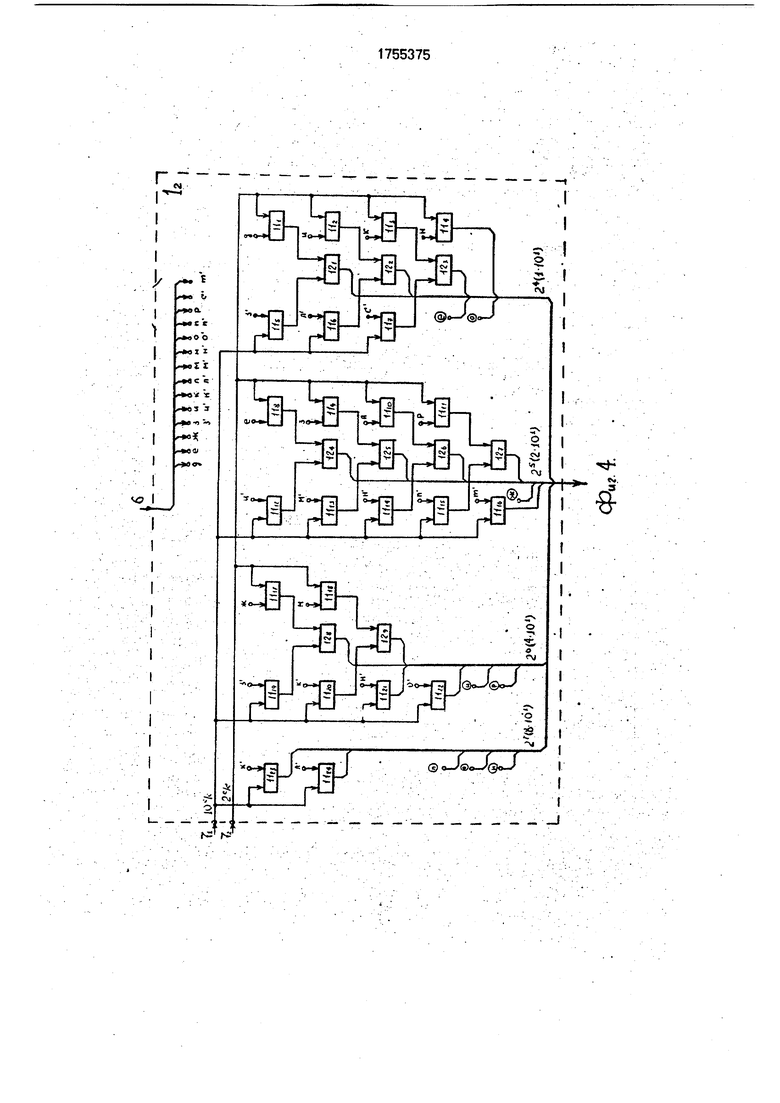

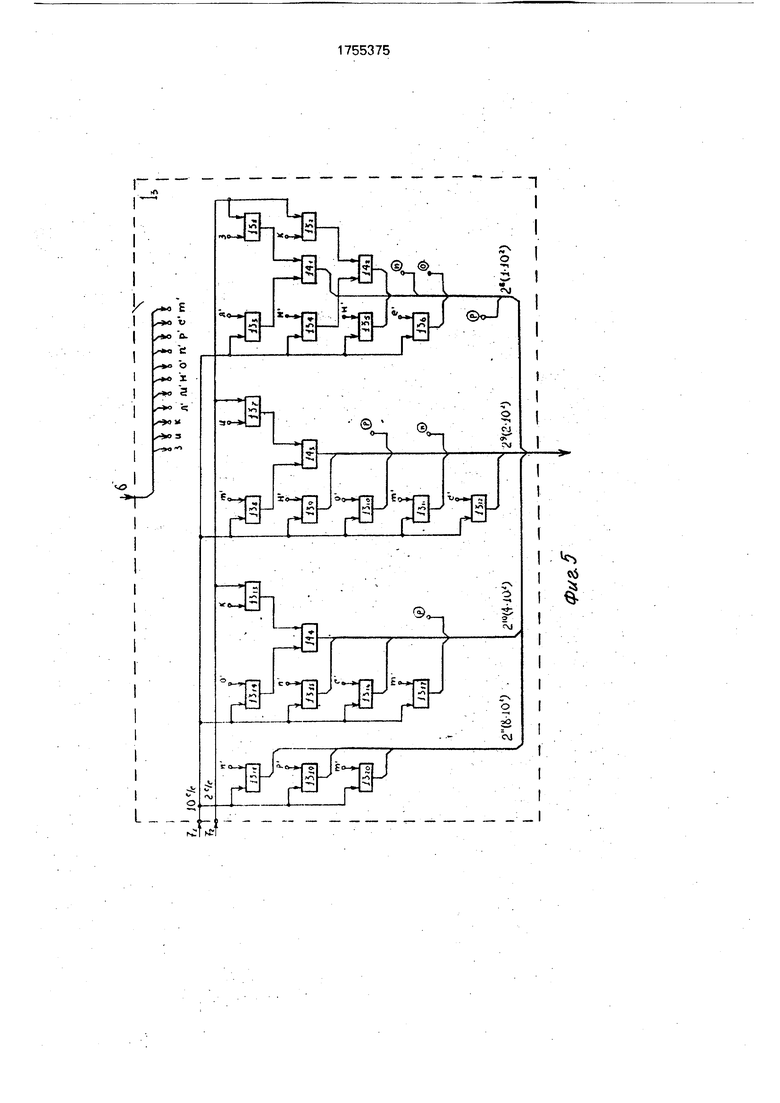

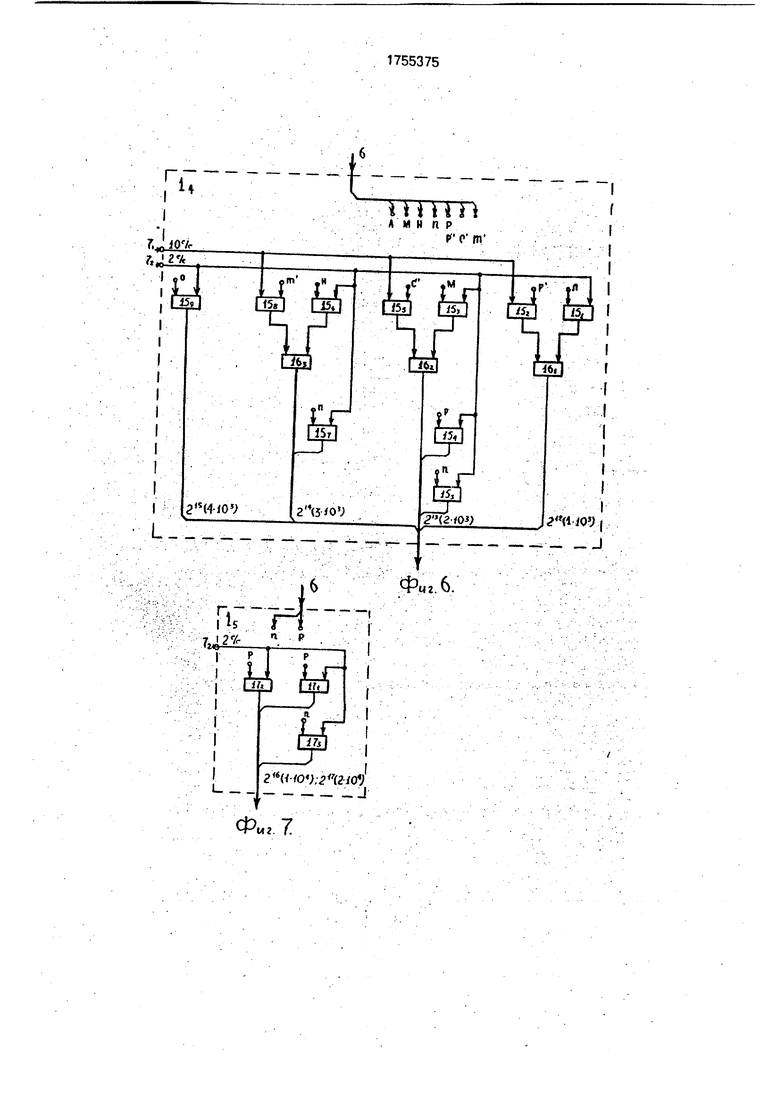

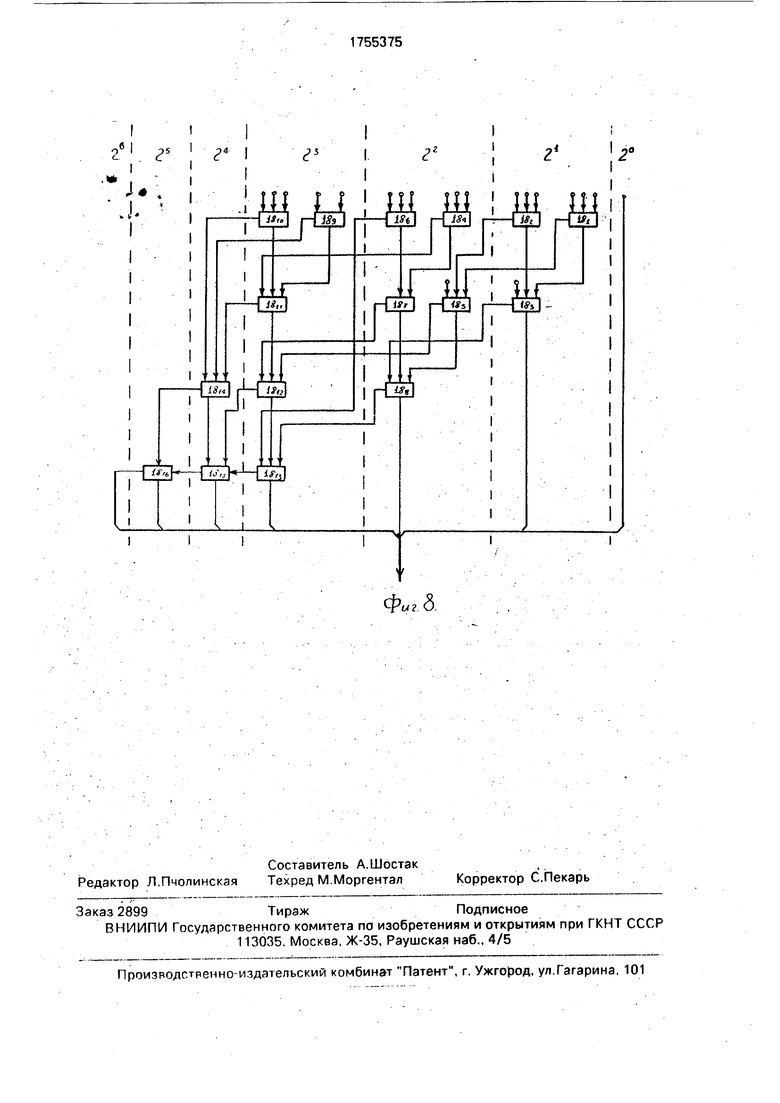

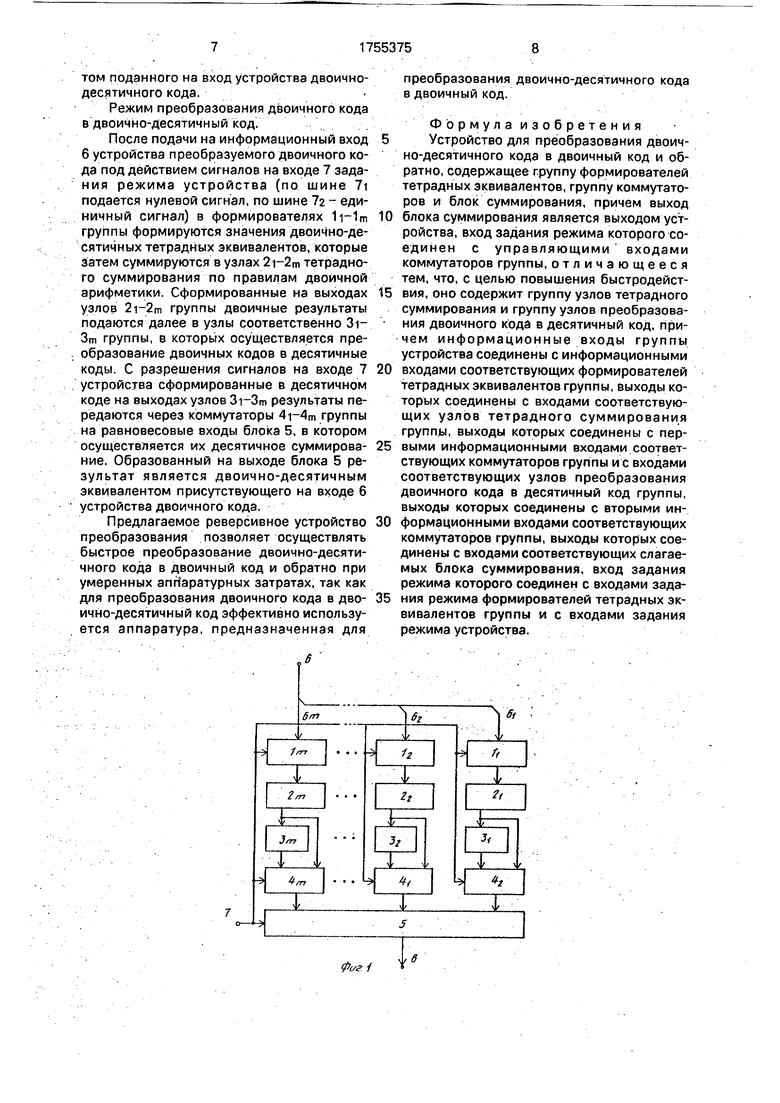

На фиг.1 приведена структурная схема устройства для преобразования двоично- десятичного кода в двоичный код и обратно, на фиг.2 - порядок формирования тетрадных эквивалентов для преобразования двоично-десятичных кодов в диапазоне 0- 39999 и двоичных кодов в диапазоне 0- 65535; на фиг 3-7 - примеры построения формирователей тетрадных эквивалентов группы для тетрад с первой по пятую соответственно; на фиг 8 - функциональная схема первого узла тетрадного суммирования группы.

Устройство для преобразования содер0 жит группу формирователей 1i-1m тетрадных эквивалентов, группу узлов 2i-2m . тетрадного суммирования, группу узлов 3i- 3m преобразования двоичного кода в десятичный код, группу коммутаторов 4-|-4т,

5 блок 5 суммирования, группу 6i-6m информационных входов устройства, вход 7 задания режима устройства (при преобразовании двоично-десятичного кода сигнал логической единицы подается на ши0 ну 7i, при преобразовании двоичного кода - на шину 72 входа 7), выход 8 устройства.

Информационные входы 6i-6m группы устройства соединены с информационными входами соответствующих формирователей

5 1i-1m тетрадных эквивалентов группы, выходы которых соединены с входами соответ- ствующих узлов 2i-2m тетрадного суммирования группы, выходы которых соединены с первыми информационными вхо0 дами соответствующих коммутаторов 4i-4m группы и входами соответствующих узлов 3i-3m преобразования двоичного кода в десятичный код группы, выходы которых соединены с вторыми информационными

5 входами соответствующих коммутаторов 4-|-4т группы, выходы которых соединены с входами соответствующих слагаемых блока 5 суммирования, вход задания режима которого соединен с входами задания режима

0 формирователей 1i-1m, коммутаторов 4i- 4m и входом 7 задания режима устройства. Формирователи 1i-1m предназначены для формирования двоичных и двоично-десятичных тетрадных эквивалентов В верх5 ней части таблицы на фиг 2 поясняется формирование двоичных тетрадных эквивалентов для преобразования 5-разрядного двоично-десятичного кода, двоичные разряды которого обозначены буквами со штри0 хами а , б , в , г , . .., с , т1, в нижней части таблицы поясняется формирование двоично-десятичных тетрадных эквивалентов для преобразования двоичного кода, двоичные разряды которого обозначены буквами без

5 штрихов а, б, в, гп, р. Предполагается,

что диапазон преобразуемых двоично-десятичные кодов равен 0-39999, диапазон преобразуемых двоичных кодов равен 0-65535 На фиг.2 кружками обведены значения тех двоичных разрядов соответствующих двоичных и двоично-десятичных эквивалентов, которые зависят только от значений разрядов преобразуемых кодов и не зависят от режима (направления) преобразования. Значения других двоичных разрядов соответствующих двоичных и двоично-десятичных эквивалентов зависят как от значений двоичных разрядов преобразуемых кодов, так и от режима преобразования.

По таблице на фиг.2 строятся функцио- нальные схемы формирователей 1i-l5. Формирователь 1i содержит элементы И 9i-9i8 и элементы ИЛИ 10i-104, формирователь 12 элементы И 111-1124 и элементы ИЛИ 12i-12g, формирователь 1з - элементы И 131-1320 и элементы ИЛИ 141-144, формирователь 1 -элементы И 15i-15io и элементы ИЛИ , формирователь 1g - элементы И 17ч-17з. При подаче на шину 7 входа 7 задания режима устройства единичного сигнала в формирователях 1i-1s формируются двоичные тетрадные эквиваленты для исходного преобразуемого двоично-десятичного кода, при подаче на шину7а входа 7 единичного сигнала-двоично-десятичные тетрадные эквиваленты для исходного преобразуемого двоичного кода.

Узлы 2t-2m тетрадного суммирования группы осуществляют двоичное суммирование массивов тетрад эквивалентов, сформи- рованных на выходах формирователей соответственно 1i-1m. Узлы 2i-2m могут быть построены с применением любых известных методов и средств. На фиг.8 в качестве примера показано построение узла 2i тетрадного суммирования на одноразрядных двоичных сумматорах 18i-18ie. Узел 2i осуществляет суммирование двоичных цифр, сформированных в формирователе 1i.

Порядок передачи информации из формирователя 1i в узел 2i следующий. Например, в формирователе 11 формируются семь двоичных цифр с весом 21 (две цифры поступают из шин д и б, а пять цифр формируются на выходах элементов И 9i-9si. Далее эти семь двоичных цифр с весом 2 поступают на входы одноразрядных двоичных сумматоров весом 2 узла 2i, с помощью которых выполняется их двоичное суммирование с передачей возникающих переносов в соседнюю весовую позицию с весом 2 узла 2i. Порядок подачи этих семи двоичных цифр на входы одноразрядных двоичных сумматоров 18i-18s произвольный. Например, на входы одноразрядного сумматора 18i можно подать три двоичных цифры, сформированные на выходах элементов И формирователя 1i, на входы одноразрядного двоичного сумматора 182 - две двоичные цифры с выходов элементов И 94-9s и одну двоичную цифру с шины б формирователя 1i, на вход одноразрядного двоичного сумматора 18з - одну двоичную цифру с

шины д формирователя 1i на фиг.З. Аналогичным образом подключаются другие входы узла 2i к выходам формирователя 1-|.

Узлы группы предназначены для преобразования в десятичный код результатов, сформированных в двоичном коде на выходах узлов соответственно 2i-2m тетрадного суммирования группы. Они являются узлами комбинационного типа и могут быть построены любым известным спосо

бом.

С помощью коммутаторов 4i-4m rpynm осуществляется передача на равновесовые входы блока 5 суммирования, либо двоичных кодов результатов с выходов узлов 2i- 2m тетрадного суммирования (режим преобразования двоично-десятичного кода в двоичный код), либо десятичных кодов результатов с выходов узлов 3i-3m преобразования двоичного кода в десятичный код группы (режим преобразования двоичного кода в двоично-десятичный код).

Каждый разряд коммутаторов 4i-4m может быть построен на одном элементе 2И2ИЛИ.

Блок 5 предназначен для двоичного (режим преобразования двоично-десятичного кода в двоичный код) или десятичного (режим преобразования двоичного кода в двоично-десятичный)суммирования

результатов, образованных на выходах коммутаторов 4i-4m группы, Он может быть построен любым известным способом.

Устройство работает следующим образом.

Режим преобразования двоично-десятичного кода в двоичный код. После подачи на информационный вход 6 устройства преобразуемого двоично-десятичного кода под

действием сигналов на выходе 7 задания режима устройства (по шине 7i подается единичный сигнал, по шине 72 - нулевой сигнал) в формирователях группы формируются значения двоичных тетрадных эквивалентов, которые затем суммируются в узлах 2i-2m тетрадного суммирования по правилам двоичной арифметики. Сформированные на выходах узлов 2i-2m группы двоичные результаты с разрешения сигналов на входе 7 устройства передаются через коммутаторы 4i-4m группы в блок 5, где осуществляется их двоичное суммирование. Образованный на выходе блока 5 результат является двоичным эквивалентом поданного на вход устройства двоично- десятичного кода.

Режим преобразования двоичного кода в двоично-десятичный код.

После подачи на информационный вход 6 устройства преобразуемого двоичного кода под действием сигналов на входе 7 зада- ния режима устройства (по шине 7i подается нулевой сигнал, по шине 1г - единичный сигнал) в формирователях 1i-1m группы формируются значения двоично-десятичных тетрадных эквивалентов, которые затем суммируются в узлах 2i-2m тетрадного суммирования по правилам двоичной арифметики. Сформированные на выходах узлов 2ч-2т группы двоичные результаты подаются далее в узлы соответственно 3i- 3m группы, в которых осуществляется преобразование двоичных кодов в десятичные коды. С разрешения сигналов на входе 7 устройства сформированные в десятичном коде на выходах узлов 3i-3m результаты передаются через коммутаторы 4i-4m группы на равновесовые входы блока 5, в котором осуществляется их десятичное суммирова- ние. Образованный на выходе блока 5 результат является двоично-десятичным эквивалентом присутствующего на входе б устройства двоичного кода.

Предлагаемое реверсивное устройство преобразования позволяет осуществлять быстрое преобразование двоично-десятичного кода в двоичный код и обратно при умеренных аппаратурных затратах, так как для преобразования двоичного кода в дво- ично-десятичный код эффективно используется аппаратура, предназначенная для

преобразования двоично-десятичного кода в двоичный код.

Ф о р м у л а и з о б р е т е н и я Устройство для преобразования двоично-десятичного кода в двоичный код и обратно, содержащее группу формирователей тетрадных эквивалентов, группу коммутаторов и блок суммирования, причем выход блока суммирования является выходом устройства, вход задания режима которого соединен с управляющими входами коммутаторов группы, отличающееся тем, что, с целью повышения быстродействия, оно содержит группу узлов тетрадного суммирования и группу узлов преобразования двоичного кода в десятичный код, причем информационные входы группы устройства соединены с информационными входами соответствующих формирователей тетрадных эквивалентов группы, выходы которых соединены с входами соответствующих узлов тетрадного суммирования группы, выходы которых соединены с первыми информационными входами соответствующих коммутаторов группы и с входами соответствующих узлов преобразования двоичного кода в десятичный код группы, выходы которых соединены с вторыми информационными входами соответствующих коммутаторов группы, выходы которых соединены с входами соответствующих слагаемых блока суммирования, вход задания режима которого соединен с входами задания режима формирователей тетрадных эквивалентов группы и с входами задания режима устройства,

Фиг 2.

f (.01 EX

(,ои)гг

ил гх

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1624698A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Двоично-десятичный сумматор | 1990 |

|

SU1728859A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU883893A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| РЕВЕРСИВНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ | 1990 |

|

RU2022467C1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1649672A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

Изобретение относится к вычислительной технике и может быть применено для быстрого преобразования чисел из двоичной системы счисления в десятичную и обратно. Целью изобретения является повышение быстродействия. Устройство содержит группу формирователей тетрадных эквивалентов, группу узлов тетрадного суммирования, группу узлов преобразования двоичного кода в десятичный код, группу коммутаторов и блок суммирования. 8 ил.

®

J4

,

п

л -и

э.«

О

,н .х ,ж.э .&

dUOHWVH НГЖОб2 7Д

шншшши

г

оГ|

о

JF

r-Jl

J

Wj

w

,д

Jfl

ллг

VoO

НК

zz

т

19

:,

SiC9SIl

X. Ј

a L -MO.

c V

eOO

el i oЈZ

4C с 4OV Т J t-n

r -on

0«

IhlpByEbi

:EH

«

5K. $K K $K

l- JipLTii- LqpLq

Г

«

:EH

н

®JI

sю

-- СО Ю LD Г.X.

о4

L

П

I

Г

n p

I Г

ҐJLf1 Пр

i

)

Фмг 7

Фмг.6.

Фыг 3

| Устройство для преобразования двоично-десятичного кода в двоичный | 1973 |

|

SU451991A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1979 |

|

SU773616A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1977 |

|

SU732853A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-08-15—Публикация

1990-12-06—Подача