Изобретение относится к вычислите. ной технике, а именно к множительно-де- лительным устройствам ЭВМ, и может быть использовано для построения специализированных быстродействующих вычислительных устройств, а также при разработке быстродействующих устройств деления, удобных для изготовления в составе больших интегральных схем (БИС).

Цель изобретения - повышение быстродействия устройства.

На чертеже показана блок-схема устройства для деления.

Устройство содержит первый 1 и второй 2 входные регистры. Первый 3 и второй 4 блоки памяти, блок 5 вычитания, первый 6 и второй 7 промежуточные регистры, перемножитель 8, выходной регистр 9, вход 10 делимого, вход 11 делителя, выход 12 частного, тактовый вход 13.

В устройстве реализован метод деления, заключающийся в предварительном определении обратной величины С делите тя X и последующем ее умножении на Y. При этом предполагается, что входными операндами делимого и делителя является п-раз- рядные положительные двоичные числа, у которых запятая фиксирована после одного разряда целой части, причем в целой части делителя всегда содержится единица, т.е. . Одним из методов вычисления функции С 1/Х является методом кусочно-линейной аппроксимации, в соответствии с которым диапазон изменения аргумента разбивается на интервалы, количество которых определяется требуемой точностью. При этом

,-(X,-Хо/),

где Хо/ - значение аргумента Х,- в начальной (опорной) точке j-ro интервала аппроксимации;

Со; - опорное значение обратной величины С; на J-M интервале аппроксимаци;

М;- значение тангенса угла наклона j-ro отрезка аппроксимации функции С 1/Х к оси абсцисс;

i 0,1,2,.., -1 (п - разрядность входных операндов делимого и делителя);

,l,2,...,2-1 (f- количество старших разрядов дробной части делителя, по которым определяются значения величин Со, и М/.

В предлагаемом устройстве для достижения абсолютной погрешности | . 2

каждый из интервалов аппроксимации развивается на подынтервалы. В этом случае функция С, определяется выражением

С; Сох М/(Х,-XOH) Сок-В;,

где Хок - значение аргумента X,- в начальной (опорной) точке К-го подынтервала;

Со« - опорное значение обратной величины С; на К-м подынтервале;

В, - значение поправки к обратной величине аргумента X,-;

К 0,1,3,..., (т {, m - количество старших разрядов дробной части делителя, по которым определяется значение величины Сох).

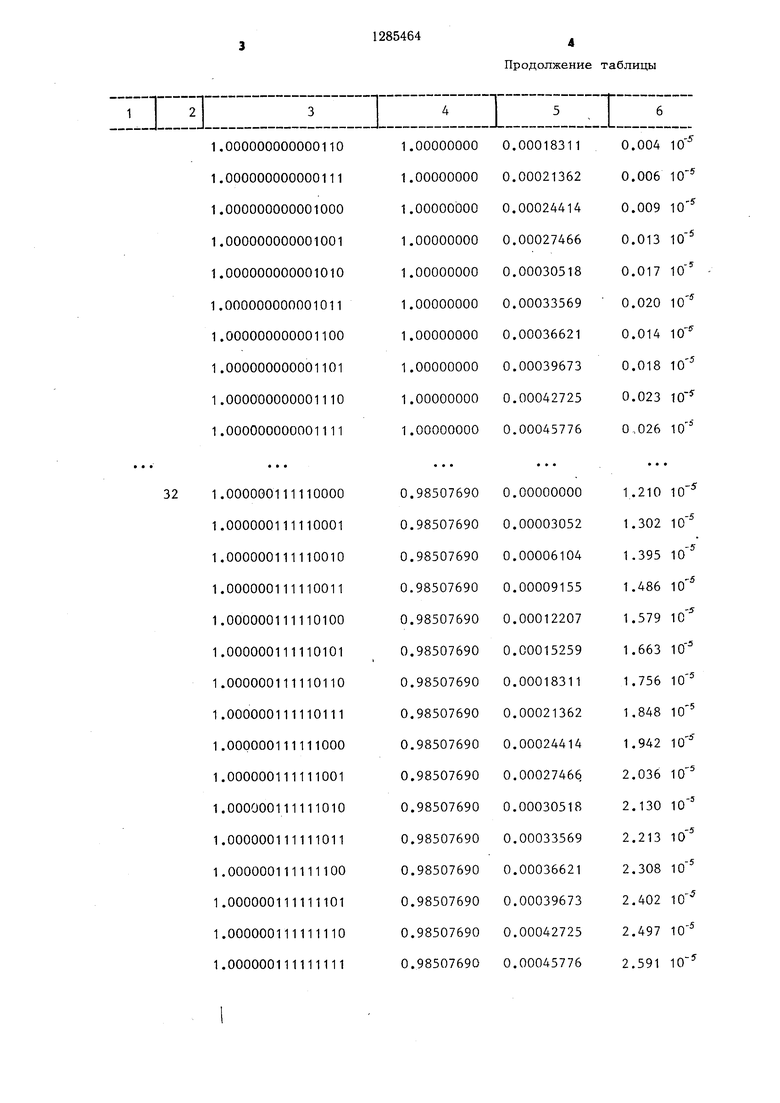

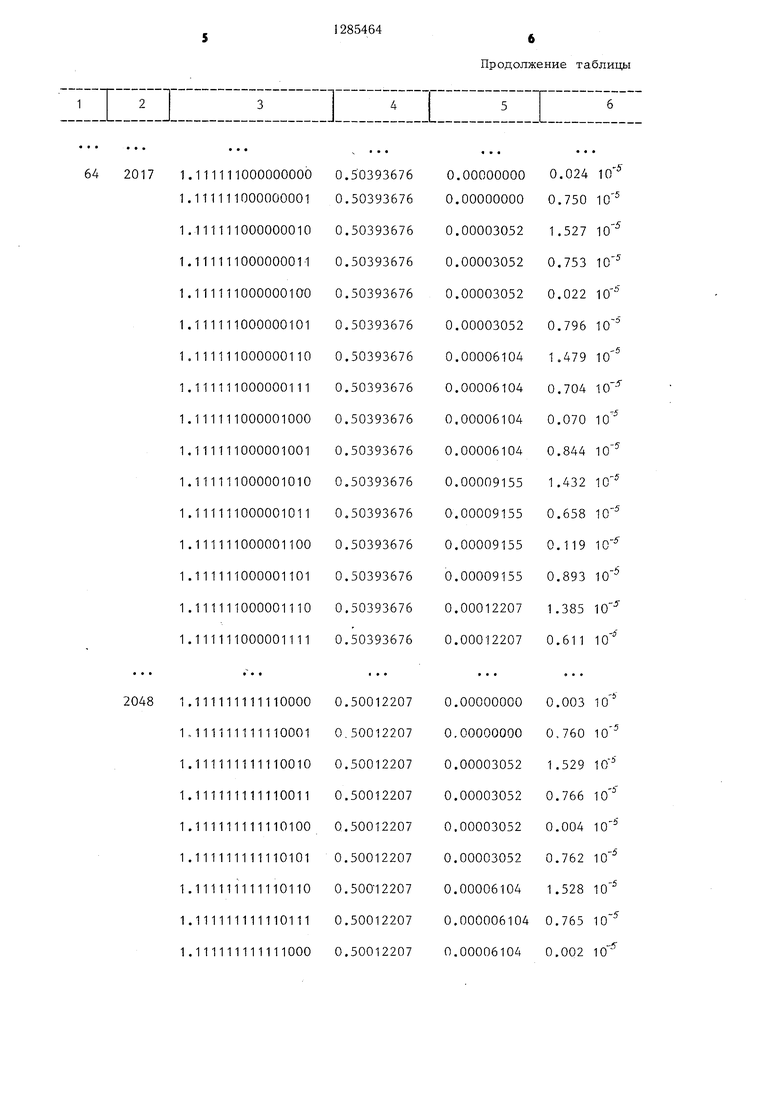

Для входных операндов с 15-разрядной дробной частью при ш 11 и 1 6, т.е. при разбиении диапазона изменения аргумента X на 64 интервала аппроксимаци, каждый из которых в свою очередь развивается на 32 подынтервала, точность достигает значения i Лша; 1 , что видно из таблицы.

Продолжение таблицы

Продолжение таблицы

гп

Устройство работает следующим образом.

По приходу первого тактового импульса на вход 13 устройства величины Y и X записываются соответственно регистры 1 и 2. По адресу, указанному m старшими разрядами дробной части X, из блока 3 постоянной памяти выбирается опорное значение обратной величины Сок, которое поступает на вход уменьшаемого блока 5. Одновременно по адресу, указанному t старшими и (п-m-1) младшими разрядами дробной части X, из блока 4 выбирается значение поправки В, к обратной величине Сок , которое поступает на вход вычитаемого блока 5. В блоке 5 производится вычисление разности (Сок--В/), представляющей собой уточненное значение обратной величины делителя. По приходу второго тактового импульса это выражение записывается в регистр 7. Одновременно в регистр 6 записывается величина Y.

Содержимое регистров 6 и 7 поступает на перемножитель 8, на выхбде которого формируется искомое частное Z Y-l/X. По приходу третьего тактового импульса полученное число записывается в регистр 9 и из него поступает на выход устройства. Формула изобретения

Устройство для деления, содержащее первый и второй входные регистры, первый и второй блоки памяти, первый и второй

Продолжение таблицы

0

промежуточные регистры, перемножитель и выходной регистр, причем информационные входы первого и второго входных регистров являются входами делимого и делите5 ля устройства, выход первого входного регистра соединен с информационным входом первого промежуточного регистра, выход которого соединен с входом первого сомножителя перемножителя, выход которого соединен с информационным входом выходного регистра, выход которого является выходом частного устройства, выход второго промежуточного регистра соединен с входом второго сомножителя перемножителя, тактовый вход устройства соединен с тактовыми входами первого и второго входных регистров, первого и второго промежуточных регистров и выходного регистра, отличающееся тем, что, с целью повышения быстродействия, в него введен блок вычитания, выход которого соединен с информацион0 ным входом второго промежуточного регистра, первая и вторая группа выходов второго входного регистра соединены с первым и вторым адресными входами первого блока памяти, выход которого соединен с входом уменьшаемого блока вычитания, вход вычитаемого которого соединен с выходом второго блока памяти, первый и второй адресные входы которого соединены с первой и третьей группой выходов второго входного регистра.

5

/3

W

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1986 |

|

SU1397903A1 |

| Устройство вычисления функции арктангенс отношения | 1988 |

|

SU1585793A1 |

| Устройство для деления | 1981 |

|

SU987621A1 |

| Вычислительное устройство | 1989 |

|

SU1691837A1 |

| Устройство для вычисления функции арктангенса отношения | 1988 |

|

SU1615709A1 |

| Устройство для вычисления функции арктангенса отношения | 1990 |

|

SU1751750A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления | 1977 |

|

SU732865A1 |

| УСТРОЙСТВО ДЛЯ ОСНОВНОГО ДЕЛЕНИЯ МОДУЛЯРНЫХ ЧИСЕЛ | 2013 |

|

RU2559771C2 |

| Устройство для деления | 1985 |

|

SU1339553A1 |

Изобретение относится к вычислительной технике, а именно к множительно- делительным устройствам ЭВМ, и может быть использовано для построения быстродействующих специализированных вычислительных устройств, а также при разработке быстродействующих устройств деления, удобных для изготовления в составе боль- щих интегральных схем ((БИС). Известные устройства для деления нормализованных в положительных чисел, представленных в формате с фиксированной запятой, имеют ограниченное быстродействие вследствие большого числа тактов вычислительного процесса. В устройство с целью повышения быстродействия введен блок вычитания, что дает возможность за один такт вычислять скорректированное значение обратной величины делителя. Это позволяет повысить быстродействие устройства с одновременным его упрощением. 1 табл., I ил. IsD 00 01 4 05

| УСТРОЙСТВО для ДЕЛЕНИЯ | 0 |

|

SU305475A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1981 |

|

SU987621A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-23—Публикация

1985-05-29—Подача