Изобретение относится к цифровой вычислительной технике и может быть использовано в оперативных запоминающих устройствах.

Цель изобретения - повышение по- мехозащищенности ячейки памяти при действии напряжения на адресном входе.

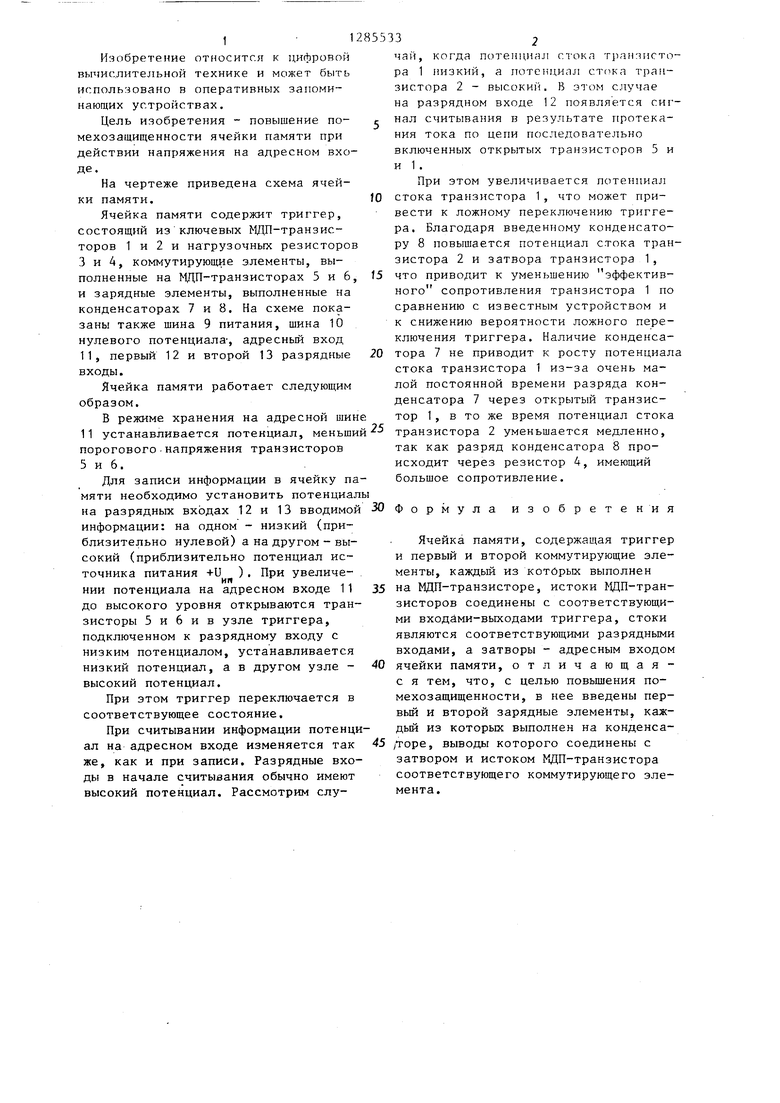

На чертеже приведена схема ячейки памяти.

Ячейка памяти содержит триггер, состоящий из ключевых МДП-транзис- торов 1 и 2 и нагрузочных резисторов 3 и А, коммутирующие элементы, выполненные на МДП-транзисторах 5 и 6, и зарядные элементы, выполненные на конденсаторах 7 и 8. На схеме показаны также шина 9 питания, шина 10 нулевого потенциала-, адресный вход 11, первый 12 и второй 13 разрядные входы.

Ячейка памяти работает следующим образом.

В режиме хранения на адресной шин 11 устанавливается потенциал, меньши пороговогонапряжения транзисторов 5 и 6.

Для записи информации в ячейку памяти необходимо установить потенциал на разрядных входах 12 и 13 вводимой информации: на одном - низкий (приблизительно нулевой) а на другом - высокий (приблизительно потенциал источника питания +U )t При увеличеияНИИ потенциала на адресном входе 11

до высокого уровня открываются транзисторы 5 и 6 и в узле триггера, подключенном к разрядному входу с низким потенциалом, устанавливается низкий потенциал, а в другом узле - высокий потенциал.

При этом триггер переключается в соответствующее состояние.

При считывании информации потенциал на адресном входе изменяется так 45 /торе, выводы которого соединены с

же, как и при записи. Разрядные входы в начале считывания обычно имеют высокий потенциал. Рассмотрим случаи, когда потенциал стокл транписто ра 1 низкий, а потенципл транзистора 2 - высокий. В этом случае на разрядном входе 12 появляется сигнал считывания в результате протекания тока по цепи последовательно включенных открытых транзисторов 5 и и 1 .

При этом увеличивается потенциал стока транзистора 1, что может привести к ложному переключению триггера. Благодаря введенному конденсатору 8 повышается потенциал стока транзистора 2 и затвора транзистора 1, что приводит к уменьшению эффективного сопротивления транзистора 1 по сравнению с известным устройством и к снижению вероятности ложного переключения триггера. Наличие конденсатора 7 не приводит к росту потенциал стока транзистора 1 из-за очень малой постоянной времени разряда конденсатора 7 через открытый транзистор 1, в то же время потенциал стока транзистора 2 уменьшается медленно, так как разряд конденсатора 8 происходит через резистор 4, имеющий большое сопротивление.

Формула изобретения

Ячейка памяти, содержащая триггер и первый и второй коммутирующие элементы, каждый из которых выполнен на ВДП-транзисторе, истоки ВДП-тран- зисторов соединены с соответствующими входами-выходами триггера, стоки являются соответствующими разрядными входами, а затворы - адресным входом ячейки памяти, отличающая- с я тем, что, с целью повъшения помехозащищенности, в нее введены первый и второй зарядные элементы, каж- дьй из которых выполнен на конденсазатвором и истоком МДП-транзистора соответствующего коммутирующего элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1465911A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Усилитель считывания | 1979 |

|

SU858093A1 |

| ЯЧЕЙКА ПАМЯТИ | 1985 |

|

RU1318096C |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1115106A1 |

| Квазистатическая ячейка памяти | 1974 |

|

SU541197A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| Усилитель считывания на мдп-транзисторах | 1978 |

|

SU721852A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в оперативных запоминающих устройствах. Целью изобретения является повышение помехозащищенности ячейки памяти при действии напряжения на адресном входе. Для достижения этой цели в ячейку памяти введены два накопительных конденсатора,которые включены между адресным входом ячейки памяти и узловыми точками триггера ячейки памяти. Благодаря конденсаторам при действии сигнала на адресном входе повьшается потенциал затвора открытого МДП-транзистора триггера, что приводит к уменьшению эффективного сопротивления транзистора и снижению вероятности, ложного пере- ключения триггера. 1 ил. (Л N9 00 ел ел СО со

| Алексенко А.Г., Шагурин И.И | |||

| Микросхемотехника | |||

| М.: Радио и связь, 1982, с | |||

| Гудок | 1921 |

|

SU255A1 |

| IEEE J | |||

| of SoEid State Circuits | |||

| V, SC-18, 1983, № 4, p | |||

| Мяльная машина для лубовых растений | 1923 |

|

SU414A1 |

Авторы

Даты

1987-01-23—Публикация

1984-12-29—Подача