11

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах, работающих в реальном масштабе времени, для управления запуском программ имеющих между собой информационные связи.

Цель изобретения - сокращение затрат оборудования.

Сущность изобретения заключается в Том, что устройство для управления запуска программ фиксирует факт наличия входных данных - наличие информационной связи в виде условий запуска программ, заносит их в фактический набор условий запуска каждой программы, анализирует полноту ее . фактического набора путем сравнения с эталонным набором, выбирает наиболее приоритетную программу из программ с полньв4 набором входных данных и передает ее номер по межпроцессорному интерфейсу в ЭВМ.

В основу работы предлагаемого уст- ройства положен принцип составления плана реализации информационного связанного набора программ с учетом их приоритета. При этом приоритет каждой программы определяется величиной критического пути в графе, представ ляющем структуру набора программ по правилу, чем больше величина критического пути от вершины графа, соответствующей данной программе, до конечной вершины, тем вьш1е ее приоритет.

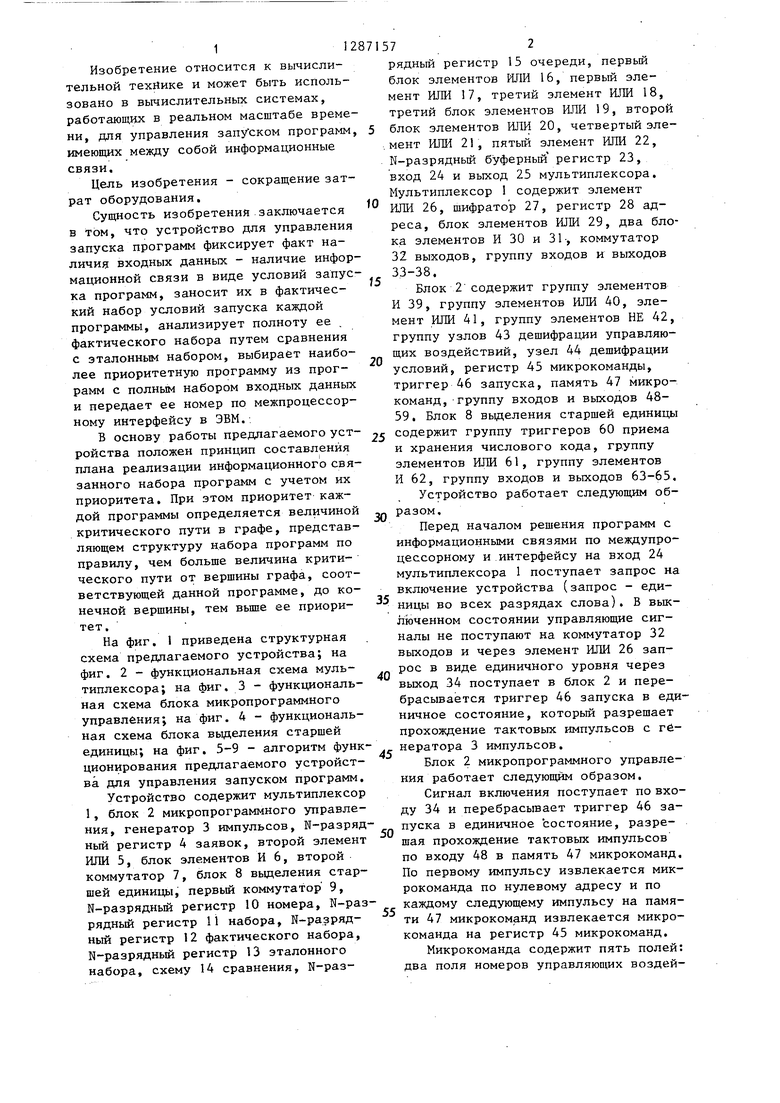

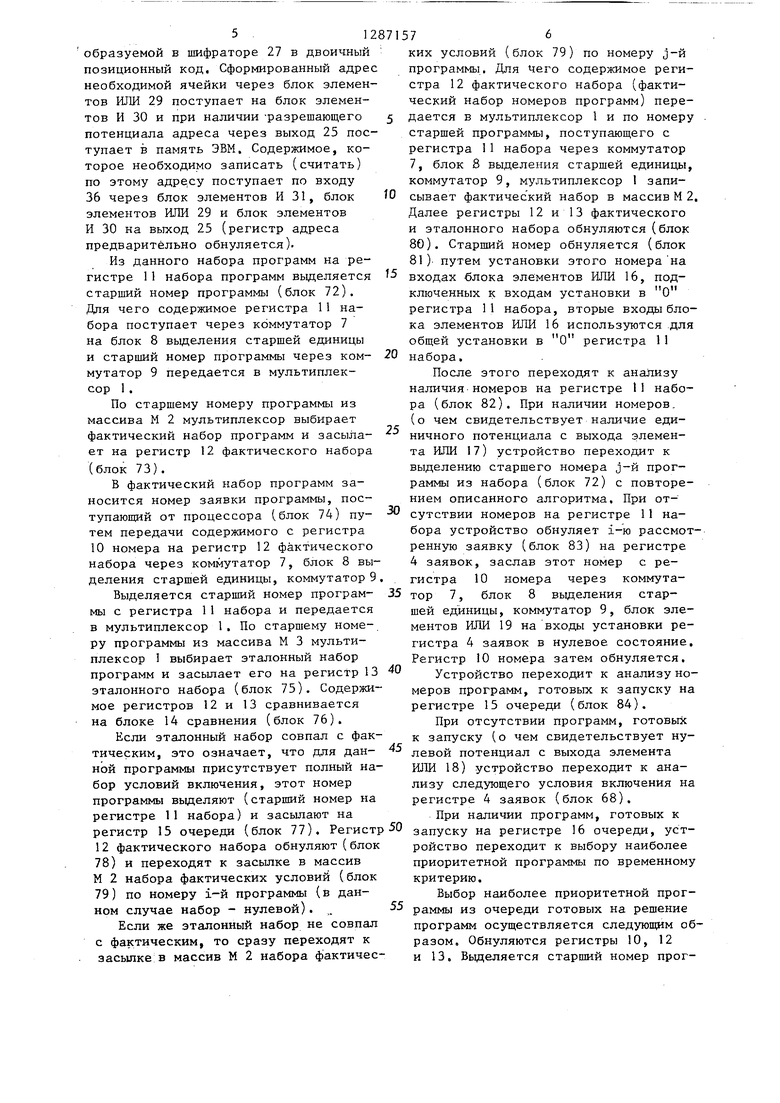

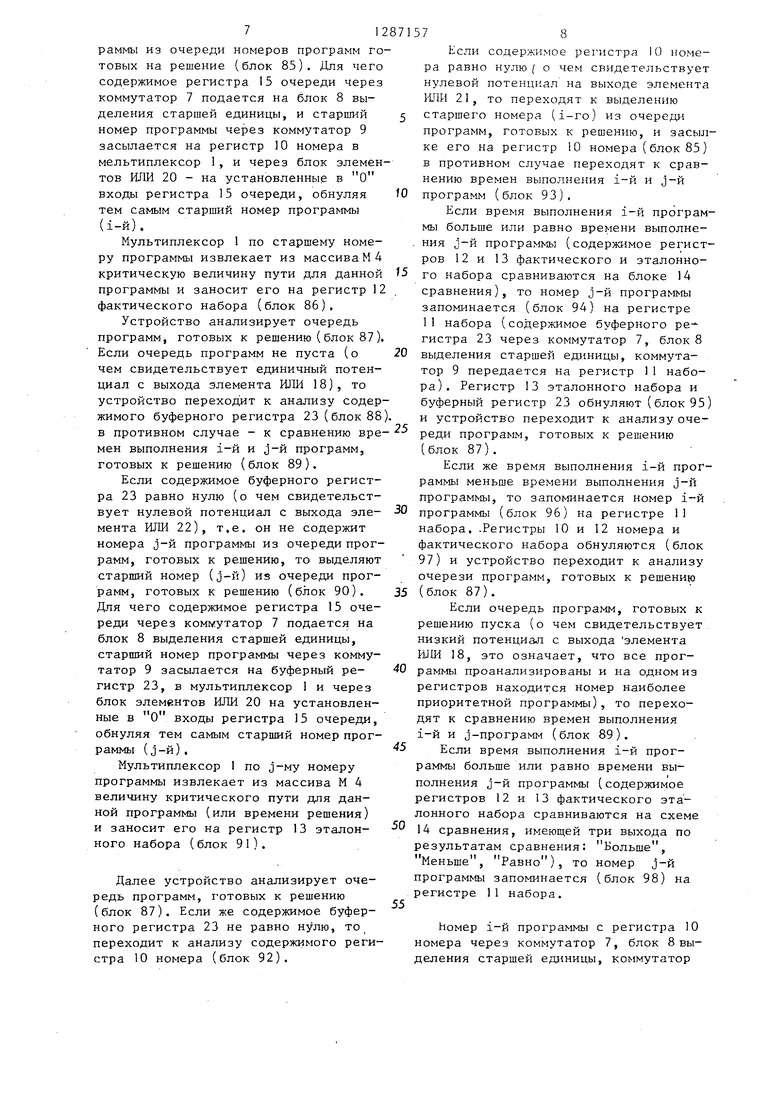

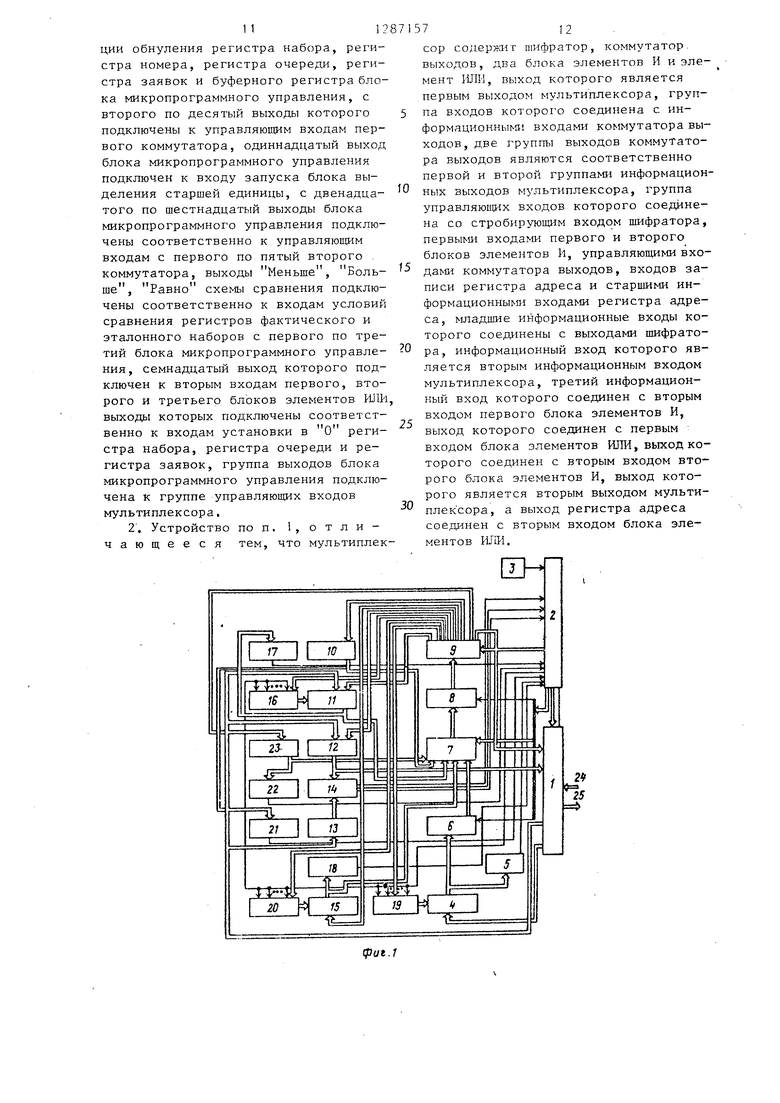

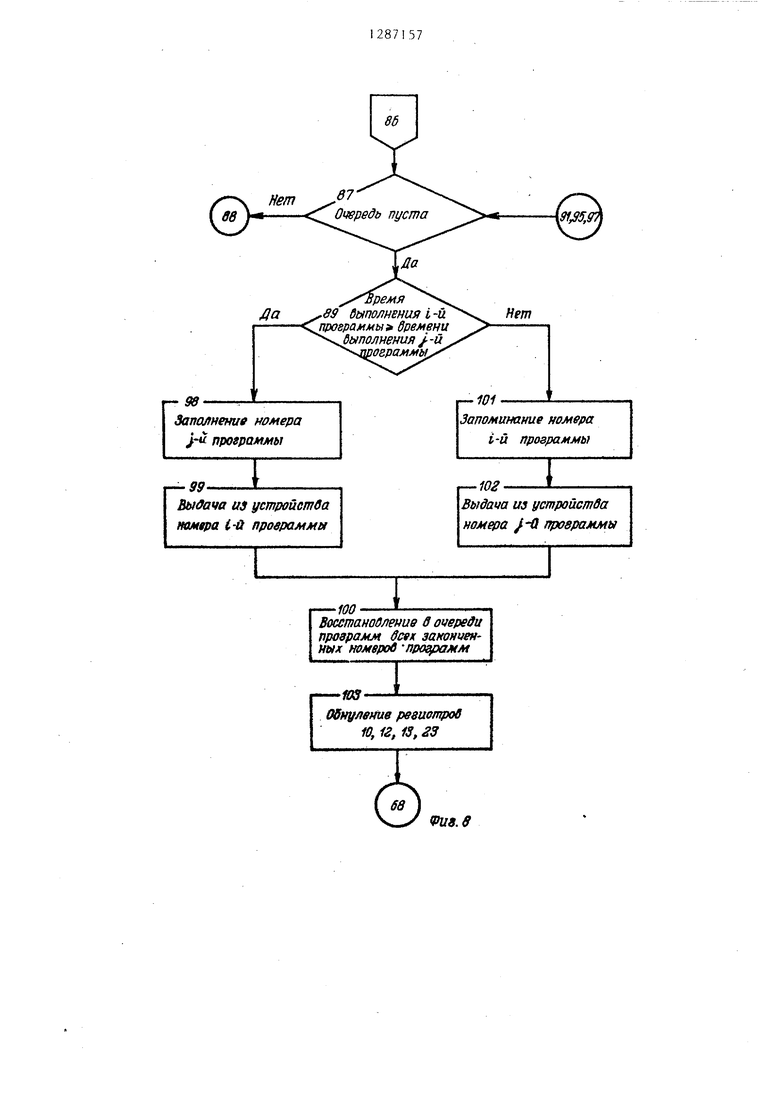

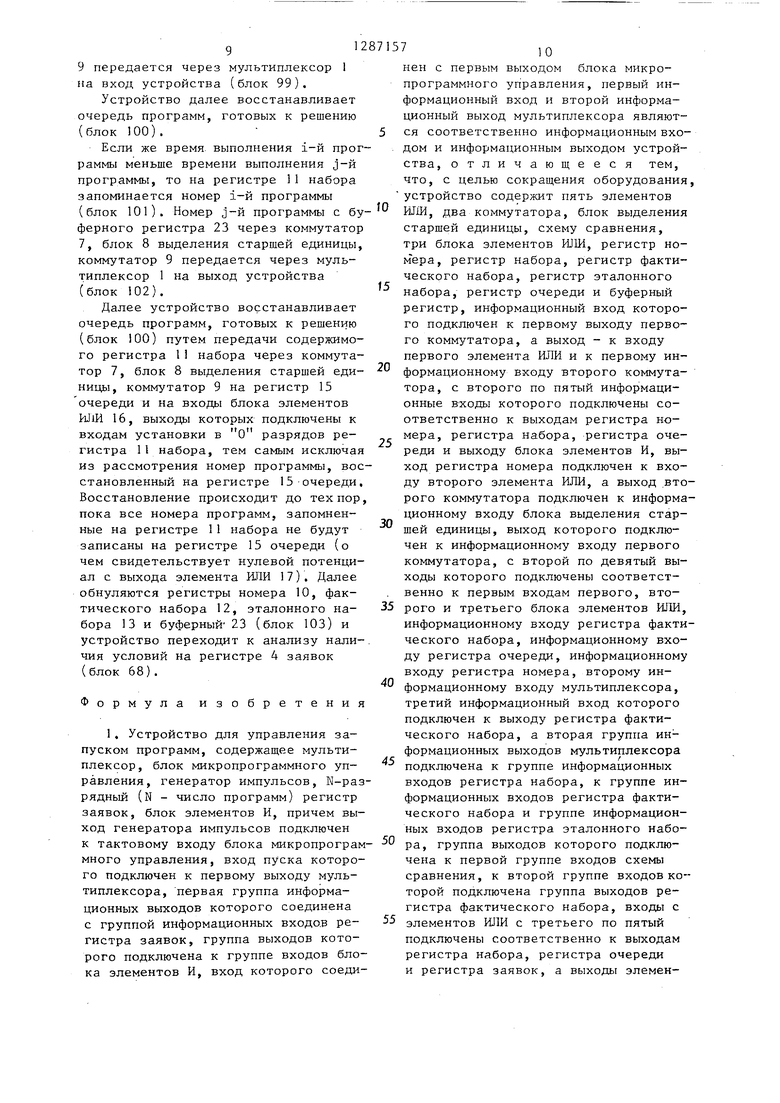

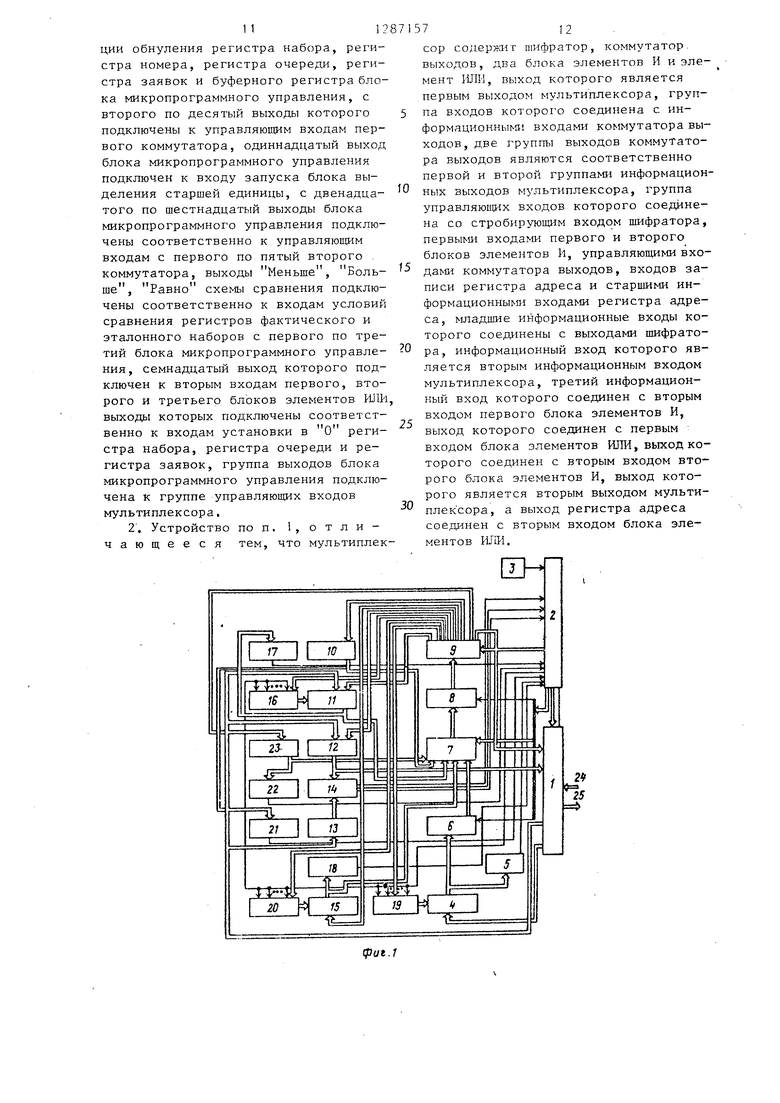

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - функциональная схема мультиплексора; на фиг. 3 - функциональная схема блока микропрограммного управления; на фиг. 4 - функциональная схема блока вьщеления старшей единицы; на фиг. 5-9 - алгоритм функционирования предлагаемого устройства для управления запуском программ. Устройство содержит мультиплексор 1, блок 2 микропрограммного управления, генератор 3 импульсов, N-разряд ный регистр 4 заявок, второй элемент ИЛИ 5, блок элементов И 6, второй коммутатор 7, блок 8 вьщеления старшей единицы, первый коммутатор 9, N-разрядньм регистр 10 номера, N-раз рядный регистр 1i набора, N-разряд- ный регистр 12 фактического набора, N-разрядный регистр 13 эталонного набора, схему 14 сравнения, N-раз

S

0

1

5

5

0

5

0

5

572

рядный регистр 15 очереди, первый блок элементов ИЛИ 16, первый элемент ИЛИ 7, третий элемент ИЛИ 18, третий блок элементов ШШ 19, второй блок элементов ИЛИ 20, четвертый эле- .мент ИЛИ 21, пятый элемент ИЛИ 22, N-разрядный буферный регистр 23, вход 24 и выход 25 мультиплексора. Мультиплексор 1 содержит элемент ИЛИ 26, шифратор 27, регистр 28 адреса, блок элементов ИЛИ 29, два блока элементов И 30 и 31-, коммутатор 32 выходов, группу входов и выходов 33-38.

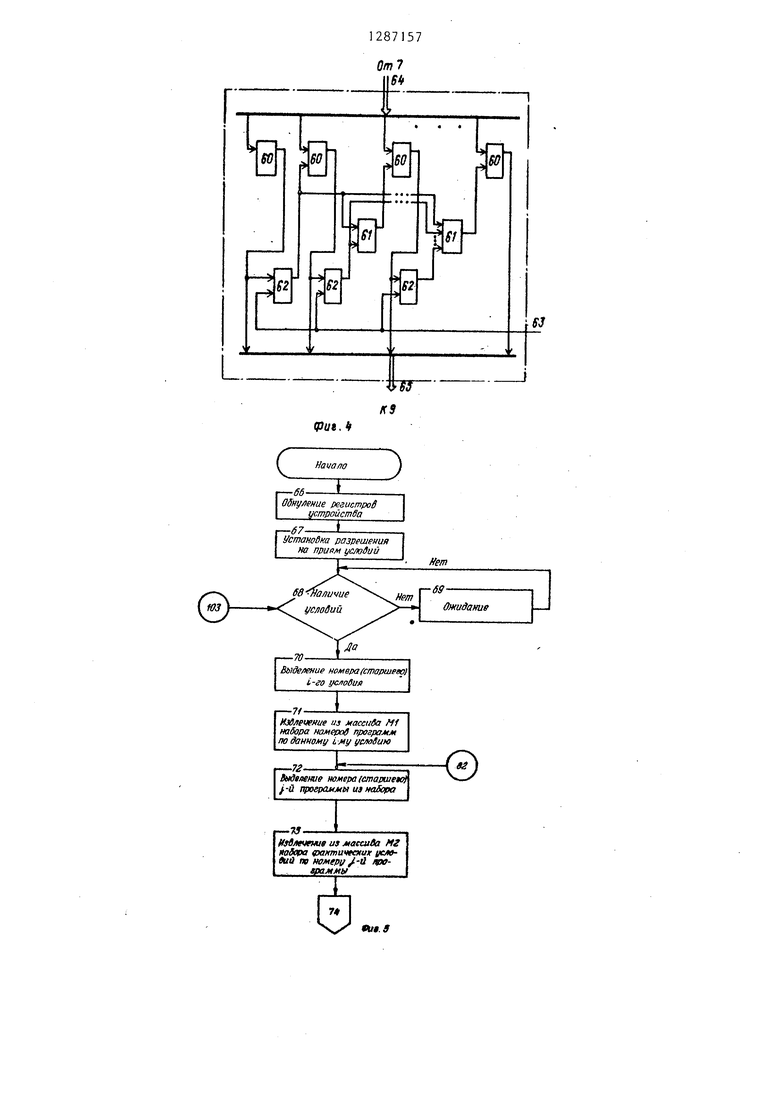

Блок 2 содержит группу элементов И 39, группу элементов ИЛИ 40, элемент ИЛИ 41, группу элементов НЕ 42, группу узлов 43 дешифрации управляющих воздействий, узел 44 дешифрации условий, регистр 45 микрокоманды, триггер 46 запуска, память 47 микрокоманд, группу входов и выходов 48- 59. Блок 8 выделения старшей единицы содержит группу триггеров 60 приема и хранения числового кода, группу элементов ИЛИ 61, группу элементов И 62, группу входов и выходов 63-65.

Устройство работает следующим образом.

Перед началом решения программ с информационными связями по междупроцессорному и интерфейсу на вход 24 мультиплексора 1 поступает запрос на включение устройства (запрос - единицы во всех разрядах слова). В выключенном состоянии управляющие сигналы не поступают на коммутатор 32 выходов и через элемент ИЛИ 26 запрос в виде единичного уровня через выход 34 поступает в блок 2 и перебрасывается триггер 46 запуска в единичное состояние, который разрешает прохождение тактовых импульсов с генератора 3 импульсов.

Блок 2 микропрограммного управления работает следующим образом.

Сигнал включения поступает по входу 34 и перебрасьшает триггер 46 запуска в единичное состояние, разрешая прохождение тактовых импульсов по входу 48 в память 47 микрокоманд. По первому импульсу извлекается микрокоманда по нулевому адресу и по каждому следующему импульсу на памяти 47 микрокоманд извлекается микрокоманда на регистр 45 микрокоманд.

Микрокоманда содержит пять полей: два поля номеров управляющих воздей

12

ствий, поле условий и два поля адресов перехода. Такая структура микрокоманды позволяет одновременно выдавать два управляющих воздействия и учитывать наличие поступающих уело- ВИЙ. Номера управляющих воздействий дешифрируются на узлах 43 дешифрации управляюш 1х воздействий и через группу элементов ИЛИ 40 поступают в устройство.

Номер условия дешифрируется на узле 44 дешифрации условий и при наличии или отсутствии соответствующего условия на одном из элементов И

39 группы на входе элемента появляется или не появляется высокий потенциал. При наличии условия в память 47 микрокоманд передается один адрес, а при отсутствии - другой адрес микрокоманды. Последней командой микропрограммы триггер 46 запуска перебрасывает в нулевое состояние, перекрывая прохождения тактовых импульсов в память 47 микрокоманд. .

Блок 2 по запросу на включение устройства обнуляет регистры и счетчики устройства (блок 66), устанавливает разрешение на прием запросов в регистр 4 заявок (блок 67) и пере- водит устройство в режим ожидания появления заявок ра регистре 4 заявок, о чем свидетельствует сигнал с выхода элемента ИЛИ 5 (блоки 68 и 69

Освободившийся от вычислительной работы процессор по межпроцессорному интерфейсу посылает запрос о готовности к реализации очередной программы набора. Этот запрос поступает через мультиплексор 1 на регистр 4 заявок. Элемент ИЛИ 5 обнаруживает наличие информации на регистре 4 заявок и сигнал с элемента ИЛИ 5 поступает в блок 2. Блок 2 организует дальнейшее функционирование устрой- ства. На регистре 4 заявок в позиционном коде фиксируются номера запросов - программ, которые выполнены. Для своей работы устройство использует четыре массива информации, хранящихся в оперативном запоминающем устройстве вычислительной системы.

Массив М 1 содержит таблицу информационных связей программ.

Массив М 2 содержит фактическое

наличие условий для запуска программ (номера выполненных программ). Б исходном состоянии массив М 2 - нулевой .

20

7

5 О

15

25

у.

. .

35

0

5

574

Массив М 3 содержит эталонное значение условий, необходимых для запуска программ (для каждой программы - номера программ, выполнение которых необходимо для запуска программы).

Массив М 4 содержит временные характеристики программ.

По сигналам блока 2 происходит выделение старшего номера запроса - номера программы (блок 70). Для чего информация с регистра 4 заявок через блок элементов И 6, коммутатор 7, поступает на блок 8 выделения старшей единицы. Далее старший номер запроса через коммутатор 9 поступает в регистр 10 номера. По старшему номеру запроса из массива М 1 извлекается набор номеров программ, для которых данная программа является условием включения (блок 71). Для чего с регистра 10 номера старший номер программы поступает через коммутатор 7 на блок 8 выделения старшей единицы.

Блок 8 выделения старшей единицы работает следующим .образом. По входам 64 блока 7 коммутации поступает двоичный код на группу триггеров 60 приема и хранения числового кода. По управляющему входу 63 от блока 2 поступает управляющий сигнал на вторые входы элементов И 62 группы.

При наличии на выходе триггера 60 группы высокого потенциала (единичный уровень) на вьпсоде соответствующего элемента И 62 группы появляется единичный уровень, которым все последующие триггера сбрасываются в нулевое состояние через элементы ИЛИ 61 группы. Таким образом, остается в единичном состоянии крайний триггер. С блока 8 выделения старшей единицы номер программ поступает на коммутатор 9 и в мультиплексор 1. Мультиплексор 1 по старшему номеру программы извлекает из массива М I набор программ и заносит его на регистр II набора.

Для передачи (извлечения) информации по нужному адресу по управляющим входам 33 в мультиплексор 1 поступает набор управляющих воздействий, характеризующих номер выбранного массива (например, 10 - второй массив). Эти воздействия являются старшими разрядами адреса, поступающими на регистр 28 адреса. Младшие разряды поставляют адрес, поступающий по входу 35 в мультиплексор 1, предварительно пре512

образуемой в шифраторе 27 в двоичный позиционный код. Сформированный адрес необходимой ячейки через блок элементов ИЛИ 29 поступает на блок элементов И 30 и при наличии -разрешающего потенциала адреса через выход 25 поступает в память ЭВМ. Содержимое, которое необходимо записать (считать) по этому адре;су поступает по входу 36 через блок элементов И 31, блок элементов ИЛИ 29 и блок элементов И 30 на выход 25 (регистр адреса предварительно обнуляется).

Из данного набора программ на регистре 11 набора программ выделяется старший номер программы (блок 72). Для чего содержимое регистра 11 набора поступает через коммутатор 7 на блок 8 выделения старшей единицы и старший номер программы через ком- мутатор 9 передается в мультиплексор 1 .

По старшему номеру программы из массива М 2 мультиплексор выбирает фактический набор программ и засыла- ет на регистр 12 фактического набора

(блок 73).

В фактический набор программ заносится номер заявки программы, пос- тупагош 1й от процессора (блок 74) пу- тем передачи содержимого с регистра 10 номера на регистр 12 фактического набора через коммутатор 7, блок 8 выделения старшей единицы, коммутатор 9

Выделяется старший номер програм- мы с регистра 11 набора и передается в мультиплексор 1 . По старп ему номе- ру программы из массива М 3 мультиплексор I выбирает эталонный набор программ и засылает его на регистр 13 эталонного набора (блок 75). Содержимое регистров 12 и 13 сравнивается на блоке 14 сравнения (блок 76).

Если эталонный набор совпал с фактическим, это означает, что для дан- ной программы присутствует полный набор условий включения, этот номер программы выделяют (старший номер на регистре 11 набора) и засылают на регистр 15 очереди (блок 77). Регист 12 фактического набора обнуляют (блок

78)и переходят к засылке в массив

М 2 набора фактических условий (блок

79)по номеру i-й программы (в данном случае набор - нулевой). .

Если же эталонный набор не совпал с фактическим, то сразу переходят к засыпке в массив М 2 набора фактичес76

ких условий (блок 79) по номеру j-й программы. Для Чего содержимое регистра 12 фактического набора (фактический набор номеров программ) передается в мультиплексор 1 и по номеру старшей программы, поступаюш;его с регистра 11 набора через коммутатор 7, блок 8 выделения старшей единицы, коммутатор 9, мультиплексор 1 записывает фактический набор в массив М 2. алее регистры 12 и 13 фактического и эталонного набора обнуляются (блок 80). Старший номер обнуляется (блок 81) путем установки этого номера на входах блока элементов ИЛИ 16, подключенных к входам установки в О регистра П набора, вторые входы блока элементов ИЛИ 16 используются для общей установки в О регистра 11 набора.

После этого переходят к анализу наличия номеров на регистре 11 набора (блок 82). При наличии номеров, (о чем свидетельствует наличие единичного потенциала с выхода элемента ИЛИ 17) устройство переходит к выделению старшего номера j-й программы из набора (блок 72) с повторением описанного алгоритма. При отсутствии номеров на регистре 11 набора устройство обнуляет i-ю рассмотренную заявку (блок 83) на регистре 4 заявок, заслав этот номер с регистра 10 номера через коммутатор 7, блок 8 вьщеления старшей единицы, коммутатор 9, блок элементов ИЛИ 19 на входы установки регистра 4 заявок в нулевое состояние. Регистр 10 номера затем обнуляется.

Устройство переходит к анализу номеров программ, готовых к запуску на регистре 15 очереди (блок 84).

При отсутствии программ, готовых к запуску (о чем свидетельствует нулевой потенциал с выхода элемента ИЛИ 18) устройство переходит к анализу следующего условия включения на регистре 4 заявок (блок 68).

При наличии программ, готовых к запуску на регистре 16 очереди, устройство переходит к выбору наиболее приоритетной программы по временному критерию.

Выбор наиболее приоритетной программы из очереди готовых на решение программ осуществляется следующим образом. Обнуляются регистры 10, 12 и 13, Вьщеляется старший номер прог712

раммы из очереди номеров программ готовых на решение (блок 85). Для чего содержимое регистра 15 очереди через коммутатор 7 подается на блок 8 выделения старшей единицы, и старший номер программы через коммутатор 9 засылается на регистр 10 номера в мельтиплексор 1, и через блок элементов ИЛИ 20 - на установленные в О входы регистра 15 очереди, обнуляя тем самым старший номер программы (i-й).

Мультиплексор 1 по старшему номеру программы извлекает из массивам 4 критическую величину пути для данной программы и заносит его на регистр 12 фактического набора (блок 86),

Устройство анализирует очередь программ, готовых к решению (блок 87). Если очередь программ не пуста (о чем свидетельствует единичный потенциал с выхода Элемента ИЛИ 18, то устройство переходит к анализу содержимого буферного регистра 23 (блок 88 в противном случае - к сравнению вре- мен выполнения i-й и j-й программ, готовых к решению (блок 89).

Если содержимое буферного регистра 23 равно нулю (о чем свидетельствует нулевой потенциал с выхода эле- мента ИЛИ 22), т.е. он не содержит номера j-й программы из очереди программ, готовых к решению, то выделяют старший номер (j-й) из очереди программ, готовых к решению (блок 90). Для чего содержимое регистра 15 очереди через коммутатор 7 подается на блок 8 выделения старшей единицы, старший номер программы через коммутатор 9 засылается на буферный ре- гистр 23, в мультиплексор 1 и через блок элементов ИЛИ 20 на установленные в О входы регистра 15 очереди, обнуляя тем самым старший номер программы (j-й).

Мультиплексор 1 по j-му номеру программы извлекает из массива М 4 величину критического пути для данной программы (или времени решения) и заносит его на регистр 13 эталон- ного набора (блок 91).

Далее устройство анализирует очередь программ, готовых к решению (блок 87). Если же содержимое буферного регистра 23 не равно нулю, то переходит к анализу содержимого регистра 10 номера (блок 92).

578

Если содержимое регистра 10 номера равно нулю ( о чем свидетельствует нулевой потенциал на выходе элемента Ш1И 21, то переходят к выделению старшего номера (i-ro) vis очереди программ, готовых к решению, и засылке его на регистр 10 номера (блок 85) в противном случае переходят к сравнению времен выполнения i-й и j-й программ (блок 93).

Если время выполнения i-й программы больше или равно времени выполне- . ния j-й программы (содержимое регистров 12 и 13 фактического и эталонного набора сравниваются на блоке 14 сравнения), то номер j-й программы запоминается (блок 94) на регистре 11 набора (содержимое буферного ре- гистра 23 через коммутатор 7, блок 8 выделения старшей единицы, коммутатор 9 передается на регистр 11 набора). Регистр 13 эталонного набора и буферный регистр 23 обнуляют (блок 95 и устройство переходит к анализу очереди программ, готовых к решению (блок 87).

Если же время выполнения i-й программы меньше времени выполнения j-й программы, то запоминается номер i-й программы (блок 96) на регистре 11 набора. -Регистры 10 и 12 номера и фактического набора обнуляются (блок 97) и устройство переходит к анализу очерези программ, готовых к решению (блок 87).

Если очередь программ, готовых к решению пуска (о чем свидетельствует низкий потенциал с выхода элемента ШШ 18, это означает, что все программы проанализированы и на одном из регистров находится номер наиболее приоритетной программы), то переходят к сравнению времен выполнения i-й и j-программ (блок 89).

Если время выполнения i-й программы больше или равно времени выполнения j-й программы (содержимое регистров 12 и 13 фактического эталонного набора сравниваются на схеме 14 сравнения, имеющей три выхода по результатам сравнения: Больше, Меньше, Равно), то номер j-й программы запоминается (блок 98) на регистре 11 набора.

Номер i-й программы с регистра Ю номера через коммутатор 7, блок 8 выделения старшей единицы, коммутатор

912

9 передается через мультиплексор 1 на вход устройства (блок 99).

Устройство далее восстанавливает очередь программ, готовых к решению (блок 100),

Если же время, выполнения i-й программы меньше времени выполнения j-й программы, то на регистре I1 набора запоминается номер i-и программы (блок 101). Номер j-й программы с буферного регистра 23 через коммутатор 7, блок 8 выделения старшей единицы, коммутатор 9 передается через мультиплексор 1 на выход устройства (блок 102).

Далее устройство восстанавливает очередь программ, готовых к решению (блок 100) путем передачи содержимого регистра 1 набора через коммутатор 7, блок В выделения старшей единицы, коммутатор 9 на регистр 15 очереди и на входы блока элементов ЫШ 16, выходы которых подключены к входам установки в О разрядов регистра 11 набора, тем самым исключая из рассмотрения номер программы, восстановленный на регистре 15-очереди. Восстановление происходит до тех пор, пока все номера программ, запомненные на регистре 11 набора не будут записаны на регистре 15 очереди (о чем свидетельствует нулевой потенциал с выхода элемента ИЛИ 17). Далее обнуляются регистры номера 10, фактического набора 12, эталонного набора 13 и буферный 23 (блок 103) и устройство переходит к анализу наличия условий на регистре 4 заявок (блок 68).

Формула изобретения

1. Устройство для управления запуском программ, содержащее мультиплексор, блок микропрограммного управления, генератор импульсов, N-раз- рядный (N - число программ) регистр заявок, блок элементов И, причем выход генератора импульсов подключен к тактовому входу блока микропрограммного управления, вход пуска которого подключен к первому выходу мультиплексора, первая группа информационных выходов которого соединена с группой информационных входо.в регистра заявок, группа выходов которого подключена к группе входов блока элементов И, вход которого соеди10

нен с первым выходом блока микропрограммного управления, первый информационный вход и второй информационный выход мультиплексора являются соответственно информационным входом и информационным выходом устройства, отличаюш;ееся тем, что, с целью сокращения оборудования.

5

0

5

0

5

0

5

0

5

устройство содержит пять элементов ШШ, два коммутатора, блок выделения старшей единицы, схему сравнения, три блока элементов ИЛИ, регистр номера, регистр набора, регистр фактического набора, регистр эталонного набора, регистр очереди и буферный регистр, информационный вход которого подключен к первому выходу первого коммутатора, а выход - к входу первого элемента ИЛИ и к первому информационному входу второго коммутатора, с второго по пятый информационные входы которого подключены соответственно к выходам регистра номера, регистра набора, регистра очереди и выходу блока элементов И, выход регистра номера подключен к входу второго элемента ИЛИ, а выход .второго коммутатора подключен к информационному входу блока выделения старшей единицы, выход которого подключен к информационному входу первого коммутатора, с второй по девятый выходы которого подключены соответственно к первым входам первого, второго и третьего блока элементов ИЛИ, информационному входу регистра фактического набора, информационному входу регистра очереди, информационному входу регистра номера, второму информационному входу мультиплексора, третий информационный вход которого подключен к выходу регистра фактического набора, а вторая группа информационных выходов мультиплексора подключена к группе информационных входов регистра набора, к группе информационных входов регистра фактического набора и группе информационных входов регистра эталонного набора, группа выходов которого подключена к первой группе входов схемы сравнения, к второй группе входов которой подключена группа выходов регистра фактического набора, входы с элементов ИЛИ с третьего по пятый подключены соответственно к выходам регистра набора, регистра очереди и регистра заявок, а выходы элемен

1112

ции обнуления регистра набора, регистра номера, регистра очереди, регистра заявок и буферного регистра блока микропрограммного управления, с второго по десятый выходы которого подключены к управляющим входам первого коммутатора, одиннадцатый выход блока микропрограммного управления подключен к входу запуска блока выделения старшей единицы, с двенадцатого по шестнадцатый выходы блока микропрограммного управления подключены соответственно к управляюш1 м входам с первого по пятый второго . коммутатора, выходы Меньше, Боль- ше, Равно схемы сравнения подключены соответственно к входам условий сравнения регистров фактического и эталонного наборов с первого по третий блока микропрограммного управле- ния, семнадцатый выход которого подключен к вторым входам первого, второго и третьего блоков элементов Ш1И выходы которых подключены соответственно к входам установки в О регистра Набора, регистра очереди и регистра заявок, группа выходов блока микропрограммного управления подключена к группе yпpaвляюшJ x входов мультиплексора.

2. Устройство по п. 1, о т л и - чаюш,ееся тем, что мультиплек

5712 .

сор содержит шифратор, коммутатор, выходов, два блока элементов Н и элемент 1ШН, выход которого является первым выходом мультиплексора, группа входов KOTopoi o соединена с информационными входами коммутатора выходов, две группы выходов коммутатора выходов являются соответственно первой и второй группами информационных выходов мультиплексора, группа yпpaвляюш ix входов которого соединена со стробирующим входом шифратора, первыми входа ш первого и второго блоков элементов И, управляюш 1ми входами коммутатора выходов, входов записи регистра адреса и старшими ин- фopмaциoнHы пI входами регистра адреса, младшие информационные входы которого соединены с выходами шифратора, информационный вход которого является вторым информационным входом мультиплексора, третий информационный вход которого соединен с вторым входом первого блока элементов И, выход которого соединен с первым входом блока элементов ИЛИ, выход которого соединен с вторым входом второго блока элементов И, выход которого является вторым выходом мульти- плек сора, а выход регистра адреса соединен с вторым входом блока элементов ШМ.

KSJ,S К

Omf

фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для отладки программ | 1983 |

|

SU1322290A2 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Микропрограммный диспетчер многопроцессорной вычислительной системы | 1987 |

|

SU1532926A1 |

| Устройство для организации мультиветвления процессов в электронной вычислительной машине | 1980 |

|

SU922743A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

Изобретение относится к области вычислительной техники и может быть использовано для управления запуском программ, имеющих между собой информационные связи. Цель изобретения - сокращение оборудования. Устройство содержит мультиплексор, блок микропрограммного уйравления, генератор импульсов, регистр заявок, блок элементов И, пять элементов ИЛИ, два коммутатора, блок выделения старшей единицы, схему сравнения, три блока элементов ИЛИ, регистры номера, набора, фактического набора, эталонного набора, очереди и буферный регистр. Устройство анализирует номера заявок на регистре заявок, поступающих через мультиплексор. Номера заявок через блок элементов И и второй коммутатор поступают на блок выделения старшей единицы. По старшему номеру через первый коммутатор и мультиплексор из памяти системы извлекается на регистр набора набор программ, информационно связанных с заявкой. Для каждой программы из этого набора из памяти системы на регистры фактического и эталонного наборов соответственно извлекаются эталонное и фактическое значения условий включения этой программы. Порядок рассмотрения определяется блоком выделения старшей единицы. При совпадении этих условий на схеме сравнения программа ставится в очередь на регистр очереди. Определение наиболее приоритет- . ной программы из очереди осуществляется путем сравнения для всех программ времени их выполнения на схеме сравнения. Порядок сравнения определяется блоком выделения старшей единицы. Обработанные заявки исключаются из рассмотрения путем обнуления соответствующих разрядов регистров набора, очереди, заявок через блоки элементов ИЛИ. Первый - пятый элементы ИЛИ фиксируют факты обнуления регистров номера, буферного, набора, очереди, заявок. Устройство функционирует под управлением микропрограммного блока управления. 1 з.п. ф-лы, 9 ил. с SS (Л с: 1чЭ 00 ч Nei СЛ

с

ffft

Начало

Обнуление ре гистрой ycmpoucmffa

-67±.

Iо

I Установка разрешения 1 на при ям ус/юбиО

I Выде/ ение номера (старшею i-eo условие

Нет

I me/If чеяив из массива Mf I набора намазов программ I т данному 1му усмвию

-72Г

Иыдляение номера (старшек / -и программы из навара

ТУ.

I-

fMjitvmuf и массива Мг мдсра узантичееках ifCM- виа I номеру/-tl t . имму

7

х

9и.Я

Y

-

Занесение номера i-ao б набор vecHUx {условий программы

I

г-75

Извме ение из массива ИЗ, набора зталоинь х дсловий т номеру J.-U прозраммы

7/9 jma лонный -s,, Нет набор услобий совпа дает с факгличесцим набором

Занесение номера j- -и программы в очередь программ, aomoBbiJf к решению

i

Обнуление набора д)акти- чесних условий -й программы

3

19 - Засылка в массив М2 набора (рантпических условий по номеру J.-U программы

Y

ма антп о но грам

во

/

PU8.6

80V

05нулв ие набора сраюличес- ких уалобий J--U программы и эталонного набора

Обнуление номера /-и программы

V

Обнуление L 8o условия

л Очередь программ, гото Вых к решению.

выделение 1-ео номера (старшего) программы из о ервди программf готобых и решению и засылка на регистр номера 10

Ыз&аечеиив из массива М4 бремени выполнения i-u программы и засылка на цвгистр pa)fmwecf oeo набора 12

87 XX 8. 7

В(п}анобленив в ovepeSu проарамм дС9к закоячен- ных иомвроб -программ

Обнуление рвзиоглроб Ю, 12, 13,23

Риз. в

I Запоминание ffOMfpa I -u программы

Fi VMUHuHus тмера i-u тюграммы

mm

Выделение /-го номера (cfnaputesi/ из софеЗа лкерамм, аопюбых к решению, и засылка т 5уд№ртЛ рееиалр 25

91Шйвчеюу из маесадвМО Окмена быгкиатшя f-u програмлы и яамхв на резистр зталоююво набора 13

Г-95

Обну/

Однцл&ше Ps23, Ре 13

OffnyA

OffnyMHue Pa Ю, As 12

. 8

Редактор Ю. Середа

Составитель М. Сорочан Техред Л.Олейник

Заказ 7718/52 Тираж 694Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор М, Пожо

| Устройство для обслуживания запросов | 1978 |

|

SU807292A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля информации по модулю два | 1979 |

|

SU877546A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-30—Публикация

1985-09-05—Подача