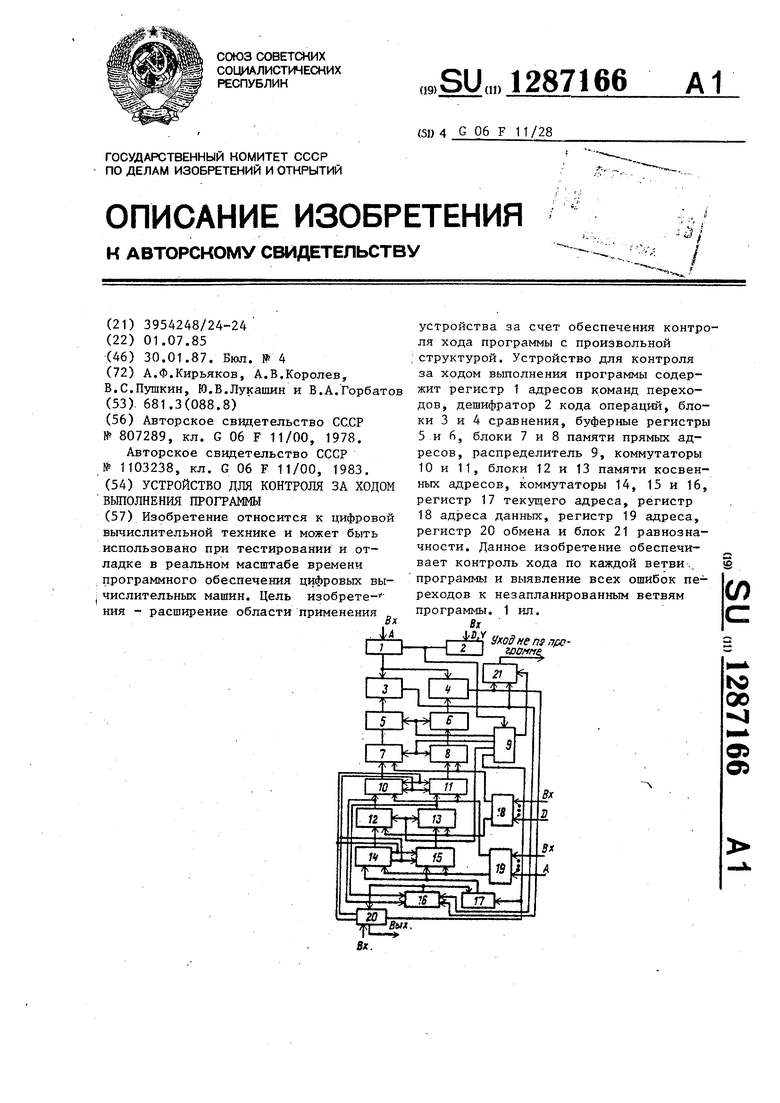

Изобретение относится к цифровой вычислительной технике и может быть использовано при тестировании и отладке в реальном масштабе времени программного обеспечения цифровых вы- числительных машин.

Цель изобретения - расширение области применения устройства за счет обеспечения контроля хода выполнения программы с произвольной структурой.

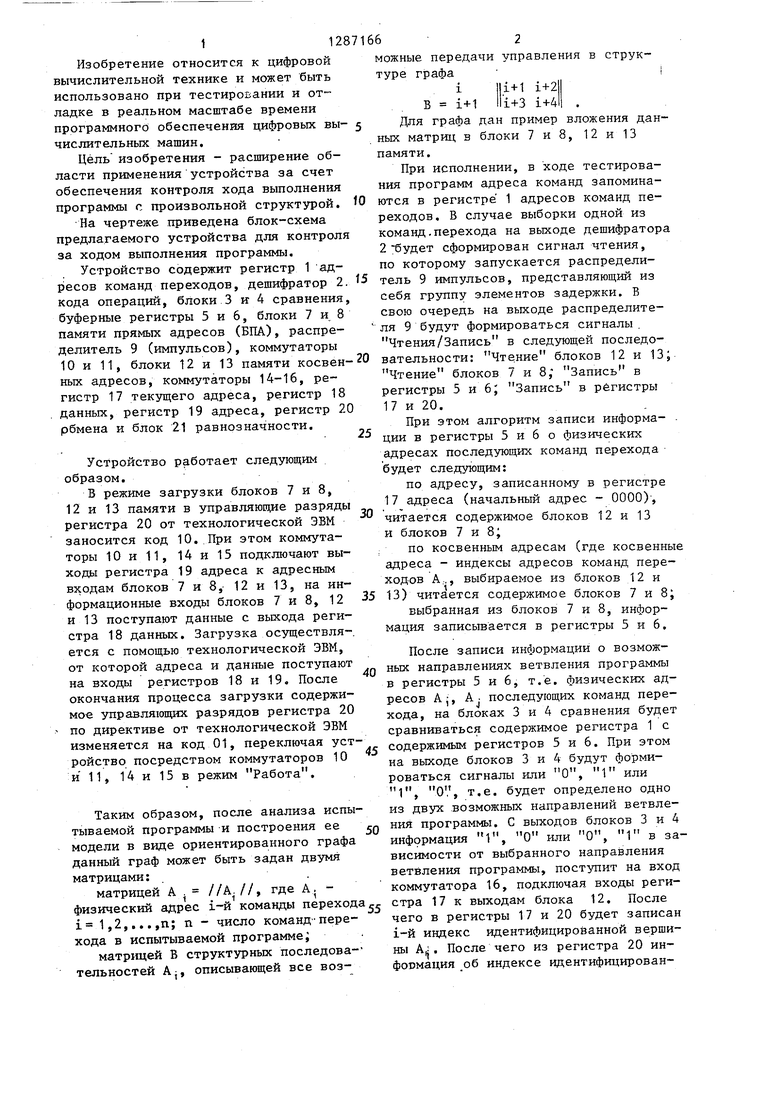

На чертеже приведена блок-схема предлагаемого устройства для контроля за ходом выполнения программы.

Устройство содержит регистр 1 адресов команд переходов, дешифратор 2. кода операций, блоки 3 и 4 сравнения, буферные регистры 5 и 6, блоки 7 и 8 памяти прямых адресов (БПА), распределитель 9 (импульсов), коммутаторы 10 и 11, блоки 12 и 13 памяти косвенных адресов, коммутаторы 14-16, регистр 17 текущего адреса, регистр 18 данных, регистр 19 адреса, регистр 20 рбмена и блок 21 равнозначности.

Устройство работает следующим образом.

В режиме загрузки блоков 7 и 8, 12 и 13 памяти в управляющие разряды регистра 20 от технологической ЭВМ заносится код 10. При этом коммутаторы 10 и 11, 14 и 15 подключают выходы регистра 19 адреса к адресным входам блоков 7 и 8, 12 и 13, на информационные входы блоков 7 и 8, 12 и 13 поступают данные с выхода регистра 18 данных. Загрузка осуществляется с помощью технологической ЭВМ, от которой адреса и данные поступают на входы регистров 18 и 19. После окончания процесса загрузки содержимое управляющих разрядов регистра 20 по директиве от технологической ЭВМ изменяется на код 01, переключая устройство посредством коммутаторов 10 и 11, 14 и 15 в режим Работа.

Таким образом, после анализа испытываемой программы и построения ее Q модели в виде ориентированного графа данный граф может быть задан двумя матрицами:

матрицей А . , где А. После записи информации о возможных направлениях ветвления программы в регистры 5 и 6, т.е. физических ад ресов AJ, А- последующих команд пере хода, на блоках 3 и 4 сравнения буде сравниваться содержимое регистра 1 с содержимым регистров 5 и 6. При этом на выходе блоков 3 и 4 будут формироваться сигналы или О, 1 или 1, О ,, т.е. будет определено одно из двух возможных направлений ветвле ний программы. С выходов блоков 3 и информация 1, О или О, 1 в з висимости от выбранного направления ветвления программы, поступит на вхо коммутатора 16, подключая входы реги

физический адрес i-й команды перехода„ стра 17 к выходам блока 12. После

i 1,2,...,п; п - число команд-перехода в испытываемой программе;

матрицей В структурных последова- тельностей А , описывающей все возчего в регистры 17 и 20 будет записа i-й индекс идентифицированной верши ны А,:. После чего из регистра 20 информация об индексе идентифицирован

5 0

можные передачи туре графа

i i+1

управления в струк0

В

jji+1 i+2 ll i+3 i+4ll .

Для графа дан пример вложения данных матриц в блоки 7 и 8, 12 и 13 памяти.

При исполнении, в ходе тестирования программ адреса команд запоминаются в регистре 1 адресов команд переходов. В случае выборки одной из команд,перехода на выходе дешифратора 2 будет сформирован сигнал чтения, по которому запускается распределитель 9 импульсов, представляющий из себя группу элементов задержки. В свою очередь на выходе распределителя 9 будут формироваться сигналы . Чтения/Запись в следзтощей последовательности: Чтение блоков 12 и 13; Чтение блоков 7 и 8, Запись в регистры 5 и 6; Запись в регистры 17 и 20.

При этом алгоритм записи информа- - ции в регистры 5 и 6 о физических адресах последующих команд перехода будет следующим:

по адресу, записанному в регистре 17 адреса (начальный адрес - 0000), читается содержимое блоков 12 и 13 и блоков 7 и 8;

по косвенным адресам (где косвенные адреса - индексы адресов команд переходов А..., выбираемое из блоков 12 и 5 13) читается содержимое блоков 7 и 8;

выбранная из блоков 7 и 8, информация записывается в регистры 5 и 6.

После записи информации о возможных направлениях ветвления программы в регистры 5 и 6, т.е. физических адресов AJ, А- последующих команд перехода, на блоках 3 и 4 сравнения будет сравниваться содержимое регистра 1 с содержимым регистров 5 и 6. При этом на выходе блоков 3 и 4 будут формироваться сигналы или О, 1 или 1, О ,, т.е. будет определено одно из двух возможных направлений ветвлений программы. С выходов блоков 3 и 4 информация 1, О или О, 1 в зависимости от выбранного направления ветвления программы, поступит на вход коммутатора 16, подключая входы регистра 17 к выходам блока 12. После

чего в регистры 17 и 20 будет записан i-й индекс идентифицированной вершины А,:. После чего из регистра 20 информация об индексе идентифицированной вершины будет переписана в память технологической ЭВМ.

Таким образом, каждый раз после записи в регистр 1 адреса текущей команды перехода и определения напра- вления ветвления программы в память технологической ЭВМ будет записан индекс очередной вершины графа. В результате в ходе выполнения программы в памяти технологической ЭВМ будет записана последовательность индексов вершин графа, соответствзтощая входным значениям, поданным на управляющую ЭВМ.

Таким образом, основным состояни- ем, фиксирующим уход программы по той или иной ветви, являются состояния выходов блоков 3 и 4 сравнения О, 1 или 1, О. Очевидно, что при уходе программы в непредсказуемую разработчиком область вычислений на выходах блоков 3 и 4 сравнения будет состояние нёсравнения О, О.

Б случае, если пер еход будет произведен в область, которая не запла- нирована, то ни на одном из блоков 3 и 4 не будет единичного сигнала. Блок 21 равнозначности при появлении нулевых сигналов на его входах вырабатывает единичный сигнал, которьш по- ступит на выход устройства и укажет на неверный ход программ.

Формула изобретения

Устройство для контроля за ходом выполнения программы, содержащее регистр адресов команд переходов, дешифратор кода операций, первый и второй блоки сравнения, первый и второй.буферные регистры, первый и второй блоки памяти .прямьпс адресов, распределитель импульсов, причем входы адресов команд переходов и кодов операций устройства соединены соот- ветственно с информационными входами регистра адресов команд переходов и I дешифратора кода операций, выход которого соединен с входом записи регистра команд переходов и входом за- пуска распределителя импульсов, информационный выход регистра адресов команд переходов соединен с первыми входами первого и второго блоков сравнения, информационные выходы первого и второго блоков памяти прямых адресов соединены с информационнь1Мй входами соответственно первого и второго буферных регистров, первый и

5

5 0

0

5

О 5 0

второй выходы распределителя импульсов соединены соответственно с входом записи первого и второго буферных регистров и входом чтения первого и второго блоков памяти прямых адресов, отличающееся тем, что, с целью расширения области применения за счет обеспечения контроля хода выполнения программы с произвольной структурой, в устройство введены пять коммутаторов, первый и второй блоки памяти косвенных адресов, регистр адреса и регистр данных, регистр обмена, регистр текущего адреса и блок равнозначности, причем информационный вход и вход адресов модели хода программы соединены с информационными

входами соответственно регистра данных и регистра адреса, первый выход которого соединен с первыми информационными входами первого и второго, коммутаторов, второй выход регистра адреса соединен с первыми информационными входами третьего и четвертого коммутаторов, выходы которых соединены с адресными входами соответственно первого и второго блоков памяти косвенных адресов, первый информационный выход регистра данных соединен с информационными входами первого и второго блоков памяти прямых адресов, второй информационный выход регистра данных соединен с информационными входами первого и второго блоков памяти косвенных адресов, третий выход распределителя импульсов соединен с входами чтения первого и второго блоков памяти косвенных адресов, информационньй выход первого блока памяти косвенных адресов соединен с вторым информационным входом первого коммутатора и с пер-. |вым информационным входом пятого коммутатора, информацис5нный выход второго блока памяти косвенных адресов соединен с вторым информационным входом второго коммутатора и вторым информационным входом пятого коммутатора, выход которого соединен с информационными входами регистра текущего адреса и регистра обмена, четвертый, выход распределителя импульсов соединен с входом записи регистра обмена и регистра текущего адреса, выход которого соединен с вторыми информационными входами третьего и четвертого коммутаторов, первый н второй выходы

,регистра обмена соединены соответственно с первыми и вторыми входами

51287166-6

первого, второго, третьего и четвер-коммутатора, выход равенства второго

того коммутаторов, вход установки ре-блока сравнения- соединен с вторым

жима устройства соединен с информаци-входом блока равнозначности и вторым

онным входом регистра обмена, третийуправляющим входом пятого коммутатовыход которого является информацион- 5Р пятый выход распределителя им-;

ным выходом устройства, выход равен-пульсов соединен с третьим входом

ства пе рвого блока сравнения соединенблока равнозначности, выход которого

с первым входом блока равнозначностиявляется выходом ошибки хода вычислии первым управляющим входом пятоготельного процесса устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Устройство для отладки программ | 1983 |

|

SU1322290A2 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для выборки команд | 1978 |

|

SU726533A1 |

| Устройство для отладки программ | 1982 |

|

SU1062708A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для обмена информацией | 1974 |

|

SU732848A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при тестировании и отладке в реальном масштабе времени программного обеспечения цифровых вычислительных машин. Цель изобрете- ния - расширение области применения устройства за счет обеспечения контроля хода программы с произвольной :структурой. Устройство для контроля за ходом выполнения программь содержит регистр 1 адресов команд переходов, дешифратор 2 кода операций, блоки 3 и 4 сравнения, буферные регистры 5 и 6, блоки 7 и 8 памяти прямых адресов, распределитель 9, коммутаторы 10 и 11, блоки 12 и 13 памяти косвенных адресов, коммутаторы 14, 15 и 16, регистр 17 текущего адреса, регистр 18 адреса данных, регистр 19 адреса, регистр 20 обмена и блок 21 равнозначности. Данное изобретение обеспечивает контроль хода по каждой ветви., программы и выявление всех ошибок переходов к незапланированным ветвям программы. 1 шт. Вх Икодне п п/хIffOffffS Ш (Л N9 00 sl Од Од

| Микропрограммное устройство управ-лЕНия C КОНТРОлЕМ пЕРЕХОдОВ | 1978 |

|

SU807289A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство управления с контролем переходов | 1983 |

|

SU1103238A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-30—Публикация

1985-07-01—Подача