Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих буферных запоминающих устройств.

Цепью изобретения является расширение области применения за счет обеспечения работы в режимах произвольного и последовательного обращений.

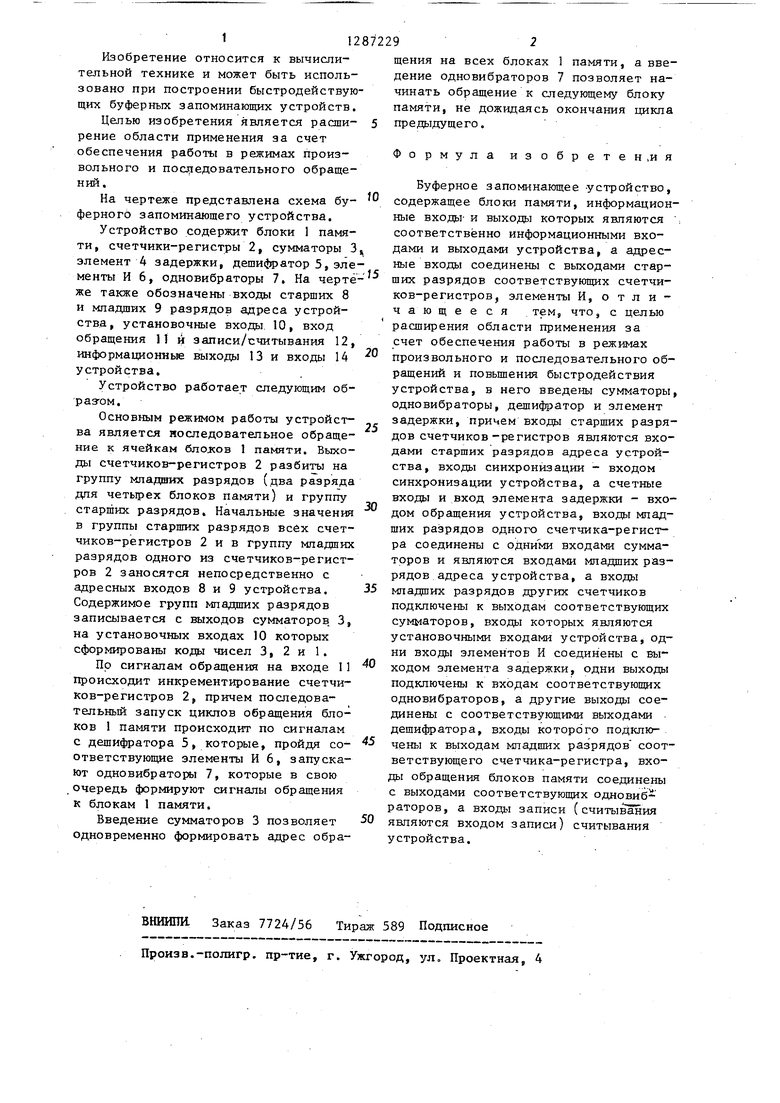

На чертеже представлена схема буферного запоминающего устройства.

Устройство содержит блоки 1 памяти, счетчики-регистры 2, сумматоры 3 элемент 4 задержки, дешифратор 5, эле менты И 6, одновибраторы 7. На черте же также обозначены входы старших 8 и младших 9 разрядов адреса устройства, установочные входы 10, вход обращения 11 и записи/считывания 12, информационные выходы 13 и входы 14 устройства.

Устройство работает следующим образ-ом.

Основным режимом работы устройства является последовательное обращение к ячейкам блодов 1 памяти. Выходы счетчиков-регистров 2 разбиты на группу младших разрядов (два разряда для четырех блоков памяти) и группу старших разрядов. Начальные значения в группы старших разрядов всех счетчиков-регистров 2 и в группу младших разрядов одного из счетчиков-регистров 2 заносятся непосредственно с адресных входов 8 и 9 устройства. Содержимое групп мпадших разрядов записывается с выходов сумматоров. 3, на установочных входах 10 которых сформированы коды чисел 3, 2 и 1.

По сигналам обращения на входе I1 происходит инкрементирование счетчиков-регистров 2, причем последовательный запуск циклов обращения блоков 1 памяти происходит по сигналам с дешифратора 5, которые, пройдя соответствующие элементы И 6, запускают одновибраторы 7, которые в свою очередь формируют сигналы обращения к блокам 1 памяти.

Введение сумматоров 3 позволяет одновременно формировать адрес обра

fO

J5

20

25

X

35

40

45

50

щения на всех блоках 1 памяти, а введение одновибраторов 7 позволяет начинать обращение к следующему блоку памяти, не дожидаясь окончания цикпа предыдущего.

Формула изобретен и я

Буферное запоминающее -устройство, содержащее блоки памяти, информационные ВХОДЫ и выходы которых являются : соответственно информационными входами и выходами устройства, а адресные входы соединены с выходами старших разрядов соответствующих счетчиков-регистров, элементы И, о т л и - чающееся тем, что, с целью расширения области применения за счет обеспечения работы в режимах произвольного и последовательного обращений и повьщ1ения быстродействия устройства, в него введены сумматоры, одновибраторы, дешифратор и элемент задержки, причем входы старших разрядов счетчиков-регистров являются входами старших разрядов адреса устройства, входы синхронизации - входом синхронизации устройства, а счетные входы и вход элемента задержки - входом обращения устройства, входы младших разрядов одного счет чика-регист- ра соединены с одними входами сумматоров и являются входами младших разрядов адреса устройства, а входы младших разрядов других счетчиков подключены к выходам соответствующих сумматоров, входы которых являются установочными входами устройства, одни входы элементов И соединены с выходом элемента задержки, одни выходы подключены к входам соответствующих одновибраторов, а другие выходы соединены с соответствующими выходами . дешифратора, входы которого подключены к выходам мпадших разрядов соответствующего счетчика-регистра, входы обращения блоков памяти соединены с выходами соответствующих одновибраторов, а входы записи (считывания являются входом записи) считывания устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адресации памяти | 1984 |

|

SU1160410A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Динамическое оперативное запоминающее устройство | 1981 |

|

SU1003142A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Запоминающее устройство | 1985 |

|

SU1249594A1 |

| Цифровой нелинейный масштабирующий преобразователь | 1981 |

|

SU1057953A1 |

| Цифровой интегратор | 1981 |

|

SU1035605A1 |

| Устройство для формирования видеосигналов | 1985 |

|

SU1317473A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих буферных запоминающих устройств. Целью изобретения является расширение области применения устройства за счет обеспечения работы в режимах произвольного и последовательного обращений. Устройство содержит блоки I памяти, счетчики-регистры 2, сумматоры 3, элемент 4 задержки, дешифратор 5, элементы И 6, одновибраторы 7. Б устройстве обеспечивается режим однократных обращений по произвольным адресам и режим последовательных обращений с повышенным быстродействием. 1 ил. (Л С ю 00 tc ю со

| Шигин А | |||

| Г | |||

| и Дерюгин А | |||

| А | |||

| Цифровые вычислительные машины | |||

| М.: Энергия, 1975, с | |||

| Катодный усилитель | 1923 |

|

SU492A1 |

| Запоминающее устройство | 1983 |

|

SU1173446A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-01-30—Публикация

1984-11-22—Подача