§

Л

ел

ел

нием входных сигналов. Устройс1во содержит 1 блоков 1 формирования воздействий и приема результатов, входной регистр 2, формирователь 3 псевдослучайной последовательности, 1 блоков 4 определения входов-выходов, дешифратор 5, регистр 6 задания режима работы, два элемента 7,8 задержки блок 9 индикации, блок 10 задания исходных данных. Устройство состоит

из иднородных по структуре блоков, совмещающих многократную подачу тестовых программ с псевдослучайными даниыьти п ку реакпий на любом входе объекта контроля. Положительный эффект достигается за счет введения операционных блоков, регистра задания режима работы, блоков определения входов-выходов и элементов задержки. 1 з.п. ф-лы, 9 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

| Устройство для формирования сдвинутых копий псевдослучайных последовательностей | 1985 |

|

SU1257815A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1288700A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

Изобретение относится к цифровой вычислительной технике и может использоваться для автоматизированного контроля блоков ЦВМ, содержащих микропроцессорные БИС. Цель изобретения - расширение функциональных возможностей устройства за счет контроля цифровых блоков с двунаправленными сигналами и произвольным назначением входных сигналов. Устройство содержит L блоков 1 формирования воздействий и приема результатов, входной регистр 2, формирователь 3 псевдослучайной последовательности, L блоков 4 определения входов-выходов, дешифратор 5, регистр 6 задания режима работы, два элемента 7, 8 задержки, блок 9 индикации, блок 10 задания исходных данных. Устройство состоит из однородных по структуре блоков, совмещающих многократную подачу тестовых программ с псевдослучайными данными и обработку реакций на любом входе объекта контроля. Положительный эффект достигается за счет введения операционных блоков, регистра задания режима работы, блоков определения входов-выходов и элементов задержки. 9 ил.

Изобретение относится к цифровой вычислительной технике и может использоваться для автоматизированного контроля блоков ЦВМ, содержащих микропроцессорные БИС.

Целью изобретении является рас;шг- рение функциональных возможностей устройства за счет контроля цифровых блоков с двунаправленными сигналами и произвольным назначением входных сигналов.

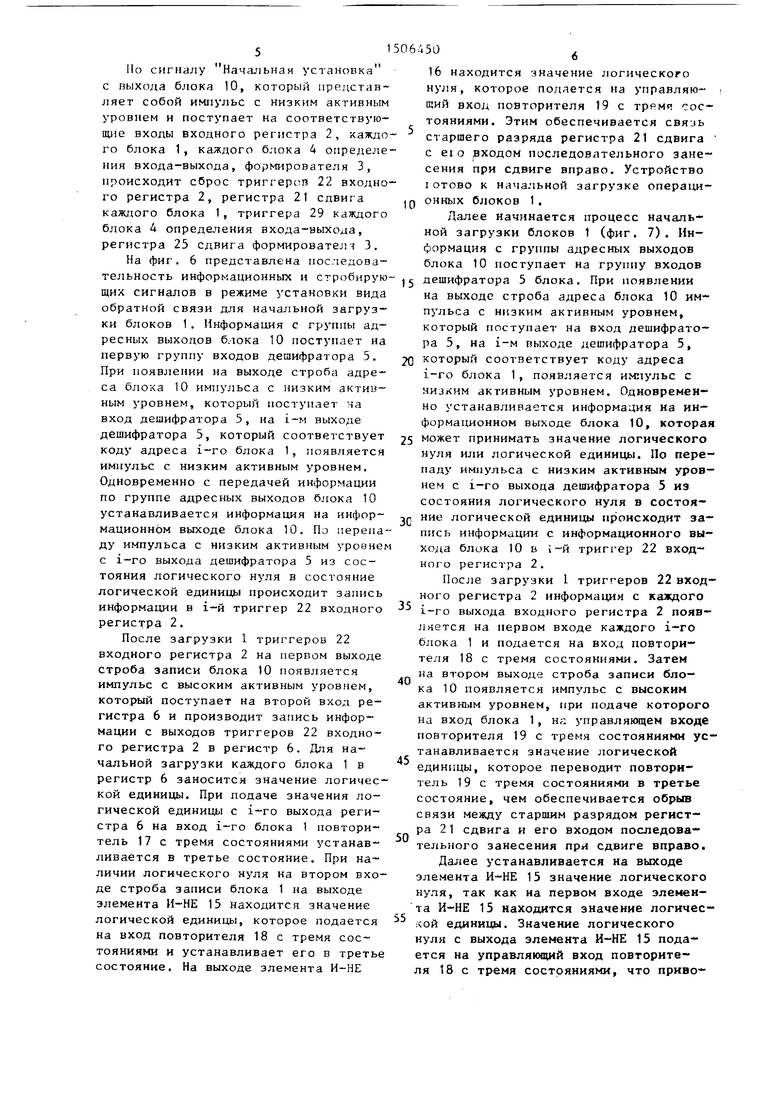

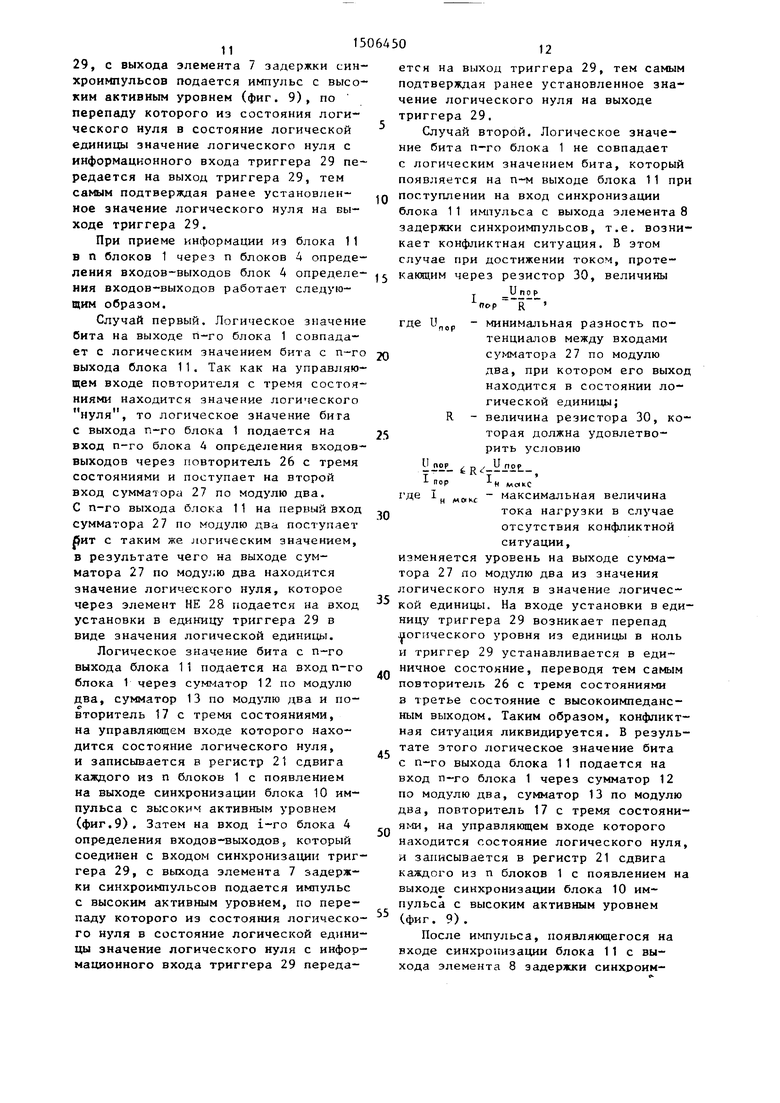

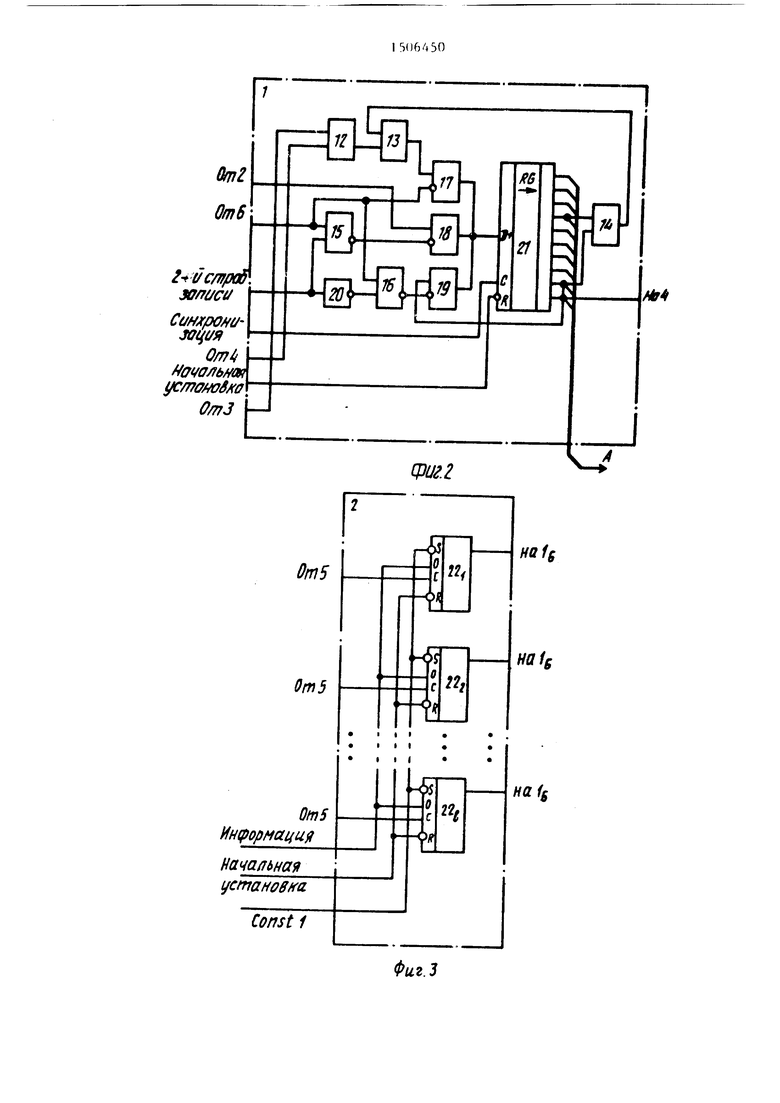

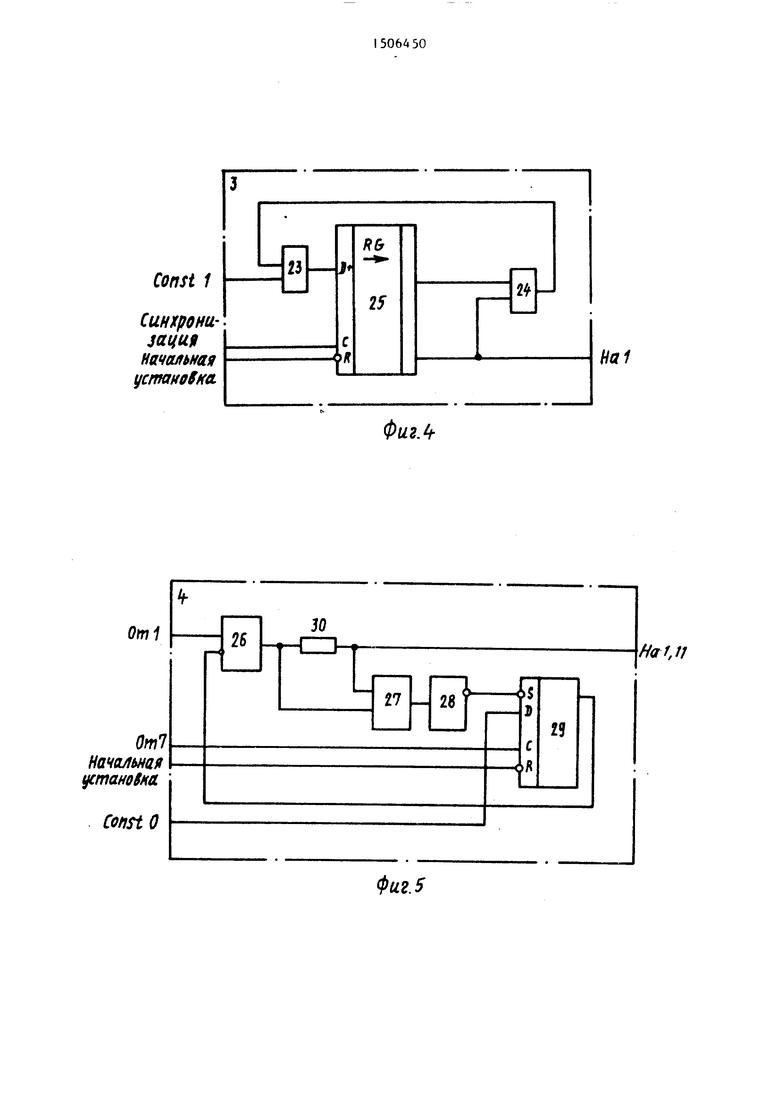

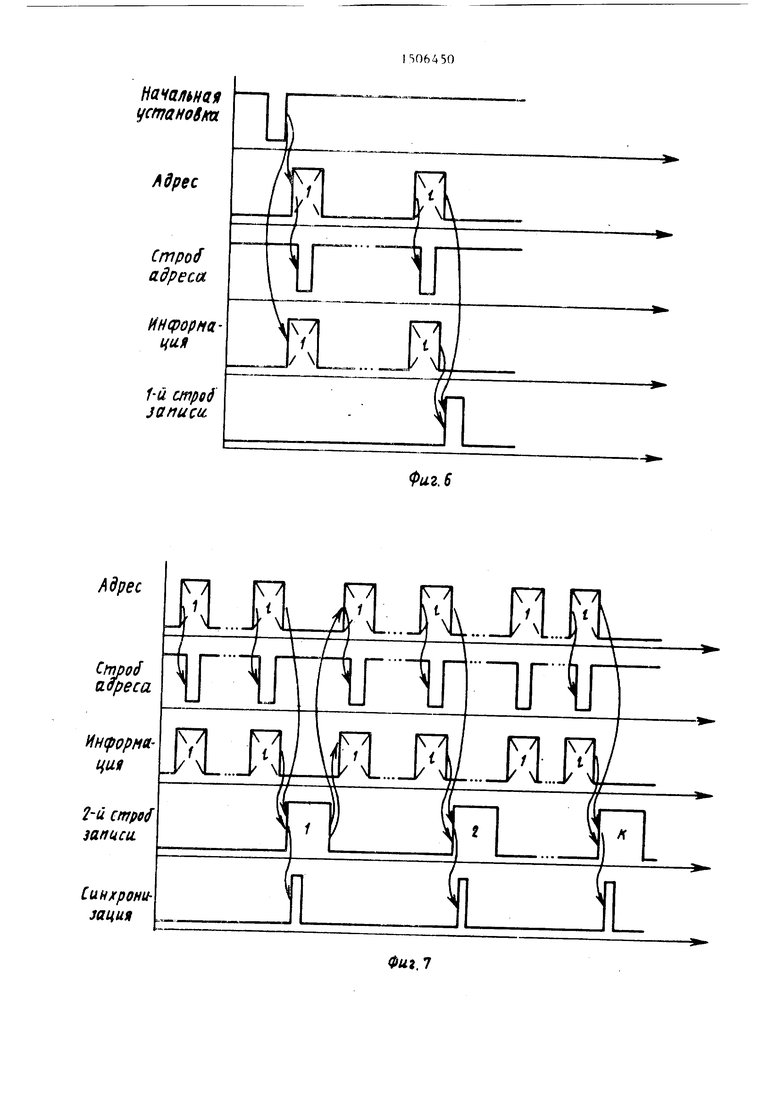

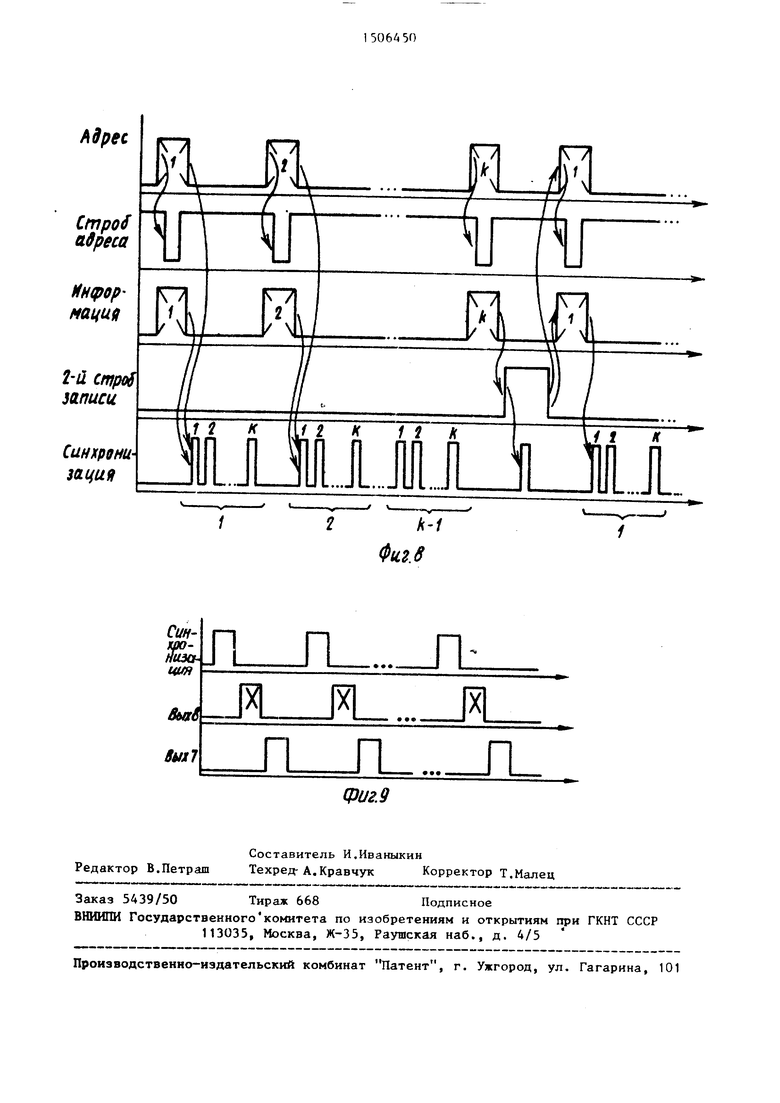

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - схема операционного блока; на фиг. 3 - схема входного регистра; на фиг. 4 - схема формирователя псевдослучайнсзй

последовательности; на фиг. 5 - схема определения входов-выходов; на фиг. 6 - 9 - зременные диаграмм, работы устройства.

Устройство содержит 1 блоков 1 формирования воздействий и приема результатов, входной регистр 2, формирователь 3 псевлослучайной последовательности, 1 блоков 4 определения входов-выходов, дешифратор 5, регистр .6 задания режима работы, два элемента 7 и 8 задержки, блок 9 индикации, блок 10 задания исходных данных и . подключено к контролируемому блоку 1 1

Операционный блок (фиг. 2) содержит сумматоры 12-14 по модулю два, элементы И-НЕ 15 и 16, повторители 17 - 19 с тремя состояниями, элемент НЕ 20, регистр 21 сдвига.

Входной регистр (фиг. 3) содержит 1 триггеров 22.

Формирователь 3 псевдослучайной последовательности (фиг. 4) содержал сумматоры 23 и 24 по модулю два и регистр 25 сдвига.

Блок 4 опреде,пепия входов-выходов . (фиг.5) содержит повторитель 26 с тремя состояниями, сумматор 27 по мо

дулю два, элемент НЕ 28, триггер 29 и регжстор 30.

Каждый i-й блок 1 используется в ,рех режимах:

в качестве i енератора тестовых низдействи.й, если 1--й вывод объекта 11 контроля является входом;

в качестве формирователя сигнатуры, еспм i-й вывод объекта 11 конт- роля является выходом;

одновременно и как генератор т-по- I ледовательности и как формирователь сигнатуры, если i-й вывод объекта 11 контроля является линией двунаправ- tj енко шины данных.

Причем в те такты процесса конт- ,пя, когда шина данных включена в режим приема информации, блок 1 используется как формирователь сигнатуры.

Входной регистр 2 служит для записи повой тестовой команды, которая входит в состав тестовой программы.

Формирователь 3 используется только как генератор т-последовательнос- ти для обеспечения функционирования блоков 1 в качестве генераторов т-по- следовательности.

Каждый i-й блок 4 определения входов-выходов используется для определения направления передачи информации на двунаправленной шине данных объекта 11 контроля.

Дешифратор 5 используется для организации доступа к любому 1-му бло- 0 ky 1 .

Регистр 6 используется для установки каждого i-го блока в требуемый режим работы.

Устройство работает следующим образом,

При включении питания состояние триггеров и регистров сдвига может быть произвольным.

0

5

51

По сигналу Начальная установка с выхода блока 10, который прецстав- ляет собой импульс с низким активным уровнем и поступает на соответствующие входы входного регистра 2, каждого блока 1, каждого блока 4 определения входа-выхода, формирователя 3, происходит сброс триггеров 22 входного регистра 2, регистра 21 сдвига каждого блока 1, триггера 29 каждого блока 4 определения входа-выхода, регистра 25 сдвига формирователя 3.

На фиг. 6 представлена последова

тельность информационных и стробирую- дешифратора 5 блока. При появлении

щих сигналов в режиме установки вида обратной связи для начальной загрузки блоков 1. Информация с группы адресных выходов блока 10 поступает на первую группу входов дешифратора 5. При появлении на выходе строба адреса блока 10 импульса с низким активным уровнем, который поступает на вход дешифратора 5, на i-м выходе дешифратора 5, который соответствует коду адреса i-ro блока 1, появляется импульс с низким активным уровнем. Одновременно с передачей информации по группе адресных выходов 6jroKa 10 устанавливается информация на информационном выходе блока 10. По перепаду импульса с низким активным уровне с i-ro выхода дешифратора 5 из состояния логического нуля в состояние логической единицы происходит запись информации в i-й триггер 22 входного регистра 2.

После загрузки 1 триггеров 22 входного регистра 2 на первом выходе строба записи блока 10 появляется импульс с высоким активным уровнем, который поступает на второй вход регистра 6 и производит запись информации с выходов триггеров 22 входного регистра 2 в регистр 6. Для начальной загрузки каждого блока 1 в регистр 6 заносится значение логической единицы. При подаче значения логической единицы с i-ro выхода регистра 6 на вход i-ro блока 1 повторитель 17 с тремя состояниями устанавливается в третье состояние. При наличии логического нуля на втором входе строба записи блока 1 на выходе элемента И-НЕ 13 находится значение логической единицы, которое подается на вход повторителя 18 с тремя состояниями и устанавливает его в третье состояние. На выходе злемента И-НЕ

16 находится значение логического нуля, которое подается на управляющий вход повторителя 19 с состояниями. Этим обеспечивается свянь старшего разряда регистра 21 сдвига с eiо уходом последовательного занесения при сдвиге вправо. Устройство готово к начальной загрузке операционных блоков 1.

Далее начинается процесс начальной загрузки блоков 1 (фиг. 7). Информация с группы адресных выходов блока 10 поступает на группу входов

дешифратора 5 блока. При появлении

0

0

5

на выходе строба адреса блока 10 импульса с низким активным уровнем, который поступает на вход дешифратора 5 , на i-M выходе дешифратора 5, который соответствует коду адреса i-ro блока 1, появляется импульс с низким активным уровнем. Одновременно устанавливается информация на информационном выходе блока 10, которая 5 может принимать значение логического нуля или логической единицы. По перепаду импульса с низким активным уровнем с 1-го выхода дешифратора 5 из состояния логического нуля в состояние логической единицы происходит запись информация с информационного выхода блока 10 в i-й триггер 22 входного регистра 2.

После загрузки 1 триггеров 22 входного регистра 2 информация с каждого i-ro выхода входного регистра 2 появляется на первом входе каждого i-ro блока 1 и подается на вход повторителя 18 с тремя состояниями. Затем на втором выхода строба записи блока 10 появляется импульс с высоким активным уровнем, при подаче которого на вход блока 1, на управляющем входе повторителя 19 с тремя состояниями устанавливается значение логической единицы, которое переводит повторитель 19 с тремя состояниями в третье состояние, чем обеспечивается обрыв связи между старшим разрядом регистра 21 сдвига и его входом последовательного занесения при сдвиге вправо.

Далее устанавливается на выходе элемента И-НЕ 15 значение логического нуля, так как на первом входе элемента И-НЕ 15 находится значение логичес- ;сой единицы. Значение логического нуля с выхода элемента И-НЕ 15 подается на управляющий вход повторителя 18 с тремя состояниями, что приво0

5

0

5

днт к передаче ннформацну с iiepBoi o входа повторителя 18 с тремя состояниями на вход гюслодов;п ельного занесения при сдвиге вправо регистра 21 сдвига. Затем на выходе синхронизации появляется импульс с высоким активным уровнем, который подается на вход синхронизации регистра 21 сдвига блока 1. В результате этого производится запись информации в первый разряд каждого регистра 21 слнига каждого блока 1 . При появлении riepe- пада из состояния логической единицы в состояние логического нуля на втором выходе строба записи блока 10., повторитель 18 с тремя состояниями вновь устанавливается в третье состояние и происходит восстановление связи между выходом старшего разряда регистра 21 сдвига и его входом последовательного занесения при слвиге вправо через повторитель 19 с тремя состояниями. Аналогичным образом производится запись информации в К разряды регистра 21 сдвига каждого блока 1, где К I г,акс|, где (I - максимальная длина тестовой команды).

Одновременно с начальной загрузкой регистров 21 сдвига блокон 1 производится загрузка регистра 23 сдви- а формирователя 3. Эргодические свойства формирователя 3 обеспечиваются соединением входа сумматора 23 по модулю два с шиной const 1, которая представляет собой вывод резистора, другой вывод которого соединен с положительным полюсом источника питания. Таким образом гарантируется ненулевое состояние регистра 25 сдвига уже после первого тактового им пульса, который подается с выхода синхронизации блока 10.

В зависимости от функционального Назначения выводов контролируемого блока i-й блок 1 устанавливается в следующий режим работы (фиг. 6):

если i-й вывод контролируемого бло ка является одним из входов командной шины, в 1-й разряд регистра 6 заносится значение логической единигда;

если i-й вывод контролируемого бло ка является одним из входов-выходов двунаправленной шины данных, в i-й разряд регистра 6 заносится значение логического нуля, которое подается на вход блока 1, соединенног о с 1 -м входом элемента И-НЕ 15. В результате этого на выходе элемента И-НЕ 15

5

0

5

0

5

0

5

0

5

появляется значение логической единицы, которое подается на управляющий вход повторителя 18 с тремя состояниями и устанавливает его в третье состояние. Значение логического нуля также подается на первый вход элемента И-НЕ 16, на выходе которого появляется значение логической единицы, которое подается на управляющий вход повторителя 19 с тремя состояниями, устанав:;иная его в третье состояние. Кроме этого, значение логического нуля подается на управляющий вход повторителя 27 с тремя состояниями. В результате этого информация с определенных выходов регистра 21 сдвиги подается на входы сумматора 14 по модулю два, с выхода которого подается через сумматор 13 по мoдyJиo два, и через повторитель 17 с тремя состояниями на вход последовательного занесения при сдвиге вправо регистра 21 сдвига. Этим обеспечивается установление i-ro блока 1 в режим генератора т-последовательности -- формирователя сигнатуры.

После установления режима работы блоков 1 (адаптация устройства) начинается процесс подачи тестовых команд на контролируемый блок (фиг. 8).

Информа1у я с группы адресных выходов блока 10 поступает на первую группу входов дешифратора 5. При появлении на выходе строба адреса блока 10 импульса с низким активным уровнем, который поступает на вход дешифратора 5, на j-м выходе дешифратора 5 (,...,K), который соответствует коду адреса j-ro блока 1, появляется импульс с низким активным уровнем. Одновременно устанавливается информация на информационном выходе блока 10, которая может принимать значение логического нуля или логической единицы. По перепаду импульса с низким активным уровнем с j-ro выхода дешифратора 3 из состояния логического нуля в состояние логической единицы происходит запись информации в j-й триггер 22 входного регистра 2. После загрузки каждого из К-1 триггеров 22 входного регистра 2 информация с каждого j-ro выхода входного регистра 2 появляется на входе каждого j-ro блока 1 и подается на вход повторителя 18 с тремя состояниями.

5

Затем на выходе синхронизации блока 10 появляется последовательность из К (К - разрядность регистра 21 сдвига) импульсов, которая подается на вход сдвига блока 1, соединенного с входом синхронизации регистра 21 сдвига. Так как время формирования одного бита на информационном выходе блока 10 больше времени генерации Q последовательности из К импульсов, которые подаются с выхода синхронизации блока 10 на входы синхронизации регистров 2i сдвига каждого из 1 блоков 1, то до появления следую- 15 щего бита на информационном выходе блока 10 тестовая программа, находя- щаяся в регистрах 21 сдвига каждого из К блоков 1, подается на блок 11 через блоки 4 определения входов- 20 выходов и возвращается в исходное состояние в регистрах 21 сдвига каждого из К блоков 1, При этом на двунаправленную шину данных с каждого из п блоков 1 через п блоков А опре- 25 деления входов-выходов подается псевдослучайная т-последовательность. В течение времени формирования К-1 бит на информационном выходе блока 10 происходит многократная (К-1 раз) 30 подача одних и тех же тестовых команд (мультипликация) с различными (псевдослучайными) наборами данных на блок 11 через 1 блоков 4 определения входов-выходОБ. Ненулевое состоя- с ине каждого из п блоков 1 обеспечивается начальной загрузкой от формирователя 3. После установления на информационном выходе блока 10 К-го логического значения разряда команды на втором выходе строба записи блока 10 появляется импульс с высоким активным уровнем, который устанавливает повторитель 19 с тремя состояниями в третье состояние, а на управ- д ляющем входе повторителя 18 с тремя состояниями устанавливает значение логического нуля в каждом из К блоков 1.

При появлении на выходе синхрони- 50 ации блока 10 импульса с высоким акивным уровнем происходит запись ноой, сформированной во входном регитре 2, тестовой команды в каждый из локов 1. При перепаде импульса на 55 тором выходе строба записи блока 10 з состояния логической единицы в сосояние логического нуля повторитель 18 с тремя состояниями устанавливает

ся в третье состояние и восстанавливается связь между старшим разрядом регистра 21 сдвига и его входом последовательного занесения при сдвиге вправо через повторитель 19 с тремя состояниями каждого из К блоков 1. Завершение записи новой тестовой команды в каждьй из К блоков 1, процесс формирования следующих тестовых команд и подача тестовых программ на блок 11 продолжаются в течение заданного времени.

Передача информации с выходов 1 блоков 1 на блок 11 через 1 блоков 4 определения входов-выходов происходит следующим образом.

После сигнала с низким активным уровнем, который поступает с выхода начальной установки блока 10 на вход нач.альной установки каждого i-ro блока 4 определения входов-выходов и по- дается на вход установки в ноль триггера 29, на выходе триггера 29 каждо- fo i-ro блока 4 определения входов- выходов находится состояние логического нуля, которое подается на управляющий вход повторителя 26 с тремя состояниями. Информация с выхода каждого i-ro блока 1 подается на информационный вход i-ro блока 4 определения входов-выходов через повторитель

26с тремя состояниями и через резистора 30, второй вывод которого соединен с выходом блока 4 определения входов-выходов, подается на i-й вход блока 11. Эта информация поступает

в блок 11 при появлении на входе синхронизации блока 11 импульса с элемента 8 задержки синхроимпульсов. Время задержки элемента 8 задержки синхроимпульсов определяется временем прохождения информации с выхода i-ro блока 1 на i-й нход блока 11 (фиг,9). При этом на выходе триггера 29 каждого i-ro блока 4 определения входов- выходов остается значение логического нуля, так как на входы сумматора

27по модулю два поступают одинаковые логические значения. В результате на выходе сумматора 27 по модулю два находится значение логического нуля, которое через злемент НЕ 28 подается на вход установки в единицу триггера 29 в виде значения логической единицы.

Затем на вход i-ro блока 4 определения входов-выходов, который соединен с входом синхронизации триггера

11

29, с выхода элемента 7 задержки синхроимпульсов подается импульс с высоким активным уровнем (фиг. 9), по перепаду которого из состояния логического нуля в состояние логической единицы значение логического нуля с информационного входа триггера 29 передается на выход триггера 29, тем самым подтверждая ранее установленное значение логического нуля на выходе триггера 29.

При приеме информации из блока 11 в п блоков 1 через п блоков 4 определения входов-выходов блок 4 определе ния входов-выходов работает следующим образом.

Случай первый. Логическое значени бита на выходе ri-ro блока 1 совпадает с логическим значением бита с п-г выхода блока 11. Так как на управляющем входе повторителя с тремя состояниями находится значение логического нуля, то логическое значение бита с выхода п-го блока 1 подается на вход п-го блока 4 определения входов выходов через повторитель 26 с тремя состояниями и поступает на второй вход сумматора 27 по модулю два. С п-го выхода блока 11 на первый вход сумматора 27 по модулю два поступает бит с таким же логическим значением, в результате чего на выходе сумматора 27 по мoдyJ;ю два находится значение логического нуля, которое через элемент НЕ 28 подается на вход установки в единицу триггера 29 в виде значения логической единицы.

Логическое значение бита с п-го выхода блока 11 подается на вход п-г блока 1 через сумг-1атор 12 по модулю два, сумматор 13 по модулю два и повторитель 17 с тремя состояниями, на управляющем входе которого находится состояние логического нуля, и записывается в регистр 21 сдвига каждого из п блоков 1 с появлением на выходе синхронизации блока 10 импульса с высоким активным уровнем (фиг.9), Затем на вход i-ro блока 4 определения входов-выходов который соединен с входом синхронизации триггера 29, с выхода элемента 7 задержки синхроимпульсов подается импульс с высоким активным уровнем, по перепаду которого из состояния логического нуля в состояние логической единицы значение логического нуля с информационного входа триггера 29 переда

10

где и

20

25

где

пор

I

кающим

12

триггера 29,

ется на выход триггера сУ, тем самым подтверждая ранее установленное значение логического нуля на выходе триггера 29.

Случай второй. Логическое значение бита п-го блока 1 не совпадает с логическим значением бита, который появляется на п-м выходе блока 11 при поступлении на вход синхронизации блока 11 импульса с выхода элемента 8 задержки синхроимпульсов, т.е. возникает конфликтная ситуация. В этом случае при достижении током, проте- через резистор 30, величины

и по р ор

минимальная разность потенциалов между входами сумматора 27 по модулю два, при котором его выход находится в состоянии логической единицы; величина резистора 30, которая должна удовлетворить условию и пор

пор

R p°f, кг1- ппв-L 1

Н «оке

30

изменяется

тора 27 по

35

40

45

50

55

Н макс

- максимальная величина тока нагрузки в случае отсутствия конфликтной ситуации,

уровень на выходе сумма- модулю два из значения логического нуля в значение логической единицы. На входе установки в единицу триггера 29 возникает перепад логического уровня из единицы в ноль

и триггер 29 устанавливается в единичное состояние, переводя тем самым повторитель 26 с тремя состояниями 3 третье состояние с высокоимпеданс- ным выходом. Таким образом, конфликтная ситуация ликвидируется. В результате этого логическое значение бита с п-го выхода блока 11 подается на вход п-го блока 1 через сумматор 12 по модулю два, сумматор 13 по модулю два, повторитель 17 с тремя состояниями, на управляющем входе которого находится состояние логического нуля, и записывается в регистр 21 сдвига каждого из п блоков 1 с появлением на выходе синхронизации блока 10 импульса с высоким активным уровнем (фиг. 9).

После импульса, появляющегося на входе синхронизации блока 11 с выхода элемента 8 задержки синхроимпульсов на вход каждого i-ro блока А определения входов-выходов, который соединен с входом синхронизации триггера 29, с выхода элемента 7 задержки синхроимпульсов подается импульс с высоким активным уровнем, по перепаду которого из состояния логического нуля в состояние логической единицы значение логического нуля с информационного входа триггера 29 передается на выход триггера 29, т.е. устанавливая его в ноль.

Время задержки между импульсами с выхода элемента 8 задержки синхроимпульсов и импульсами с выхода элемента 7 задержки синхроимпульсов определяется быстродействием блока 11 и временем записи информации в регистр 21 сдвига каждого блока 1.

Импульсы с высоким активным уровнем с выхода синхронизации блока 10 подаются одновременно на вход каждого i-ro блока 1 и на вход формирователя 3, с выхода которого псевдослучайная т-последовательность подается на вход каждого п-го блока 1, а записывается в каждый регистр 21 сдвига каждого п-го блока 1 через сумматор 12 по модулю два, сумматор 23 по модулю два и повторитель 17 с тремя состояниями при появлении на выходе синхронизации блока 10 импульса с высоким активным уровнем. Этим обеспечивается ненулевое состояние каждого из п блоков 1 в процессе работы устройства.

Вычисленные сигнатуры индицируются блоком 9 индикации и сравниваются с сигнатурами, полученными в результате проверки исправного цифрового блока или математического моделирования . Контролируемый цифровой блок считается исправным, если указанные (Сигнатуры совпадают.

Блок to может быть реализован на основе любого устройства, работа которого обеспечивает требуемую последовательность информационных и стробирующих сигналов, например Электроника-60 с устройством параллельного обмена И2 15КС-180-032.

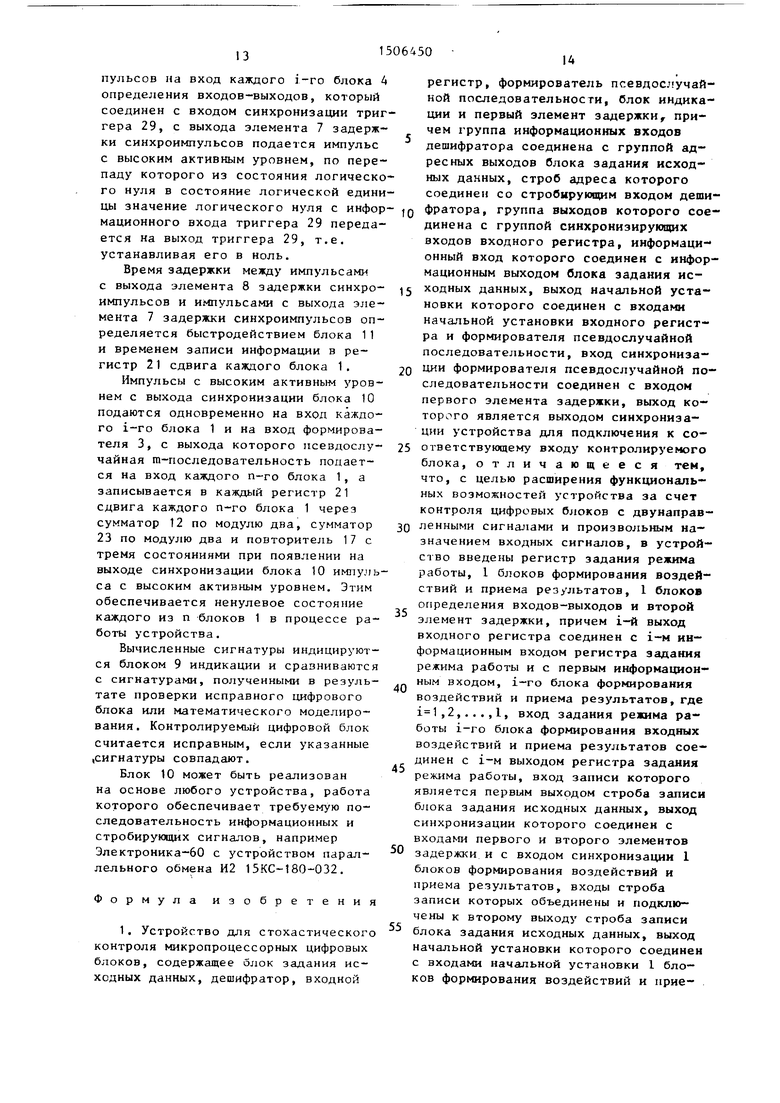

Формула изобретения

0

5

0

5

0

5

0

5

0

5

регистр, формирователь псевдос/ учай- ной последовательности, блок индикации и первый элемент задержки причем группа информационных входов дешифратора соединена с группой ад ресных выходов блока задания исходных данных, строб адреса которого соединен со стробнрующим входом дешифратора, группа выходов которого соединена с группой синхронизирующих входов входного регистра, информаци- онный вход которого соединен с информационным выходом блока задания исходных данных, выход начальной установки которого соединен с входами начальной установки входного регистра и формирователя псевдослучайной последовательности, вход синхронизации формирователя псевдослучайной последовательности соединен с входом первого элемента задержки, выход которого является выходом синхронизации устройства для подключения к соответствующему входу контролируемого блока, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет контроля цифровых блоков с двунаправленными сигналами и произвольным назначением входных сигналов, в устройство введены регистр задания режима работы, 1 блоков формирования воздействий и приема результатов, 1 блоков определения входов-выходов и второй элемент задержки, причем i-и выход входного регистра соединен с i-м информационным входом регистра задания режима работы и с первым информационным входом, i-го блока формирования воздействий и приема результатов, где ,2,...,, вход задания режима работы i-ro блока формирования входных воздействий и приема результатов соединен с i-M выходом регистра задания режима работы, вход записи которого является первым выходом строба записи блока задания исходных данных, выход синхронизации которого соединен с входами первого и второго элементов задержки и с входом синхронизации 1 блоков формирования воздействий и приема результатов, входы строба записи которых объединены и подключены к второму выходу строба записи блока задания исходных данных, выход начальной установки которого соединен с входами начальной установки 1 блоков формирования воздействий и прие-

ма результатов и 1 блоков определения входов-выходов, входы псевдо- i случайной последовательности блоков формирования воздействий и приема ре- зультйтов объединены и подключены к выходу формирователя псевдослучайной последовательности, входы синхронизации блоков определения входоввыходов объединены и подключены к вы- д ход первого сумматора по модулю два

ходу второго элемента задержки, выход i-ro блока формирования воздействий и приема результатов соединен с информационным входом i-ro блока определения входов-выходов, вход-выход которого соединен с вторит информационным входом i-ro блока формирования воздействий и приема результатов и является i-M входом-выходом группы информационных входов-выходов устройства для подключения к контролируемому блоку, группа информационных выходов i-ro блока формирования воздействий и приема результатов соединена с i-и группой входов блока индикации.

15

20

25

30

35

40

соединен с первым входом второго сум матора по модулю два, выход которого соединен с информационным входом вто рого формирователя с тремя состояния ми, управляющий вход которого соединен с первыми входами элементов И-НЕ и является входом задания режима работы блока, информационный вход третьего формирователя с тремя состояниями является первым информацион ным входом блока, вход элемента НЕ объединен с вторым входом первого элемента И-НЕ и является вторым входом строба записи блока, выход элемента НЕ соединен с вторым входом вт рого элемента И-НЕ, выходы первого и второго эле1 1ентов И-НЕ соединены с управляющими входами соответственн третьего и первого формирователей с тремя состояниями, тактовый вход и вход обнуления регистра сдвига являются соответственно входом синхронизации и входом начальной установки блока, информационный вход и вход псевдослучайной последовательности которого соединены соответственно с первым и вторым входами третьего сумматора по модулю два, выход которого соединен с вторым входом второг сумматора по модулю два.

т(1,К), п(1,К), К - разрядность регистра сдвига, К-й разрядный выход регистра сдвига соединен с информационным входом первого формирователя с тремя состояниями и является информационным выходом блока, разрядные выходы регистра сдвига образуют группу информационных выходов блока, вы5

0

5

0

5

0

соединен с первым входом второго сумматора по модулю два, выход которого соединен с информационным входом второго формирователя с тремя состояниями, управляющий вход которого соединен с первыми входами элементов И-НЕ и является входом задания режима работы блока, информационный вход третьего формирователя с тремя состояниями является первым информационным входом блока, вход элемента НЕ объединен с вторым входом первого элемента И-НЕ и является вторым входом строба записи блока, выход элемента НЕ соединен с вторым входом второго элемента И-НЕ, выходы первого и второго эле1 1ентов И-НЕ соединены с управляющими входами соответственно третьего и первого формирователей с тремя состояниями, тактовый вход и вход обнуления регистра сдвига являются соответственно входом синхронизации и входом начальной установки блока, информационный вход и вход псевдослучайной последовательности которого соединены соответственно с первым и вторым входами третьего сумматора по модулю два, выход которого соединен с вторым входом второго сумматора по модулю два.

м

OfffS

2 ислгр(зб

CuH foowЩ{/Я

0/774

yC/r7O S/(O

0/7J3

OfnS Ин(рормациц

Начальная

ijcmaHoBffu Const 1

Hff

Фиг.З

Oml

Om7

Нача/гма г ycmaf/ofM j

Co fist 0

0мгЛ

Ha 1.11

Фиг.5

Адрес

CfTjfio/ иореса

ИН(рОрМЛ

ций

2-й записи.

Ыи кропи- зиции

Фаг. 6

Фиг,7

Адрес

Cmpof адреса

HHtpop- мйциа

2-й cmpog записи

Синхроны

i к i 2 к / г л

Син- ию- низаHtfft

А-/

Фаг.в

| Устройство для контроля логических блоков | 1982 |

|

SU1037257A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-07—Публикация

1987-07-20—Подача