Изобретение относится к электросвязи и может использоваться в системах передачи данных с решающей обратной связью с адаптивным кодированием передаваемой информации.

Цель изобретения - сокраш,ение времени оценки состояния дискретного канала.

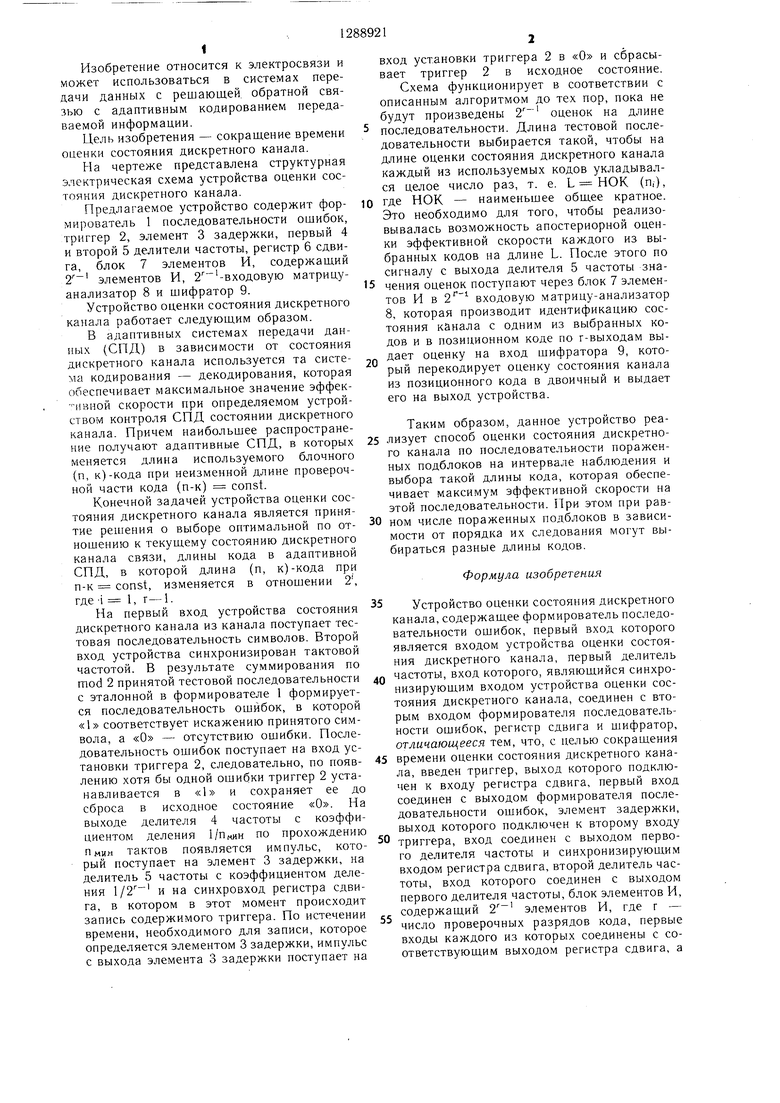

На чертеже представлена структурная электрическая схема устройства оценки состояния дискретного канала.

вход установки триггера 2 в «О и сбрасывает триггер 2 в исходное состояние. Схема функционирует в соответствии с описанным алгоритмом до тех пор, пока не будут произведены оценок на длине последовательности. Длина тестовой последовательности выбирается такой, чтобы на длине оценки состояния дискретного канала каждый из используемых кодов укладывался целое число раз, т. е. L НОК (п,),

Предлагаемое устройство содержит фор- ю где НОК - наименьшее общее кратное.

мирователь 1 последовательности ошибок, триггер 2, элемент 3 задержки, первый 4 и второй 5 делители частоты, регистр 6 сдвига, блок 7 элементов И, содержащий элементов И, 2 -входовую матрицу- анализатор 8 и шифратор 9.

Устройство оценки состояния дискретного канала работает следующим образом.

В адаптивных системах передачи данных (СПД) в зависимости от состояния дискретного канала используется та система кодирования - декодирования, которая обеспечивает максимальное значение эффек- цвной скорости при определяемом устройством контроля СПД состоянии дискретного канала. Причем наибольщее распространеЭто необходимо для того, чтобы реализовывалась возможность апостериорной оценки эффективной скорости каждого из выбранных кодов на длине L. После этого по сигналу с выхода делителя 5 частоты зна- 15 чения оценок поступают через блок 7 элементов И в входовую матрицу-анализатор 8, которая производит идентификацию состояния канала с одним из выбранных кодов и в позиционном коде по г-выходам выдает оценку на вход шифратора 9, который перекодирует оценку состояния канала из позиционного кода в двоичный и выдает его на выход устройства.

Таким образом, данное устройство реа20

ние получают адаптивные СПД, в которых 25 лизует способ оценки состояния дискретного канала по последовательности пораженных подблоков на интервале наблюдения и выбора такой длины кода, которая обеспечивает максимум эффективной скорости на этой последовательности. При этом при равменяется длина используемого блочного (п, к)-кода при неизменной длине проверочной части кода (п-к) const.

Конечной задачей устройства оценки состояния дискретного канала является принятие решения о выборе оптимальной по от- 30 ном числе пораженных подблоков в зависимости от порядка их следования могут выбираться разные длины кодов.

Формула изобретения

Устройство оценки состояния дискретного канала, содержащее формирователь последовательности ошибок, первый вход которого является входом устройства оценки состояния дискретного канала, первый делитель

ношению к текущему состоянию дискретного канала связи, длины кода в адаптивной СПД, в которой длина (п, к)-кода при п-к const, изменяется в отношении 2, где , г- 1.

На первый вход устройства состояния дискретного канала из канала поступает тестовая последовательность символов. Второй вход устройства синхронизирован тактовой частотой. В результате суммирования по

mod 2 принятой тестовой последовательности 40 частоты, вход которого, являющийся синхро- с эталонной в формирователе 1 формирует-.-.,-г.,„,„,,.. „„„п.,.. .-.„ ,,„ „

ся последовательность ошибок, в которой «1 соответствует искажению принятого символа, а «О - отсутствию ошибки. Последовательность ошибок поступает на вход уснизирующим входом устройства оценки состояния дискретного канала, соединен с вторым входом формирователя последовательности ошибок, регистр сдвига и шифратор, отличающееся тем, что, с целью сокращения

тановки триггера 2, следовательно, по появ- 45 времени оценки состояния дискретного каналению хотя бы одной ошибки триггер 2 устанавливается в «1 и сохраняет ее до сброса в исходное состояние «О. На выходе делителя 4 частоты с коэффициентом деления 1/Пмин по прохождению Пмин тактов появляется импульс, который поступает на элемент 3 задержки, на делитель 5 частоты с коэффициентом деления 1/2 и на сиихровход регистра сдвига, в котором в этот момент происходит запись содержимого триггера. По истечении времени, необходимого для записи, которое определяется элементом 3 задержки, импульс с выхода элемента 3 задержки поступает на

50

55

ла, введен триггер, выход которого подключен к входу регистра сдвига, первый вход соединен с выходом формирователя последовательности ошибок, элемент задержки, выход которого подключен к второму входу триггера, вход соединен с выходом первого делителя частоты и синхронизирующим входом регистра сдвига, второй делитель частоты, вход которого соединен с выходом первого делителя частоты, блок элементов И, содержащий элементов И, где г - число проверочных разрядов кода, первые входы каждого из которых соединены с соответствующим выходом регистра сдвига, а

вход установки триггера 2 в «О и сбрасывает триггер 2 в исходное состояние. Схема функционирует в соответствии с описанным алгоритмом до тех пор, пока не будут произведены оценок на длине последовательности. Длина тестовой последовательности выбирается такой, чтобы на длине оценки состояния дискретного канала каждый из используемых кодов укладывался целое число раз, т. е. L НОК (п,),

где НОК - наименьшее общее кратное.

Это необходимо для того, чтобы реализовывалась возможность апостериорной оценки эффективной скорости каждого из выбранных кодов на длине L. После этого по сигналу с выхода делителя 5 частоты зна- чения оценок поступают через блок 7 элементов И в входовую матрицу-анализатор 8, которая производит идентификацию состояния канала с одним из выбранных кодов и в позиционном коде по г-выходам выдает оценку на вход шифратора 9, который перекодирует оценку состояния канала из позиционного кода в двоичный и выдает его на выход устройства.

Таким образом, данное устройство реа

частоты, вход которого, являющийся синхро- .-.,-г.,„,„,,.. „„„п.,.. .-.„ ,,„ „

низирующим входом устройства оценки состояния дискретного канала, соединен с вторым входом формирователя последовательности ошибок, регистр сдвига и шифратор, отличающееся тем, что, с целью сокращения

ла, введен триггер, выход которого подключен к входу регистра сдвига, первый вход соединен с выходом формирователя последовательности ошибок, элемент задержки, выход которого подключен к второму входу триггера, вход соединен с выходом первого делителя частоты и синхронизирующим входом регистра сдвига, второй делитель частоты, вход которого соединен с выходом первого делителя частоты, блок элементов И, содержащий элементов И, где г - число проверочных разрядов кода, первые входы каждого из которых соединены с соответствующим выходом регистра сдвига, а

1288921 34

вторые входы соединены с выходом второгота И, а выходы подключены к соответ- делителя частоты и 2 -входовая матрица-ствующим входам шифратора, выходы кото- анализатор, каждый из входов которой сое-рого являются выходами устройства оценки динен с выходом соответствующего элемен-состояния дискретного канала.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА СВЯЗИ | 2002 |

|

RU2216865C1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ДОСТОВЕРНОСТИ ИНФОРМАЦИИ, ПЕРЕДАВАЕМОЙ ЦИКЛИЧЕСКИМ КОДоМ | 1971 |

|

SU316204A1 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2014 |

|

RU2563145C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

Изобретение относится к электросвязи. Цель изобретения - сокращение времени оценки состояния дискретного канала. Устрво содержит формирователь 1 последовательности ошибок, делитель 4 частоты, регистр 6 сдвига, шифратор 9. Вновь введены триггер 2, эл-т 3 задержки, делитель 5 частоты, блок эл-тов И 7, содержаш,ий эл-тов И, 2 -входовая матрица-анализатор 8 (г - число проверочных разрядов кода). Устройство реализует способ оценки состояния дискретного канала но последовательности пораженных подблоков на интервале наблюдения .и выбора такой длины кода, к-рая обеспечивает макс, эффективной скорости на этой последовательности. При этом при. равном числе пораженных подблоков в зависимости от порядка их следования могут выбираться разные длины кодов. 1 ил. ВхЛ (Л ND ОС 00 (X) |С ; 2 г%г

| Советов Б | |||

| Я., Стах В | |||

| М | |||

| Построение адаптивных систем передачи информации для автоматизированного управления.-Л.: Энергоиздат, 1982, с | |||

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Элементы теории передачи дискретной информации./Под ред | |||

| Л | |||

| П | |||

| Пуртова.-М.: Связь, 1972, с | |||

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-02-07—Публикация

1985-09-18—Подача