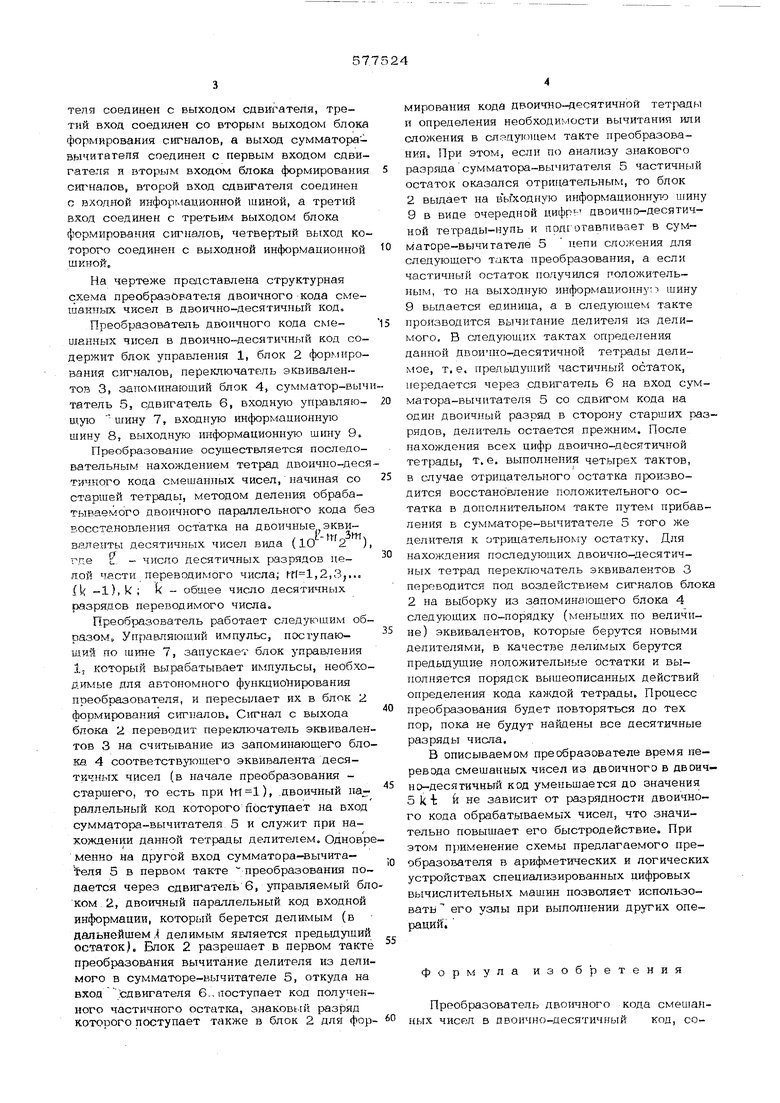

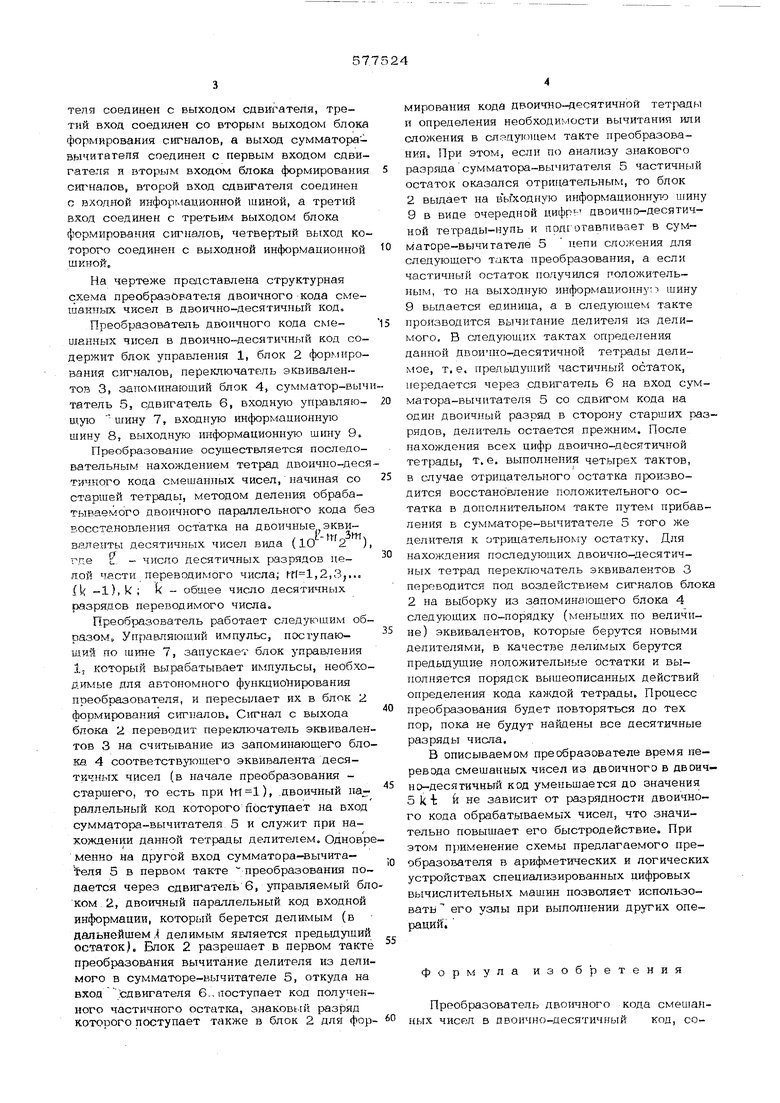

Изобретение относится к области вычисл гельной техники и автоматики и может быть использовано в специализированных арифметических и логических устройствах, оперирующих в двоичной системе счисления и выдающих результат обработки информации для восприятия в десятичной системе. Известен преобразователь кодов из двоично-десятичной системы счисления в двоич ную, содержащий блок управления, переключатель экивалентов, запоминающее устройство двоичных эквивапечтов, распределитель двоичных разрядов по весам, регистр числа, одноразрядный двоичный сумматор, регистр результата i Быстродействие этого преобразователя недостаточно высоко и (зависит от числа двоичных разрядов П; преобразование К-Разрядного десятичного числа длится в течение времени 4k hi рде - -длительность одного такта преобразования. Из известных преобразователей двоичного кода в двоично десятичный наиболее бли ким по технической с тиности к заявленному является преобразователь двоичного кода смешанных чисел в двоично-десятичный код, содержащий блок управления,, вход , соединен с входной управляющей шиной,выход - с первым входом блока формирован1ш сигналов, первый выход которого соединен через переключатель эквивалентов с входом запом1шающего блока . . Схема этого преобразователя весьма проста, а перевод цвоичного кода смешанных чисел в двоичнодесятичный код осуществляется беспрограммным путем с использованием двоичных / эквивалентов десятичных чисел вида (10Г J. где 1 -ОД,2,3Однако быстродейст вие данного преобразоватегя также зависит от числа двоичных разрядов ц , а время перевода достигает значен1Ш 9 k Н t . Целью изобретения является повышение быстродействрш преобразования двоичного кода смещаиных чисел в двоично-десятичнь Й ход. Это достигается тем, что в преобразователь введены сумматор-вычитатель и (сдвигатель, причем первый вход сумматораJвычитaтeля соедшген с выходом запомянаюшего блока, второй вход сумматора вычйта- теля соединен с выходом сдвигатепя, третий вход соединен со вторым выходом блока формирования сигналов, а выход сумматоравычитатепя соединен с первым входом сдвигателя и вторым входом блока формирования сшнапов, второй вход сдвигателя соединен с входной инфоркшционной шиной, а третий вход соединен с третьим выходом блока формирования сигналов, четвертый выход ко торого соединен с выходной информационной шкной„ На чертеже представлена структурная схема преобразователя двоичного кода смешанных чисел в двоично-десятичный код. Преобразователь двоичного кода смешанных чисел в двоично-десятичный код содержит блок управления 1, блок 2 ({юрмирования сигналов, переключатель эквивалентов 3, запо {инающий блок 4, сумматор-выч татель 5, сдвигатель 6, входную унравляюшую шину 7, входную информационную шину 8, выходную информационную шину 9. Преобразование осуществляется последовательным нахождением тетрад двоично-деся тичного кода смешанных чисел, начиная со старшей тетрады, методом деления обрабатываемого двоичного параллельного кода без восстановления остатка на двоичные, экви() валенты десятичных чисел вида ;: - число десятичных разрядов целой части переводимого числа; ,2,3,... Ik -1), k ; k - общее число десятичных разрядов переводимого числа. Преобразователь работает следующим образом УнраЕшяюший импульс, псюгупаю- ший по ш}ше 7, запускает блок управления 1; который вырабатывает импульсы, необходимые для автономного функционирования преобразователя, и пересылает их в блок 2 формирован1ш сигналов. CitrHaa с выхода блока 2 переводит переключатель эквивален тов 3 на считывание из запоминающего бло ка 4 соответствуюшего эквивалента десятичных чисел (в начале преобразования старшего, то есть при ), .двоичный параллельный код которогойоступает на вход сумматора-вычитателя 5 и служит при нахождении данной тетрады делителем. Одновре менно на другой вход сумматора-вычита- еля 5 в первом такте преобразования подается через сдвигатель 6, управляемый бл ком, 2, двоичный параллельный код входной информации, который берется делимым (в дальнейшем Д делимым является предьщуший остаток). Бпок 2 разрешает в первом такте преобразования вычитание делителя из делимого в сумматоре-вычитателе 5, откуда на вход сдвигателя G-. поступает код полученного частичного остат1са, знаковь-гй разряд которого поступает также в блок 2 для формирования кода двоично-десятичной тетрады и определения необходимости вычитания или сложения в сладук.яием такте преобразования. При этом, если по анализу знакового разряда сумматора-вычитателя 5 частичный остаток оказался отрицательным, то блок 2 выдает на выходную информационную шину 9 в виде очередной цифрь двоично-десятичной тетрады-нупь и подготавпивает в сумма то ре.-вы читателе 5 пени сложения для следующего такта преобразования, а если частичный остаток получился положительным, то на выходную информационнуп шину 9 выдается единица, а в следующем такте производится вычитание делителя из делимого, В следующих тактах определения данной Двоично-десятичной тетрады делимое, т. е. предьщуший частичный остаток, передается через сдвигатель 6 на вход сумматора-вычитателя 5 со сдвигом кода на один двоичный разряд в сторону старших разрядов, делитель остается прежним. После нахождения всех цифр двоично-десятичной тетрады, т.е. выполнения четырех тактов, в случае отрицательного остат1са производится восстановление положительного остатка в дополнительном такте путем прибавления в сумматоре-вычитателе 5 того же делителя к отрицательному остатку. Для нахождения последующих двоично-десятичных тетрад переключатель эквивалентов 3 переводится под воздействием сигналов блока 2 на выборку из запоминающего блока 4 следующих по-порядку (меньших но величине) эквивалентов, которые берутся новыми делителями, в качестве делимых берутся предьщущие положительные остатки и выполняется порядок вышеописанных действий определения кода каждой тетрады. Процесс преобразования будет повторяться до тех пор, пока не будут найдены все десятичные разряды числа. В описываемом преобразователе время перевода смешанных чисел из двоичного в двоично-десятичный код уменьшается до значения 5 k t и не зависит от разрядности двоичного кода обрабатываемых чисел, что значительно повышает его быстродействие. При этом применение схемы предлагаемого преобразователя в арифметических и логических устройствах специализированных цифровых вычислительных машин позволяет использовати его узлы при выполнении других операций. формула изобретения Преобразователь дво1гчного кода смешанных чисел в двоично-десятичный код, содержащий блок управления, вход которого со:единен с входной управляющей шиной, выход - с первым входом блока формирования сигна|дов, первый выход которого соединен через переключатель эквивалентов с входом запо- s минаюшего блока, отличаю ший:с я тем, что, с целью повышения быстродействия, в него введены сумматор-вычитатель и сдвигатель, причем первый вход сумматора-вычитателя соединен с выходом ю запоминающего блока, второй вход сумматоравычитателя соединен с выходом сдвигателя, третий вход соединен со вторым выхо- . дом блока формирования сигналов, а выход

сумматора-вычитателя соединен с первым входом сдвигателя и вторым входом блока формирования сигналов, второй вход сдвигателя соединен с входной | информационной шиной, а третий вход соединен с третьим выходом блока формирования сигналов, четрертый выход которого соединен с выходной информационной шиной.

Источники информации, принятые во при экспертизе:

1.Авторское свидетепьство СССР № 336382, кп. G Об 1 5/02, 1972.

2.Авторское свидетельство СССР N9 296102, кл. G Об Р 5/02, 1969.

Авторы

Даты

1977-10-25—Публикация

1975-01-09—Подача