(54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЛОГИЧЕСКИХ

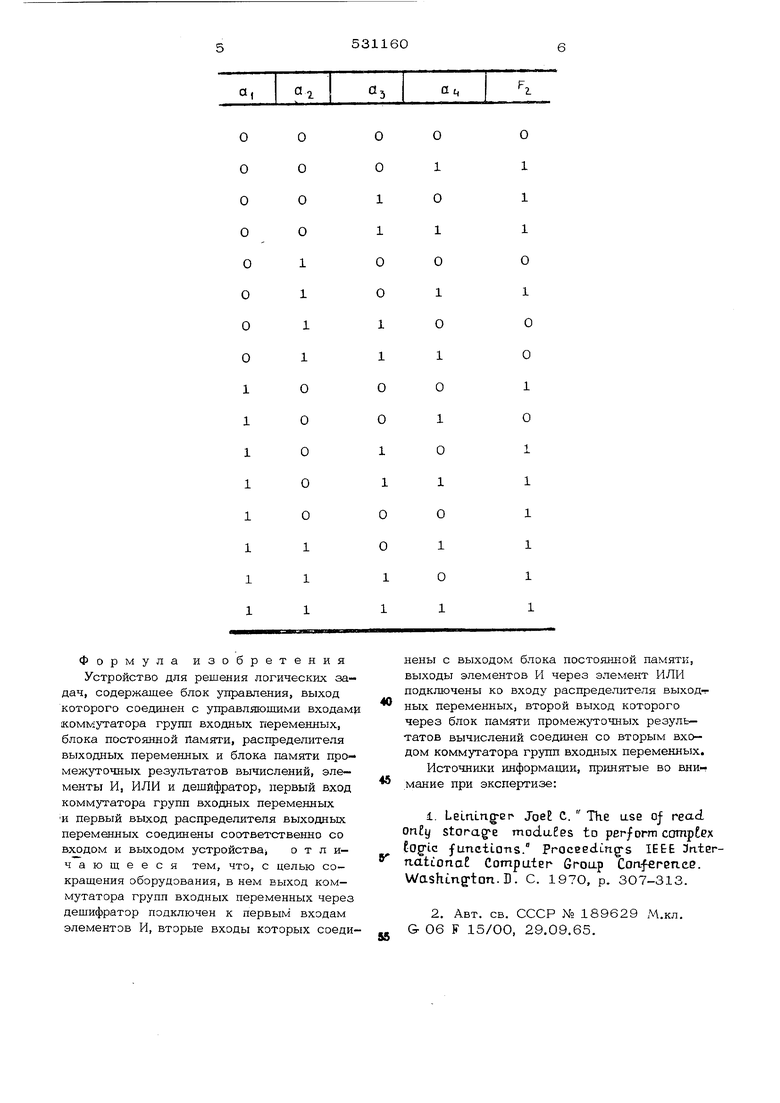

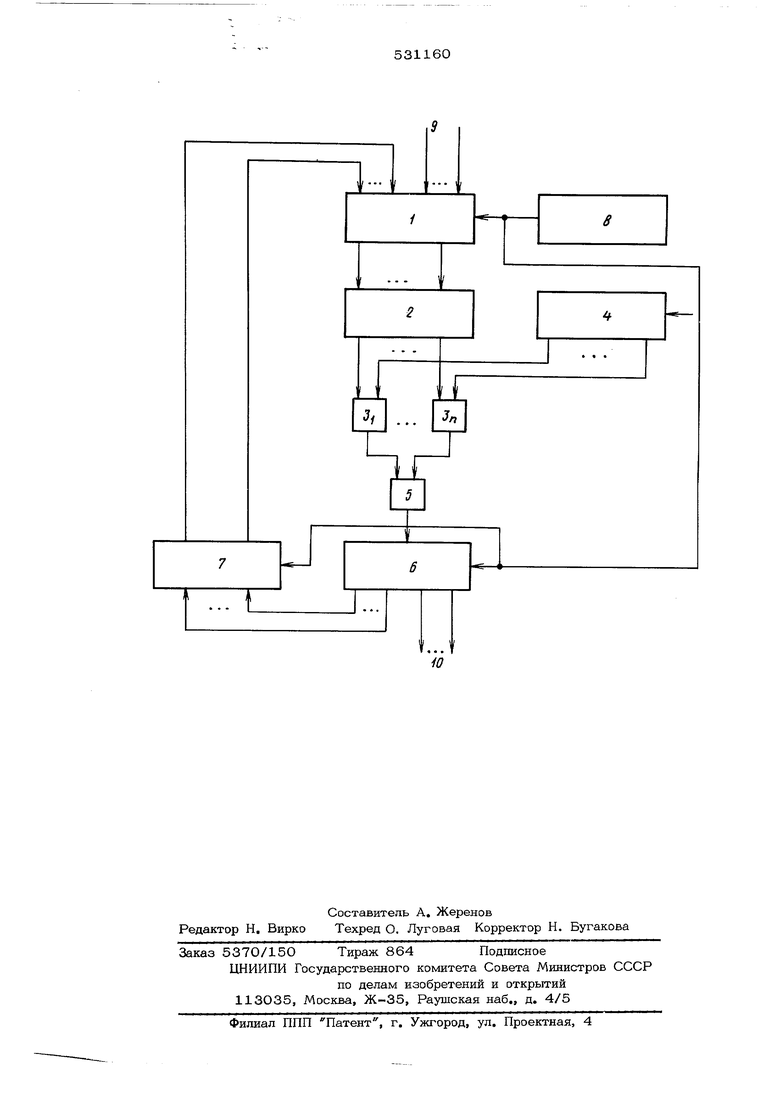

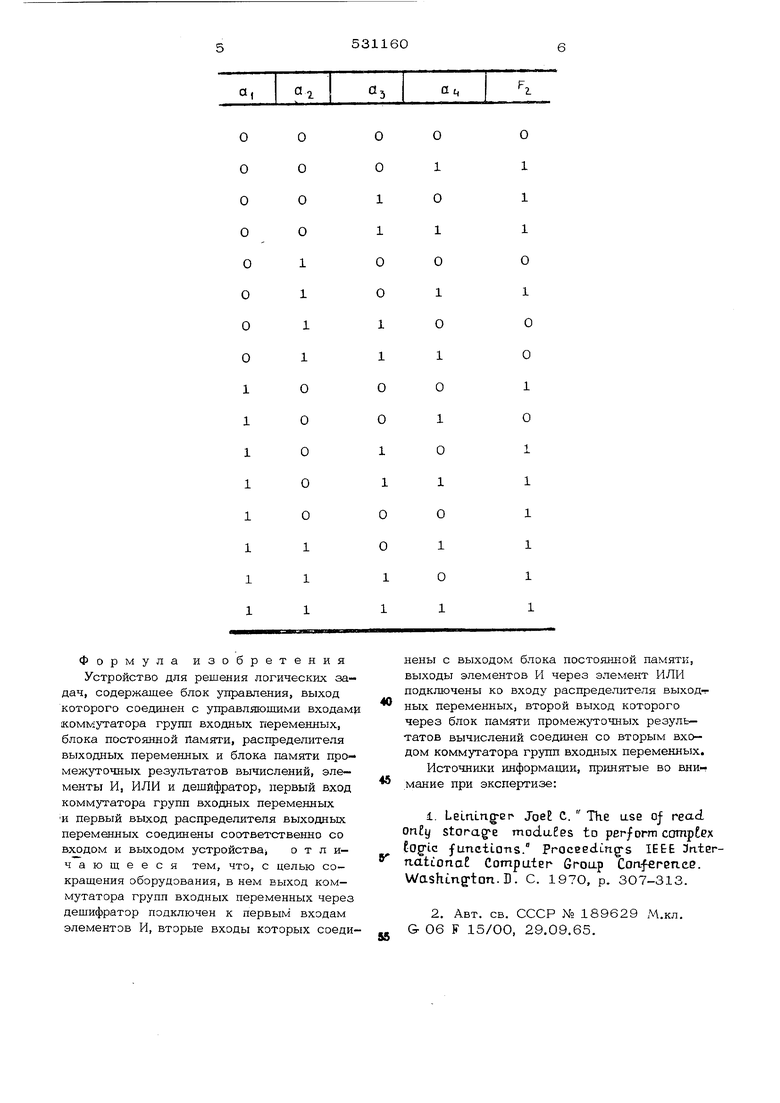

ЗАДАЧ вычисляет значения функции с пятью переменными ( a,«sss a)j одна из которых результат предыдущей операции. Применение групповой обработки информации в устройстве позволяет сократить программу вычисления по сравненшо с ин дивидуальной (по -битовой) обработкой двух позиционных сигналов, однако этот выигрыш существенно зависит от вида вичисляемых логических функций, что является недостатком указанного устройства. Так, например, вычисление функции/ F,a,3,.,() осуществляется за одну команду в то врем как для вычисления функции F2 a, + , (2.) требуется четыре команды. Целью изобретения является сокращение оборудования устройства Поставленная цель достигается тем, что в устройстве выход коммутатора групп вход ных nepoMeifflbix через дещифратор подключен к первым входам элементов И, вторые входы которых соединены с выходом блока постояршой памяти, выходы элементов И через элемент ИЛИ подключены ко входу распределителя выходньтх переменных, второй выход которого через блок памяти промежуточных результатов вычислений соединен со вторым входом коммутатора групп входных переменных. Это позволяет вычислять любую логичес кую функцшо от выбранной группы переменных за одну команду, в связи с чем эконо мится объем памяти программ, В блоке постоЕШНой памяти устройства записываются не команды программы, вычисденнЯг а заранее вычисленные значения логической функции при всех возможных наборах, входных переменных, составляющих группу, Известно, что любая логическая функция от П переменных определяется своими значениями на каждом из 2 наборов вход ных переменных. Поэтому для вычисления одной сколь угодно сложной функции, напри мер, переменных достаточно записать в 16--ТИ разрядном слове памяти 16 значений выходной функции, каждое из которых соответствует одному набору входных переменных, и иметь возможность выбора од- кого из записанных значений в зависимости от поданного входного набора. Таким образом, решение заданной системы булевых функций может быть сведено к выполнению последовательности однотипных операций над группами из нескольких переменных, причем каждая операция состоит из выбора слова памяти, в котором записаны значения вычисляемой функции от всех групп входных аргументов этой функции и выбора одного из разрядов этого слова в соответствии со значением входных переменных в группе. На чертеже представлена схема устройства. Оно содержит коммутатор 1 групп переменных, дешифратор 2, элементы И 3 - 3 р , блок 4 постоянной памяти, элемент ИЛИ 5, распределитель 6 выходных переменных, блок 7 памяти промежуточных результатов вычислений, блок 8 уп равдения, вход 9 и выход 10 устройства. Блок 8 управления формирует коды адресов, поступающие на входы коммутатора 1, распределителя 6 и блоков 4 и 7, В со-ответствии с указанным адресом на выходе коммутатора 1 формируется группа из П двоичных переменных. Указанная группа как 2 -разрядный двоичный код поступает на вход дешифратора 2, выход которого подключен ко входам элементов И, на вто- рые входы элементов И подается код слова из блока 4, где хранится значение булевых функций, С помощью элементов И и ИЛИ осуществляется выбор одного из двух разрядов кода слова памяти. Значение этого разряда через распределитель 6 выходных переменных (двухпозиционных сигналов) подается либо на выход 10 устройства, в блок 7 памяти промежуточных результатов вычислений, представляющий собой набор из триггеров. Выходы триггеров блока 7 подключены ко входу коммутатора 1 групп входных переменных таким образом, что промежуточные результаты могут быть использовалы наравне с двухпозиционными сигналами, подаваемыми на вход 9 устройства. Например, для вычисления за одну команду функции F 2 заданной либо выражением (2), либо таблицей, в одном 16-ти разрядном слове памяти записывается код, приведенный в столбце Р таблицы.

Формула изобретения Устройство для решения логических задач, содержащее блок управления, выход которого соединен с управляющими входам} коммутатора групп входных переменных, блока постоянной Памяти, распределителя выходных переменных и блока памяти промежуточных результатов вычислений, элементы И, ИЛИ и дешифратор, первый вход коммутатора групп входных переменных И первый выход распределителя выходных переменных соединены соответственно со входом и выходом устройства отличающееся тем, что, с целью сокращения оборудования, в нем выход коммутатора групп входных переменных через дешифратор подключен к первым входам элементов И, вторые входы которых соединены с выходом блока постоянной памяти, выходы элементов И через элемент ИЛИ подключены ко входу распределителя выход-г ных переменных, второй выход которого через блок памяти промеж точных результатов вычислений соединен со вторым входом коммутатора групп входных переменных. Источники информации, принятые во внимание при экспертизе:

1. LelnLng-er JoeE С. The use oj read, onlg storag e modaEes to perform complex functions.° proceed.Lngs IEEE 3n.terTtatLonaE Computter Groap Con.feren.ee. WashLUQfton.D. C. 197O, p. 3O7-313.

2. Авт. св. СССР № 189629 М.кл. G 06 F 15/00, 29.09.65.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации логических функций | 1981 |

|

SU1001080A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Устройство для вычисления булевых функций | 1980 |

|

SU955027A1 |

| Устройство для моделирования конечных автоматов | 1977 |

|

SU717775A1 |

| Устройство логической обработки | 1982 |

|

SU1124317A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Устройство для сравнения кодов | 1982 |

|

SU1027715A1 |

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

| Схема сравнения кодов | 1978 |

|

SU780003A1 |

| Устройство для реализации булевых функций | 1982 |

|

SU1032451A1 |

Авторы

Даты

1976-10-05—Публикация

1974-12-08—Подача