1

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных системах, а также в специализированных вычислительных комплексах для сдвига двоичных кодов и чисел.

Целью изобретения является расширение функциональных возможностей за счет определения левого значащего разряда и выполнения арифметических сдвигов.

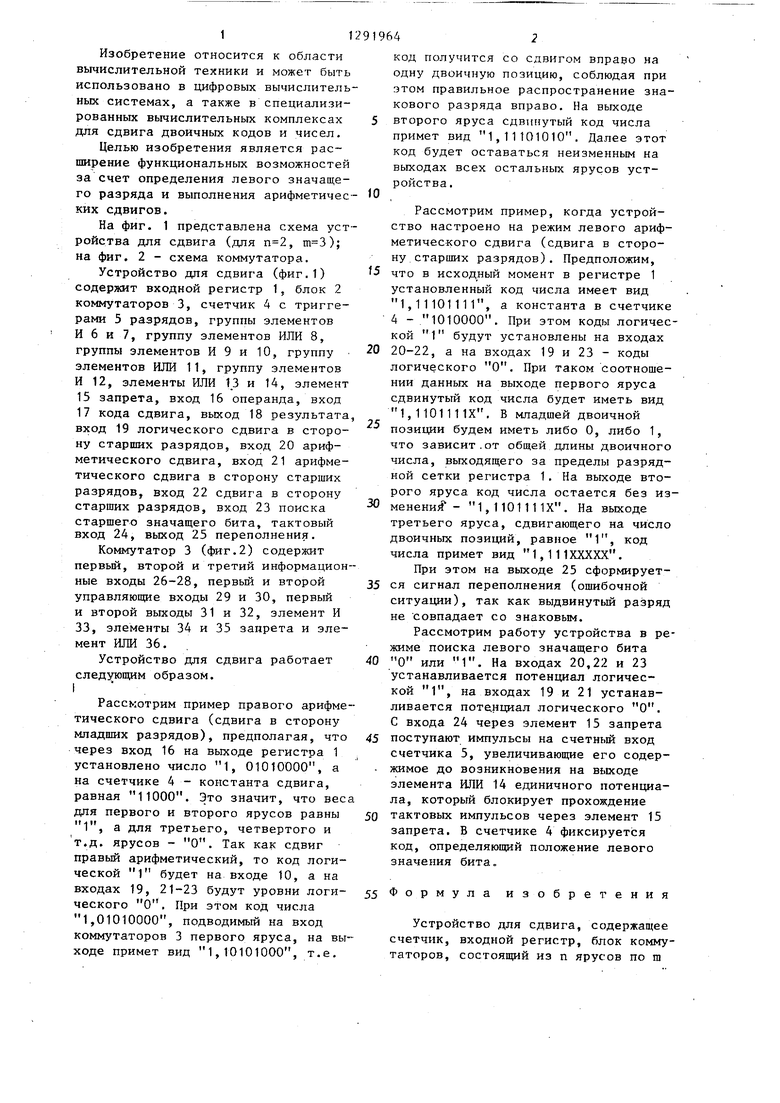

На фиг. 1 представлена схема устройства для сдвига (для , ); на фиг. 2 - схема коммутатора.

Устройство для сдвига (фиг,1) содержит входной регистр 1, блок 2 коммутаторов 3, счетчик 4 с триггерами 5 разрядов, группы элементов И 6 и 7, группу элементов ИЛИ 8, группы элементов И 9 и 10, группу элементов ИЛИ 11, группу элементов И 12, элементы ИЛИ и 14, элемент 15 запрета, вход 16 операнда, вход 17 кода сдвига, выход 18 результата вход 19 логического сдвига в сторону старших разрядов, вход 20 арифметического сдвига, вход 21 арифметического сдвига в сторону старших разрядов, вход 22 сдвига в сторону старших разрядов, вход 23 поиска старшего значащего бита, тактовый вход 24, выход 25 переполнения.

Коммутатор 3 (фиг.2) содержит первый, второй и третий информационные входы 26-28, первый и второй управляющие входы 29 и 30, первый и второй выходы 31 и 32, элемент И 33, элементы 34 и 35 запрета и элемент ИЛИ 36.

Устройство для сдвига работает следующим образом.

устанавливается потенциал логической 1, на входах 19 и 21 устанавливается потенциал логического О. С входа 24 через элемент 15 запрета 45 поступают импульсы на счетный вход

счетчика 5, увеличивающие его содер - жимое до возникновения на выходе элемента ИЛИ 14 единичного потенциа

Расскотрим пример правого арифметического сдвига (сдвига в сторону младших разрядов), предполагая, что через вход 16 на выходе регистра 1 установлено число 1, 01010000, а на счетчике 4 - константа сдвига, равная 11000. Это значит, что веса для первого и второго ярусов равны 50 1, а для третьего, четвертого и т.д. ярусов - О. Так как сдвиг правый арифметический, то код логической 1 будет на входе 10, а на

входах 19, 21-23 будут уровни логи- Формула изобретени ческого О. При этом код числа

ла, который блокирует прохождение тактовых импульсов через элемент 15 запрета. В счетчике 4 фиксируется код, определяющий положение левого значения бита,,

1,01010000, подводимый на вход коммутаторов 3 первого яруса, на выходе примет вид 1,10101000, т.е.

код получится со сдвигом вправо на одну двоичную позицию, соблюдая при этом правильное распространение знакового разряда вправо. На выходе второго яруса сдвинутый код числа примет вид 1,11101010. Далее этот код будет оставаться неизменным на выходах всех остальных ярусов устройства.

Рассмотрим пример, когда устройство настроено на режим левого арифметического сдвига (сдвига в сторону старших разрядов). Предположим, что в исходный момент в регистре 1 установленный код числа имеет вид 1,11101111, а константа в счетчике 4 - 1010000. При этом коды логической 1 будут установлены на входах

20-22, а на входах 19 и 23 - коды логического О. При таком соотношении данных на выходе первого яруса сдвинутый код числа будет иметь вид 1,1101111X. В младшей двоичной

позиции будем иметь либо О, либо 1, что зависит.от общей длины двоичного числа, выходящего за пределы разрядной сетки регистра 1. На выходе второго яруса код числа остается без изменений - 1,110111IX. На выходе третьего яруса, сдвигающего на число двоичных позигщк, равное 1, код числа примет вид 1,111ХХХХХ.

При этом на выходе 25 сформируется сигнал переполнения (ошибочной ситуации), так как выдвинутЕ ш разряд не совпадает со знаковым.

Рассмотрим работу устройства в режиме поиска левого значащего бита

О или 1. На входах 20,22 и 23

устанавливается потенциал логической 1, на входах 19 и 21 устанавливается потенциал логического О. С входа 24 через элемент 15 запрета поступают импульсы на счетный вход

счетчика 5, увеличивающие его содер- жимое до возникновения на выходе элемента ИЛИ 14 единичного потенциа

ла, который блокирует прохождение тактовых импульсов через элемент 15 запрета. В счетчике 4 фиксируется код, определяющий положение левого значения бита,,

Устройство для сдвига, содержащее счетчик, входной регистр, блок коммутаторов, состоящий из п ярусов по га

3

коммутаторов в каждом, причем первы и второй информационные входы j-ro коммутатора первого яруса соединены соответственно с прямыми выходами j го и (j+1)-ro разрядов входного ре- гистра, вход которого соединен с входом операнда устройства, первый выход j-ro коммутатора i-ro яруса (i 1-п, j - 1-m) соединен с первы информационным входом j-ro коммутат ра и вторым информационным входом (j- 2)-го коммутатора ( яруса, первый управляющий вход коммутаторов каждого яруса соединен с прямым выходом соответствующего разряд счетчика, входы разрядов которого являются входом кода сдвига устройства, выход результата которого соединен с первыми выходами коммутаторов последнего яруса, отличающееся тем, что, с целью расширения функциональных возможностей за счет определения старшего значащего разряда и выполнения арифметических сдвигов, оно содержит пять групп элементов И, две группы элеметов ИЛИ, два элемента ИЛИ и элемент запрета, причем третий информационн вход j-ro коммутатора первого яруса соединен с прямым выходом (j-1)-ro разряда входного регистра, первьй выход j-ro коммутатора i-ro яруса соединен с третьим информационным входом (J+2 )-го коммутатора (i+1)- го яруса, вторые управляющие входы коммутаторов всех ярусов соединены с входом сдвига в сторону старших разрядов устройства, первые входы элементов И первой и второй групп соединены соответственно с входом арифметического сдвига и входом логического сдвига в сторону старших разрядов устройства, вторые входы элементов И первой группы соединены с первыми информационными входами первых коммутаторов соответствующих ярусов, второй вход i-ro элемента И второй группы соединен.с первым информационным входом (2 4-1)-го коммутатора i-ro яруса, выходы элементов И первой и второй групп соединены соответственно с первым и

15

0

5

. 5 0

30

35

0

вторым входами соответствующих элементов ИЛИ первой группы, выход 1- го элемента ИЛИ которой соединен с третьим информационным входом первого коммутатора i-ro яруса и с вторыми информационными входами коммутаторов с первого по ( )-й i-ro яруса, входы первого элемента и третьей группы соединены соответствен- но с инверсными выходами первого и второго разрядов входного регистра, входы первого элемента И четвертой группы соединены соответственно с прямыми выходами первого и второго разрядов входного регистра, входы i-ro, кроме первого, элемента И третьей группы соединены соответственно с вторыми выходами коммутаторов с первого по (2 +1)-й (i-l)-rp яруса, входы i-ro, кроме первого, элемента И четвертой группы соединены соответственно с первыми выходами коммутаторов с первого по (2 + +1)-й (i-l)-ro яруса, выходы элементов И третьей и четвертой групп соединены соответственно с первым и вторым входами соответствующих элементов ИЛИ второй группы, инверсные выходы которых соединены соответственно с первыми входами элементов И пятой группы, вторые входы которых соединены с прямыми выходами соответствующих разрядов счетчика, выход первого элемента ИЛИ соединен с третьими входами элементов И пятой группы, выходы которых соединены соответственно с входами второго элемента ИЛИ, выход которого является выходом переполнения устройства и соединен с управляющим входом элемента запрета, выход которого соединен со счетным входом счетчика, тактовый вход устройства соединен с первым информационным входом элемен- 5 та запрета, второй информационный вход которого соединен с первым входом первого элемента ИЛИ и является входом поиска старшего знача- . щего бита устройства,, вход арифметического сдвига в сторону старших разрядов которого соединен с вторым входом первого элемента ИЛИ.

0

п

2 иг2 (

w

28

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1984 |

|

SU1256016A1 |

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для потенцирования логарифмов п-разрядных двоичных чисел | 1977 |

|

SU765801A1 |

| Устройство для умножения чисел с фиксированной запятой | 1989 |

|

SU1758644A1 |

.Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных системах, а также специализированных вычислительных комплексах для сдвига двоичных кодов .и чисел. Целью изобретения является расширение функциональных возможностей за счет определения старшего значащего разряда и выполнения арифмети- ческих сдвигов. Поставленная цель достигается тем, что устройство для сдвига, содержащее входной регистр 1, блок 2 коммутаторов 3 и счетчик 4, содержит пять групп 6,7,9,10,12 элементов И, две группы элементов ИЛИ 8,11, два элемента ИЛИ 13, 14 и элемент запрета 15 с соответствующими связями. 2 ил. (Л ю о О) fe/

| Устройство для сдвига данных | 1983 |

|

SU1140113A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство сдвига информации | 1976 |

|

SU602939A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-23—Публикация

1985-09-16—Подача