Изобретение относится к вычислительной технике, в частности к устройствам памяти на полупроводниковых приборах.

Цель изобретения - повышение надежности устройства.

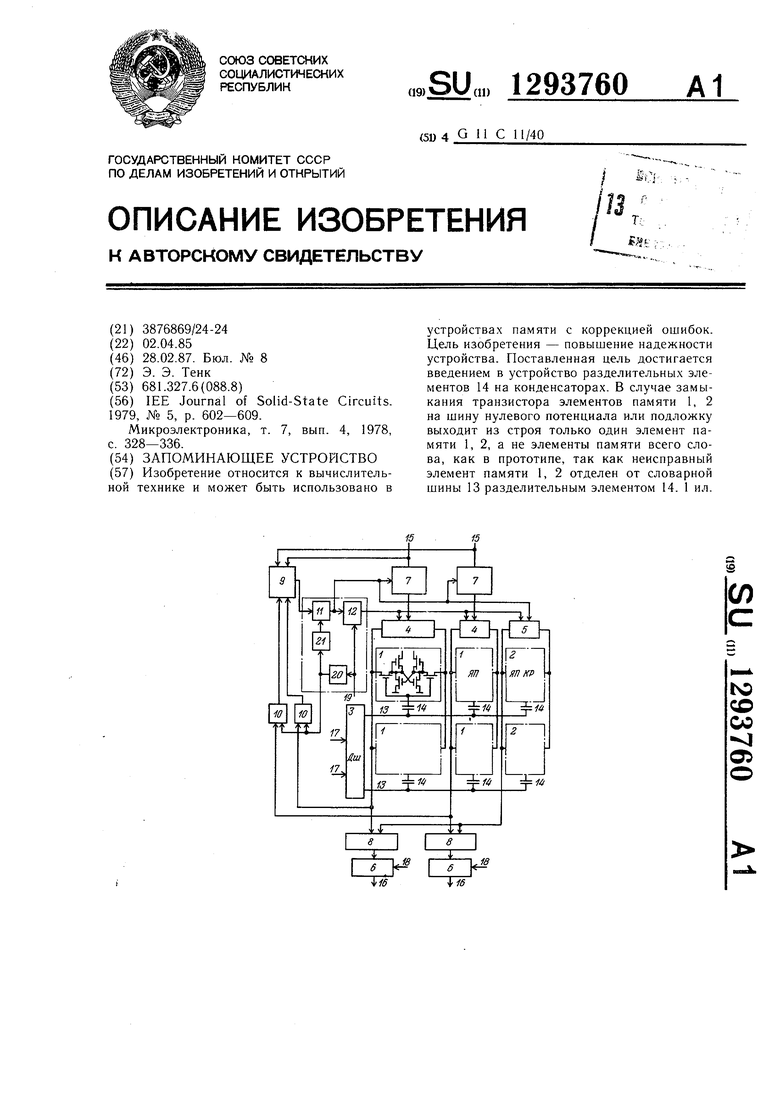

На чертеже приведена структурная схема предлагаемого запоминающего устройства .

Устройство содержит элементы 1 памяти информационных, элементы 2 памяти контрольных разрядов, дешифратор 3, блоки 4, 5 записи информационных и контрольного разрядов, блоки 6 считывания информационных разрядов, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ первой 7 и второй 8 группы, блок 9 сравнения, группу элементов И 10, элемент И 11, элемент ИЛИ 12, словарные шины 13, разделительные элементы на конденсаторах 14, информационные входы 15 и выходы 16 устройства, адресные входы 17, входы 18 разрешения считывания,вход 19 разрешения записи, первый 20 и второй 21 элементы задержки.

Устройство работает следуюшим образом.

В режиме записи информация с входов 15 через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ первой 7 группы в прямом коде поступает на входы блоков 4 записи и далее на входы- выходы элементов 1 памяти. Одновременно дешифратор 3 в соответствии с кодом адреса на входах 17 возбуждает одну из словарных шин 13, отпирая адресные транзисторы элементов 1 памяти, подключенных к словарной шине 13 через конденсаторы 14. В результате информация с входов 15 записывается в элементы 1 памяти. Одновременно в элемент 2 памяти через блок 5 записи записывается «О. Для обнаружения возможной ошибки из-за неисправности элемента 1 памяти после записи информации по сигналу с выхода первого элемента 20 задержки происходит контрольное считывание по этому же адресу и сравнение в блоке 9 сравнения считанного слова со словом, имеюшимся на входах 15. На выходе блока 9 формируется сигнал ошибки записи, который поступает через элемент И 11 на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой 7 группы, разрешая инвертирование содержимого всего записываемого слова и перезапись его в таком виде по тому же адресу. При этом в элемент 2 памяти записывается «1. Сигнал, тактируюший работу блоков 4 и 5 записи, формируется на выходе элемента ИЛИ 12.

В режиме считывания информация с элементов 1 памяти поступает на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй 8 группы, на вторые входы которых из элемента 2 памяти поступает сигнал, который при наличии в слове дефектного элемента 1 памяти инвертирует считанную информацию и тем самым исправляет сигнал с дефектного

5

5 0

элемента 1 памяти, так как он не инвертируется при записи из-за неисправности элемента 1 памяти.

При наличии в элементе 1 памяти дефекта, приводяшего к замыканию адресного входа элемента 1 памяти на шину нулевого потенциала или подложку, выходит из строя только один элемент 1 памяти. Остальные элементы 1 и 2 памяти, подключенные к данной словарной шине 13, остаются работоспособными. Это достигается наличием в элементах памяти 1 и 2 разделительных элементов 14.

Формула изобретения

Запоминающее устройство, содержащее элементы памяти информационных и контрольного разрядов, дешифратор, блоки записи информационных и контрольного раз рядов, блоки считывания информационных разрядов, блок сравнения, первую и вторую группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу элементов И, элемент ИЛИ, элемент И и первый и второй элементы задержки, причем числовые входы-выходы элементов памяти информационных и контрольного разрядов соединены с выходами соответствующих блоков записи, первые входы которых соединены с выходом элемента ИЛИ, вторые входы блоков записи информационных разрядов соединены с выходами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, первые входы которых соединены с выходом элемента И, первым входом элемента ИЛИ и вторы.м входом блока записи контрольного разряда, второй вход элемента ИЛИ соединен с входом первого элемента задержки и является входом разрешения записи устройства, выход первого элемента задержки соединен с первыми входами элементов И группы и с входом второго элемента задержки, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом блока сравнения, первые входы блоков записи информационных разрядов соединены с вторыми входами соответствующих элементов И группы и с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, вторые входы которых соединены с первым входом блока записи контрольного разряда, а выходы - с первыми входами соответствующих блоков считывания информационных разрядов, вторые входы которых являются входом разрешения считывания устройства, а выходы - информационными выходами устройства, выходы эле- . ментов И группы соединены с вход.ами нер5 вой группы блока.сравнения, входы второй группы которого соединены с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

5

0

1293760

34

первой группы и являются информационны-торых выполнен на конденсаторе, причем

ми входами устройства, входы дешифраторапервые выводы конденсаторов каждой групявляются адресными входами устройства,пы соединены с соответствующими выходами

отличающееся тем, что, с целью повышениядешифратора, а вторые - с адресными вхонадежности устройства, оно содержит труп-дами соответствующих элементов памяти

пы разделительных элементов, каждый из ко-.информационных и контрольного разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1986 |

|

SU1377913A1 |

| Полупроводниковое оперативное запоминающее устройство | 1985 |

|

SU1295446A1 |

| Оперативное запоминающее устройство | 1987 |

|

SU1425782A1 |

| Оперативное запоминающее устройство | 1987 |

|

SU1429167A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1986 |

|

SU1439679A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| Резервированное запоминающее устройство | 1986 |

|

SU1417041A1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1278984A1 |

| Настраиваемое логическое устройство | 1990 |

|

SU1784964A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах памяти с коррекцией ошибок. Цель изобретения - повышение надежности устройства. Поставленная цель достигается введением в устройство разделительных элементов 14 на конденсаторах. В случае замыкания транзистора элементов памяти 1, 2 на шину нулевого потенциала или подложку выходит из строя только один элемент памяти 1, 2, а не элементы памяти всего слова, как в прототипе, так как неисправный элемент памяти 1, 2 отделен от словарной шины 13 разделительным элементом 14. 1 ил. (Л ND СО СО о: f3

| IEE Journal of Solid-State Circuits | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| АППАРАТ ДЛЯ РАЗРЕЗАНИЯ ПЕРЕДВИГАЮЩЕЙСЯ НА ПОДВИЖНОМ СТОЛЕ ТОРФЯНОЙ ПОЛОСЫ ПРИ ПОМОЩИ НОЖЕЙ, УКРЕПЛЕННЫХ НА ПОВЕРХНОСТИ БАРАБАНА | 1922 |

|

SU602A1 |

| Микроэлектроника, т | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

Авторы

Даты

1987-02-28—Публикация

1985-04-02—Подача