-У

.СО

со

САЭ

Изобретение относится к вычислительной технике, в частности к полупроводниковым интегральным устройствам памяти.

Целью изобретения является упрощение устройства за счет уменьшения площади интегральной микросхемы па- мыти, занятой разделительными элементами.

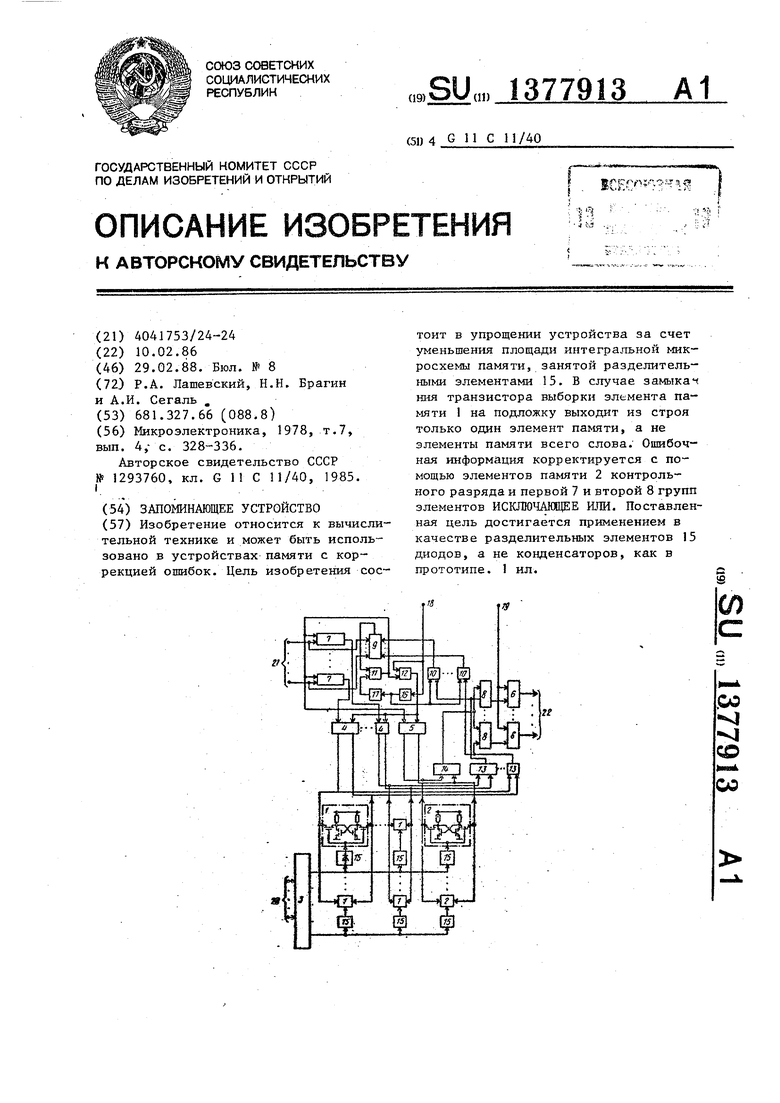

На чертеже представлена структзф- ная схема запоминающего устройства

Устройство содержит элементы 1 памяти информационных разрядов, элементы 2 памяти контрольного разряда, дешифратор 3, блоки записи информационных 4 и контрольного 5 разрядов, блоки 6 считывания информационных разрядов, элементы ИСКЛЮЧАЩЕЕ ИЛИ первой 7 и второй 8 групп, блок 9 сравнения, группу элементов И 10, элемент И 11, элемент ИЛИ 12, усилители считывания информационных 13 и контрольного 14 разрядов,, раздели-, тельные элементы 15 на диодах, первый 16 и второй 17 элементы задержки, вход 18 разрешения записи, вход 19 разрешения считывания, адресные входы 20, информационные входы 21 и 22 устройства.

Устройство работает следующим образо-м.

В режиме записи (единичный сигнал на входе 18) с входов 21 через элементы 7 информация в прямом коде поступает на входы блоков 4 записи, с выходов которых она поступает на числовые входы-выходы элементов 1 памяти информационных разрядов.. Одновременно дешифратор 3 в соответствии с кодом, адреса: на входах 20 возбуждает адресных шин, отпирая адресные транзисторы в элементе 1 памяти информационных разрядов и элементе 2 памяти контрольного разряда, подключенных к соответствующему выходу дешифратора 3 через разделительные элементы 15.В результате , информация, установленная на входах 21, записывается в соответствукндие элементы 1 памяти информационных разрядов. Одновременно в элемент 2 памяти контрольного разряда через блок 5 записи контрольного разряда записывается о, так как отсутствует сигнал на выходе элемента И 11. Для обнаружения возможной ошибки из-за неисправности одного из элементов памяти информационного разряда после записи информац:ии по сигналу- с выхода первого элемента 16 задержки происходит

контрольное считывание- по этому же адресу и сравнение в блоке 9 сравнения считываемой информации, поступающей с выходов соответствующих усилителей 13 считывания .через элементы И группы 10 с имеющейся на информационных входах 21 устройства. Если ошибка есть, то на выходе блока 9 сравнения формируется сигнал ошибки записи, который поступает

через элемент И 11 на соответствующие входы элементов 7, разрешая инвертирование- в последних содержимого всего записывае мого слова и перезапись его в таком виде-по данному адресу. При этом в элемент 2 памяти контрольного разряда, подключенный к данному выходу дешифратора 3 через разделительный элемент 15, записывается единичный символ, поступаюцщй с выхода элемента И 11

через блок 5 записи контрольного разряда. Сигнал, тактирующий работу блоков записи информационных 4 и контрольного 5.разрядов, формирует-

ся на выкоде элемента ИЛИ 12, на

входы которого подаются сигналь Разрешение записи с входа 18 И с выхода второго элемента 17 задержки через элемент И 11.

В режиме считывания, (единичный сигнал на входе 19) дешифратор 3, как и в режиме записи, возбуждает одну из адресных шин, отпирая адресные транзисторы в cooтвeтcтвyюшJ x

элементах 1 памяти информационных разрядов и элементе 2 памяти контрольного разряда. Считываемая из элементов 1 памяти информация через соответствующие усилите1ш 13 считы-.:

вания поступает на входы элементов 8, на другие входа. которых- с элемента 2 памяти контрольного разряда через усилитель 14 считывания контрольного разряда поступает сигнал, который

при наличии в слове дефектного эле- мента памяти инвертирует считываемую информацию (на элементе 8), и, таким образом, исправляет сигнал-, считанный из дефектного элемента памяти, поскольку он не инвертируется при повторной записи из-за неисправности элемента памяти (информация в дефектном элементе памяти не изменена). Информация с исправных элементов 1

памяти остается неизменной, так как инвертируется дважды:, при повторной записи и при считывании. С выходов 8 элементов считываемая информация поступает на входы блоков 6 считывания и на информационные выходы 22 устройства.

Функции, выполняемые разделительным элементом 15 на диоде.

Если выход дешифратора 3 не выбран, то он имеет низкий потенциал. При этом е1-1кости затворов адресных транзисторов элементов памяти разря жены обратным током диода 15..Параметры диода 15 выбираются такими, чтобы время разряда емкостей затворов адресных транзисторов элементов 1 памяти его обратным током было достаточно малым (десятки не).

При записи или считывании на выбранном выходе дешифратора 3 устанавливается высокий потенциал. Емкости затворов адресных транзисторов элементов 1 памяти заряжаются через открытый диод 15, подготавливая элемент 1 памяти для записи клк считывания.

i

При пробое .подзатворного окисла

адресного транзистора в области зэтвор-сток и наличии на соответствующем числовом входе-гвыход,е высокого, напряжения при отсутствии диода 15 возможно возбуждение невыбранной строки, что приведет к сбою в работе устройства. Наличие диода 15 -позволяет ограничить ток, связа.н- ный с таким замыканием, и сохранить низкий потенциал на невыбранной строке.

Формула изобретения

Запоминающее устройство, содержащее элементы памяти информационных и контрольного разрядов, дешиф- .ратор, блоки записи информационных и контрольного разрядов, усилители считывания информационных и контрольного разрядов, .блоки считывания информационных разрядов, блок сравнения, первую и вторую группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу элементов И, элемент ШШ, элемент И, первый и второй элементы задержки и группы разделительных элементов, причем числовые входы-выходы элементов памяти информационных и контроль0

5

0

5

0

5

0

5

0

5

ного разрядов соединены с выходами блоков записи соответственно информационных и контрольного разрядов, первые входа блоков записи информационных и контрольного разрядов соеди- нень с выходом .элемента ИЛИ, вторые входы блоков записи информационных разрядов соединены с выходами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, первые входы которых соединены с выходом элемента И, пер вым входом элемента ИЛИ и вторум входом блока записи контрольного разряда, второй вход элемента ИЛИ соединен с выходом первого элемента задержки- и является входом разрешения записи устройства, выход первого элемента задержки соединен с первыми входами элементов И группы и с входом второго элемента задержки, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом блока сравнения , выходы блоков записи информационных и контрольного разрядов соединены с входами усилителей считываний соответственно информационнь1х и контрольного разрядов, выходы усилителей считывания информационных разрядов соединены с вторыми входами соответствующих элементов И группы и с первыми входами соответствующ1 х ; элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, вторые входы которых соединены с выходом усилителя считьшания контрольного разряда, а выходы - с первыми входами соответствутощих бло- :ков считывания информационкьк разрядов, вторые входы которых- являются входом разрешения считывания устройства, а выходы - информационными выходами устройства выходы элементов И группы соединены с входами первой группы блока сравнения., входы второй группы которого соединены с вторыми входами элементов ИСКЛЮЧА аЦЕЕ ИЛИ первой группы и являются информационными входами устройства, адресные входы элементов памяти информа- 1ЩОННЫХ и контрольного разрядов соединены с первыми выводами разделительных элементов групп, вторые выводы разделительных элементов каждой группы соединены с сответствующими выходами дешифратора, входы которого Являются адресными входами устройства, о т л и чаю щ в е с я тем, что, с целью упрощения устройства.

51377913

каждый разделительный элемент выпол- ляется первым, а анод - вторым выво- нен в виде диода, катод которого яв- дами разделительного элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1293760A1 |

| Полупроводниковое оперативное запоминающее устройство | 1985 |

|

SU1295446A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1986 |

|

SU1439679A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| Оперативное запоминающее устройство | 1987 |

|

SU1425782A1 |

| Оперативное запоминающее устройство | 1987 |

|

SU1429167A1 |

| Запоминающее устройство | 1986 |

|

SU1361636A1 |

| Запоминающее устройство | 1983 |

|

SU1112412A1 |

| Резервированное запоминающее устройство | 1986 |

|

SU1417041A1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1278984A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах памяти с коррекцией ошибок. Цель изобретения состоит в упрощении устройства за счет уменьшения площади интегральной микросхемы памяти, занятой разделительными элементами 15. Б случае замыкам кия транзистора выборки элемента памяти 1 на подложку выходит из строя только один элемент памяти, а не элементы памяти всего слова. Ошибочная информация корректируется с помощью элементов памяти 2 контрольного разряда и первой 7 и второй 8 групп элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Поставленная цель достигается применением в качестве разделительных элементов 15 диодов, а не конденсаторов, как в прототипе. 1 ил. Ш

| Микроэлектроника, 1978, т.7, вып | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

| Запоминающее устройство | 1985 |

|

SU1293760A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-02-28—Публикация

1986-02-10—Подача