гз 2it

16

L.0-1

(Л

с

22

}-L@-

4

ю

СП

00 ts5

случае неисправности элемента памяти 3 контрольного разряда по сигналу с элемента ИЛИ 18 производится повторная запись гнформации в инверсном виде в Элементы памяти 2 информационных разрядов. При считьтании эта информация вновь инвертируется, что позволяет устройству нормально работать при неисправности элемента памяти 3 контрольного разряда. з.п,

ф-лы; I ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковое оперативное запоминающее устройство | 1985 |

|

SU1295446A1 |

| Запоминающее устройство | 1985 |

|

SU1293760A1 |

| Запоминающее устройство | 1986 |

|

SU1377913A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1986 |

|

SU1439679A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Запоминающее устройство с резервированием | 1986 |

|

SU1417042A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1100638A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1188784A1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1278984A1 |

Изобретение относится к вычислительной технике, в частности к интегральным полупроводниковым запоминающим устройствам. Цель изобретения - повьшение надежности устройстаа.Поставленная цель достигается тем, что устройство содержит второй элемент ИЛИ 18 с соответствующими связями. В

1

Изобретение относится к вычислительной технике, в частности к интегральным полупроводниковым запоминающим устройствам (ЗУ).

Цель изобретения - повышение на- дежности устройства.

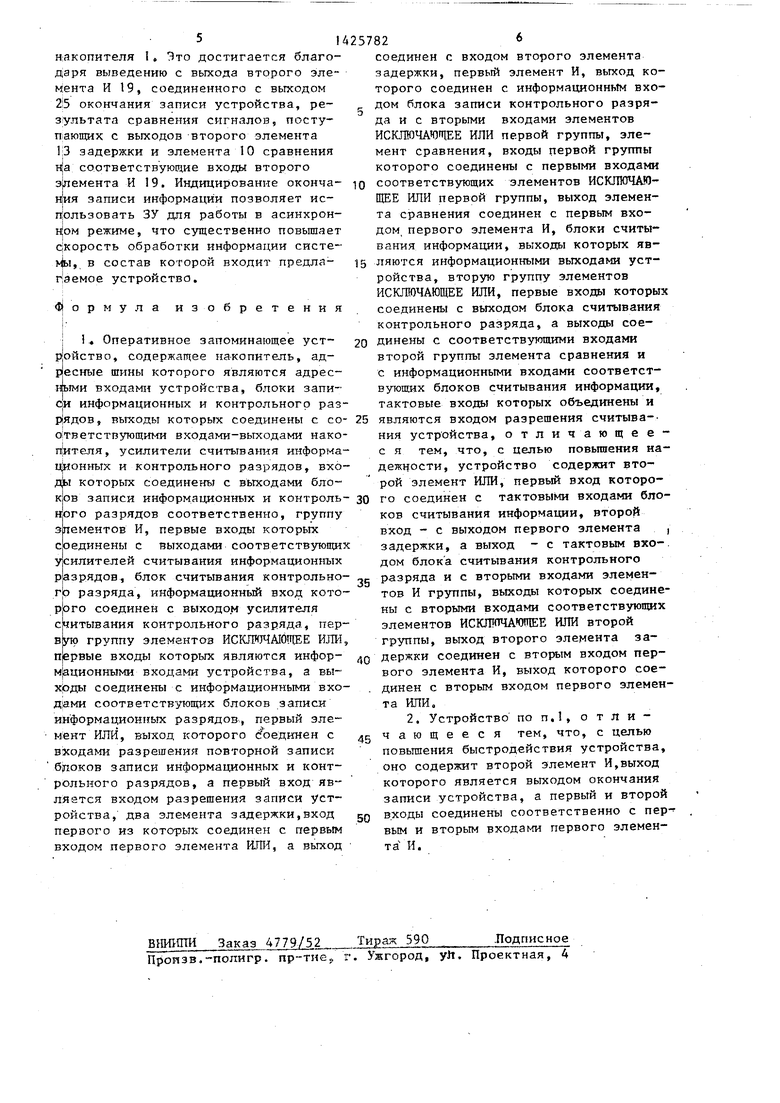

. На чертеже представлена структур- най схема оперативного ЧУ.

Оперативное ЗУ содержит накопитель 1, элементы 2 памяти информаци- онных разрядов, элементы 3 памяти контрольного разряда, блоки 4 записи информационных раз-рядов, блок 5 записи контрольного разряда, первый элемент ИЛИ 6, усилители 7 считывания информационных разрядов, усилитель 8 считывания контрольного разряда, элементы ИСКЛЮЧАЮЩЕЕ ШТИ 9 первой группы, элемент 10 сравнения, первый элемент И 11, первый 12 и второй 13 эле- менты задержки, группы элементов И 14 блок 15 считывания контрольного разряда, элементы ИСКГООЧАЮЩЕЕ ШШ 16 второй группы, блоки 17 считывания информационных разрядов, второй эле- мент ИЛИ 18, второй элемент И 19, адресные входы 20 устройства, информационные входы 21 устройства, информационные выходы 22 устройства,вход 23 разрешения записи устройства, вход 24 разрешения считывания устройства, выход 25 окончания записи устройства.

Устройство работает следующим образом.

В режиме записи информация с вхо- дов 21 устройства через элементы ИСКЛЮ.ЧАЮЩЕЕ ШШ 9 в прямом коде поступает на информационные входы блоков 4 записи информационных разрядов, с выходов которых она поступает на инфор- мационные входы-выходы элементов 2 памяти информационных разрядов нако- пителя 1i :В соответствии с кодом адреса, установленным на адресных входах 20 устройства, возбуждается одна из адресньпс шин в накопителе 1, делая возможным запись информации, установленной на входах 21, в соответствующие элементы 2 памяти информационных разрядов накопителя 1. Одновременно с записью информации в информационные разряды в элемент 3 памяти контрольного разряда накопителя 1, подключенный к возбужденной/в соответствии с кодом адреса на входах 20 адресной шине, записывается логический О, так как сигнал разрешения повторной записи на выходе первого элемента И И отсутствует. Для обнаружения возможной ошибки из-за неисправности элемента 2 памяти информационного разряда после записи информации по сигналу с вьпсода первого элемента 12 эадержки, поступающему через второй элемент ИЛИ 18 на вход управления блока 15 считывания контрольного разряда и вторые входы элементов И 14 группы, происходит контрольное считывание по этому же адресу.

Считанная информация через элементы И 14 группы поступает на вторые входы соответствующих элементов .ИСКЛЮЧАЩЕЕ ИЛИ 16 второй группы. На первые входы элементов ИСКЛЮЧАКЯЦЕЕ ИЛИ 16 второй группы с входа-выхо51а элемента 3 памяти контрольного разряда накопителя 1 через усилитель 8 считывания контрольного разряда в блок 15 считывания контрольного разряда поступает сигнал логического О. Логические сигналы, установленные на информационных входах элемен- .тов ИСКЛЮЧАЮЩЕЕ ИЛИ 16 второй группы, без инвертирования поступают на входы второй группы элемента 10 сравнения, в котором сравниваттся с имеющейся на информационных входах 21

устройства записываемой в соответствующие элементы 2 памяти информационных разрядов информацией, В случае обнаружения ошибки на выходе элемента 10 сравнения формируется сигнал ошибки записи, который поступает через первый элемент И 11 на вторые входы элементов ИСКШОЧАЮЩЕЕ ИЛИ 9 первой группы, разрешая инвертирова- ние в последних содержимого всего записываемого слова и перезапись его в таком биде по данному адресу. При этом в соответствующий элемент 3 памяти контрольного разряда записьгаает- ся сигнал логической 1, поступаю- щий с выхода первого элемента 11 и через блок 5 записи контрольного разряда. Сигнал, синхронизирующий работу

блоков 4 записи информационных разря- 20 та 3 памяти контрольного разряда в

ней всегда хранится логический О. В этом случае режим записи информации не отличается от описанного,При считывании, если элементы 2 памяти 25 информационных разрядов исправны,от каз ячейки памяти контрольного разр да не Приводит к искажению записан- ной информации. Если в результате о каза элемента 3 памяти контрольного 30 разряда в ней всегда хранится логическая 1, то в .режиме записи при промежуточном считывании информации из элементов 2 памяти информационных разрядов с целью обнаружения 25 ощибки записи считьгааемая информаци .инвертируется в элементах ИСКЛЮЧАЮ- :ЩЕЕ ИЛИ 16 второй группы, В элемент I10 сравнения вырабатывается сигнал ошибки и записываемая информация ин 4о вертируется в элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 9 первой группы, а в элемент 3 памяти контрольного разряда записыв ется сигнал ощибки (логическая 1 При считывании по сигналу разрешени 45 считьгеания информация из элементов 2 памяти информационных разрядов ин вертируется второй раз в элементах ИСКЛЮЧАКЯЦЕЕ ИЖ 16 второй группы и

дов и блока 5 записи контрольного разряда, формируется на выходе первого элемента ИЛИ 6, на первый и второй входы которого подаются сигналы разрешения записи с входа 23 устройства и разрешения повторной записи с выхода второго элемента 13 задержки через первый элемент И 11,

В режиме считывания, как и в режиме записи, в соответствии с кодом адреса, установленным на адресных входах-20 устройства, возбуждается одна из адресных шин накопителя 1, делая возможным считывание информации из соответствующих элементов па- яти. Считываемая из элементов 2 памяти информационных разрядов информация через соответствующие элементы И 14 группы поступает на в-юрые входы соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 16 второй группы. На первые входы последних из элемента 3 памяти контрольного разряда накогм- теля I через блок 15 считьгеания конт- рольн.ого разряда поступает сигнал, который при наличии в слове дефектного элемента инвертирует в элементах 16 считываемую информацию. Таким образом, исправляется сигнал, считанный из дефектного элемента 2 памяти информационного разряда, поскольку он не инвертируется при повторной записи из-за неисправности элемента 2 памяти информационного разряда (информация в дефектном элементе неиз-.. менна), а инвертирование при считывании исправляет сигнал дефектной позиции. Информация из исправных эле- ментов 2 памяти информационных размент

рядов остается неизменной, так как инвертируется дважды - при повторной записи и при считьгеании. С выходов элементов 16 считываемая информация поступает на первые входы блоков 17 считывания информационных разрядов и далее - на информационные выходы 22 устройства.. Управление в режиме считывания производится сигналом, подаваемым с входа 24 разрешения считывания устройства на вторые входы блоков 17 считывания информационных разрядов, а также через второй элеИЛИ 18 - на вход управления блока 15 считывания контрольного разряда и на вторые входы группы элементов И 14.

Пусть в результате отказа элемен0 та 3 памяти контрольного разряда в

ней всегда хранится логический О. В этом случае режим записи информации не отличается от описанного,При считывании, если элементы 2 памяти 25 информационных разрядов исправны,отказ ячейки памяти контрольного разряда не Приводит к искажению записан- ной информации. Если в результате отказа элемента 3 памяти контрольного 30 разряда в ней всегда хранится логическая 1, то в .режиме записи при промежуточном считывании информации из элементов 2 памяти информационных разрядов с целью обнаружения 25 ощибки записи считьгааемая информация .инвертируется в элементах ИСКЛЮЧАЮ- :ЩЕЕ ИЛИ 16 второй группы, В элементе I10 сравнения вырабатывается сигнал ошибки и записываемая информация ин- 4о вертируется в элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 9 первой группы, а в элемент 3 памяти контрольного разряда записывается сигнал ощибки (логическая 1), При считывании по сигналу разрешения 45 считьгеания информация из элементов 2 памяти информационных разрядов инвертируется второй раз в элементах ИСКЛЮЧАКЯЦЕЕ ИЖ 16 второй группы и

исправленной поступает на информаци- 50 онные выходы 22 устройства. Таким образом, отказ элементов 3 памяти контрольного разряда не приводит к выходу из строя всего ЗУ, Результатом оказывается повышение надежности ЗУ,

Кроме того, в режиме записи появляется возможность индицирования окончания записи ннформахщи в элементы 2 памяти информационных разрядов

55

Н;акопителя , Это достигается благодаря выведению с выхода второго элемента И 19, соединенного с выходом 25 окончания записи устройства, ре- зультата сравнения сигналов, поступающих с выходов второго элемента 1:3 задержки и элемента 10 сравнения HJa соответствующие входы второго элемента И 19. Индицирование оконча- н(ия записи информации позволяет использовать ЗУ для работы в асинхрон- HJOM режиме, что существенно повьшгает cJKOpocTb обработки информации систе- , в состав которой входит предла- Наемое устройство.

8|ормула изобретения

; 1 Оперативное запоминающее уст- Е ойство, содержащее накопитель, ад- pjecHbie шины которого являются адресными входами устройства, блоки запи- С)И информационных и контрольного раз- Р|ядов, выходы которых соединены с со- О|Тветствутощими входами-выходами нако- п итепя, усилители считывания информационных и контрольного разрядов, вхо- дЫ которых соединены с выходами бло- к|ов записи информационных и контроль- Hjoro разрядов соответственно, группу 3цементов И, первые входы которых соединены с выходами соответствующих усилителей считывания информационных разрядов, блок считьгеания контрольного разряда, информационный вход кото- соединен с выходом усилителя считывания контрольного разряда, пер- в группу элементов ИСКШТЧА1()ЩЕЕ ИЛИ, первые входы которых являются инфор- мЦционными входами устройства, а вы- хрды соединены с информационными входами соответствующих блоков записи информационных разрядов, первый элемент ИЛИ, выход которого с оединен с входами разрешения повторной записи бпоков записи информационных и контрольного разрядов, а первый вход является входом разрешения записи устройства, два элемента задержки,вход первого из которых соединен с первым входом первого элемента HJHi, а выход

5 О Q g Q

5

соединен с входом второго элемента задержки, первый элемент И, выход которого соединен с информационным входом блока записи контрольного разряда и с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, элемент сравнения, входы первой группы которого соединены с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, выход элемента сравнения соединен с первым входом первого элемента И, блоки считывания информации, выходы которых являются информационными выходами устройства, вторую группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых соединены с выходом блока считывания контрольного разряда, а выходы соединены с соответствующими входами второй группы элемента сравнения и с информационными входами соответствующих блоков считывания информации, тактовые входы которых объединены и являются входом разрещения считыва-- ния устройства, отличающее- с я тем, что, с целью повышения надежности, устройство содержит второй элемент ИЛИ, первый вход которого соединен с тактовыми входами блоков считывания информации, второй вход - с выходом первого элемента , задержки, а выход - с тактовым вхо-. дом блока считывания контрольного разряда и с вторыми входами элементов И группы, выходы которых соединены с вторыми входами соответствующих элементов ИСКЛЮЧАЩЕЕ ИЛИ второй группы, выход второго элемента задержки соединен с вторым входом первого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ,

| IEEE | |||

| Journal of Solid State Circuits, 1979, 5, p | |||

| АППАРАТ ДЛЯ РАЗРЕЗАНИЯ ПЕРЕДВИГАЮЩЕЙСЯ НА ПОДВИЖНОМ СТОЛЕ ТОРФЯНОЙ ПОЛОСЫ ПРИ ПОМОЩИ НОЖЕЙ, УКРЕПЛЕННЫХ НА ПОВЕРХНОСТИ БАРАБАНА | 1922 |

|

SU602A1 |

| Полупроводниковое оперативное запоминающее устройство | 1985 |

|

SU1295446A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-09-23—Публикация

1987-01-06—Подача