Изобретение относится к вычислительной технике, в частности к микропроцессорам с микропрограммным управлением,

Целью изобретения является повьше- ние быстродействия устройства.

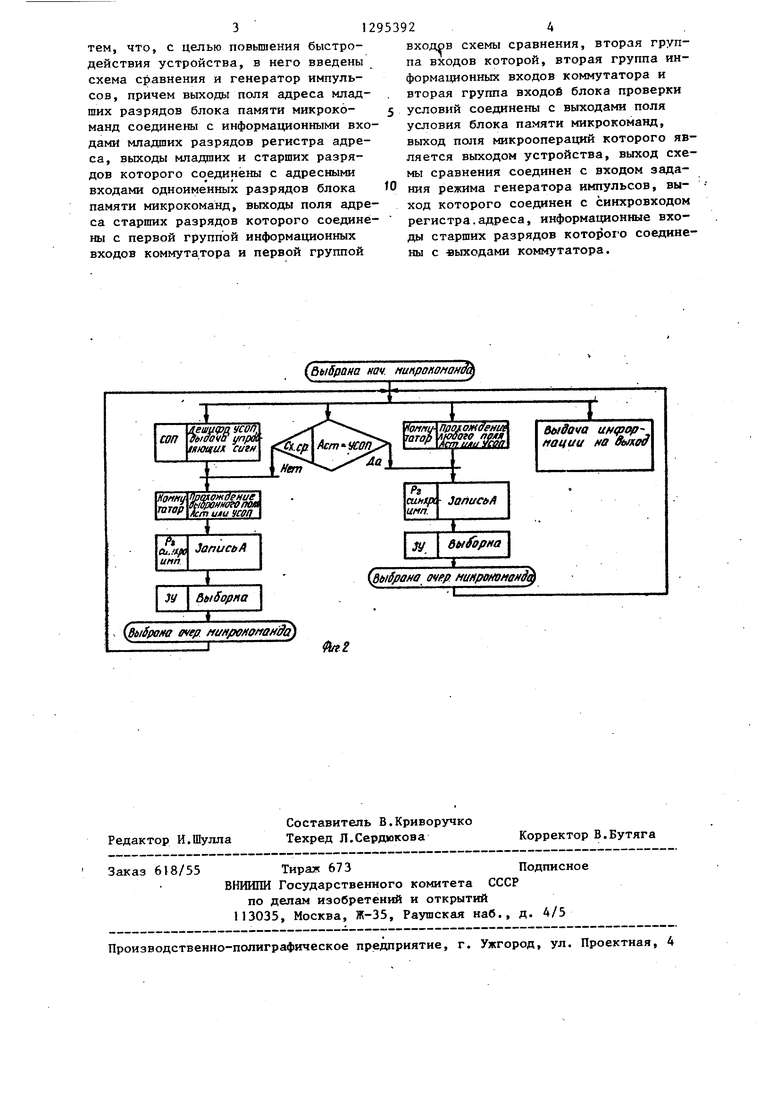

На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - алгоритм функционирования устройства.

Устройство (фиг,1) содержит регистры 1 адреса, блок 2 памяти микрокоманд, коммутатор 3, блок 4 проверки условий, схему 5 сравнения, генератор 6. В блок 4 проверки условий входит дешифратор 7, блок 8 элементов И, элемент ИЛИ 9 и инвертор 10.

Устройство работает следующим образом.

При условных переходах в поле УСОП кодируется условие, по состоя- J5 нию которого происходит переход. В поля А и заносится один из возможных адресов перехода, который выбирается так, чтобы код А,. не был равен коду УСОП. С момента появления

В исходном состоянии регистр 1 ад- 20 микрокоманды код УСОП начинает дешифреса обнулен - по нулевому адресу из блока 2 памяти микрокоманд выбирается начальная микрокоманда программ. С момента ее выборки начинаются три процесса: прохождение информации через коммутатор 3 с одной из групп его входов, дешифрация кода управления в блоке 4 проверки условий и сравнение на равенство кодов соответственно поля старшей части адреса А .. и поля логического условия (УСОП)

татор 3. Блок 4 выдает на выходы состояние, зависшцее от состояния рассматриваемого условия. В результате через коммутатор 3 пропускается код либо с первого, либо с второго плеча

в схеме 5 сравнения. Далее в зависимости от результата сравнения в схеме 5 алгоритм реализуется по одной из двутс веток в зависимости от вида- 35 и в регистр I записывается либо код условного или безусловного - перехо- -сг А,, либо код УСОП, А„д. Таким да к следующей микрокоманде,образом, в зависимости от состояния

Рассмотрим случай безусловного пе- условия при условном переходе форми- рехода.руется один из двух возможных кодов

Адрес следующей микрокоманды запи- адреса следующей микрокоманды. В сывается в поле младшей части адреса

длительность указанного такта входят задержки в блоке 4, коммутаторе 3, регистре 1, блоке 2 памяти, т.е. он равен такту известного устройства (и условного, и безусловного).Ад и в поле А . Кроме того, поле УСОП кодируется одинаково с полем А , что возможно, так как при безусловных переходах поле УСОП свободно от своих прямых обязанностей. В результате схема 5 выдает сигнал логической 1, идентифицирующий равенство А(, УСОП, т.е. безусловный переход. По этому сигналу генератор 6 без задержек вырабатывает импульс на регистр I адреса, в котором фиксируется следующий адрес микрокоманды. Благодаря равенству А УСОП безразлично, какое из плеч коммутатора 3 открыто, т.е. состояние бЯока 4 здесь значения не имеет и задержка на прохождение сигнала через блок 4

в длительность такта с бeчycлoвшJlм переходом не входит. Кроме того, обеспечивается параллельное прохождение сигнала через коммутатор 3 со срабатыванием 5 и генератора 6: в длительность указанного такта входит либо задержка в коммутаторе 3, либо задержка в схеме 5 и генераторе 6 (наибольшая из них). Распараллеливание этих процедур также увеличивает быстродействие при безусловных переходах.

При условных переходах в поле УСОП кодируется условие, по состоя- 5 нию которого происходит переход. В поля А и заносится один из возможных адресов перехода, который выбирается так, чтобы код А,. не был равен коду УСОП. С момента появления

ст логироваться дешифратором блока 4. Параллельно схема 5 анализирует коды А. и УСОП и вырабатывает сигнал ческого.0 (Ар, УСОП, условный переход). По этому сигналу генератор 6 с задержкой формирует синхроимпульсы. Задержка определяется прохождением сигнала через элементы И 8, элемент ИЛИ 9, инвертор 10 и коммутатор 3. Блок 4 выдает на выходы состояние, зависшцее от состояния рассматриваемого условия. В результате через коммутатор 3 пропускается код либо с первого, либо с второго плеча

и в регистр I записывается либо код -сг А,, либо код УСОП, А„д. Таким образом, в зависимости от состояния

адреса следующей микрокоманды. В

длительность указанного такта входят задержки в блоке 4, коммутаторе 3, регистре 1, блоке 2 памяти, т.е. он равен такту известного устройства (и условного, и безусловного).Формула изобретения

Микро/грограммное устройство управ- ления, содержащее блок памяти микрокоманд, регистр адреса, коммутатор, блок проверки условий, первая группа входов которого является входами логических условий устройства, первый 55 и второй выходы блока проверки условий соединены соответственно с первым и вторым управляющими входами коммутатора, отличающееся

тем, что, с целью повышения быстродействия устройства, в него введены схема сравнения и генератор импульсов, причем выходы поля адреса младших разрядов блока памяти микрокоманд соединены с информационными входами младших разрядов регистра адреса, выходы младших и старших разрядов которого со единёны с адресными входами одноименных разрядов блока памяти микрокоманд, выходы поля адреса старших разрядов которого соединены с первой группой информационных входов коммутатора и первой группой

Редактор И.Шулла

Составитель В.Криворучко Техред Л.Сердюкова

Заказ 618/55 Тиран 673Подписное

ВНИИПИ Государствениого комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

входов схемы сравнения, вторая группа входов которой, вторая группа информационных входов коммутатора и вторая группа входов блока проверки условий соединены с выходами поля условия блока памяти микрокоманд, выход поля микроопераций которого является выходом устройства, выход схемы сравнения соединен с входом задания режима генератора импульсов, выход которого соединен с синхровходом регистра.адреса, информационные входы старших разрядов которого соединены с выходами коммутатора.

Корректор В.Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1310815A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Устройство микропрограммного управления | 1987 |

|

SU1524049A1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2020559C1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310817A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Устройство микропрограммного управления | 1984 |

|

SU1226453A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1233155A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1629910A1 |

Изобретение относится к вычислительной технике и может использоваться в микропроцессорных системах с микропрограммным управлением. Цель изобретения - увеличение быстродействия устройства. Устройство содержит регистр 1 адреса, блок 2 памяти микрокоманд, коммутатор 3, блок 4 проверки условий, схему 5 сравнения, генератор 6. Цель достигается за счет того, что при безусловных переходах поле кода логического условия микрокоманд кодируется одинаково с полем старшей части адреса. В этом случае схема 5 сравнения вырабатывает сигнал, по которому генератор 6 формирует синхроиь-тульсы с укороченным периодом следования. 2 ил. ё

| Майоров С.А., Новиков Г.И | |||

| Принципы организации цифровых машин | |||

| - Л.: Машиностроение, 1974, с | |||

| Прибор для записи звуковых волн | 1920 |

|

SU219A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Майоров С.А., Новиков Г.И | |||

| Структура электронных вычислительных машин | |||

| - Л.: Машиностроение, 1979, с, , рис | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Прин | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1987-03-07—Публикация

1985-07-05—Подача