ел ю

4;

О 4

;о

Изобретение относится к автоматике и вычислительной технике и может быть использоваио в контроллерах периферийных устройств и в управляющих автоматах.

Цель изобретения - повышение быстродействия устройства путем уменьшения задержки выдачи выходных сиг- калов при операциях условного перехода.

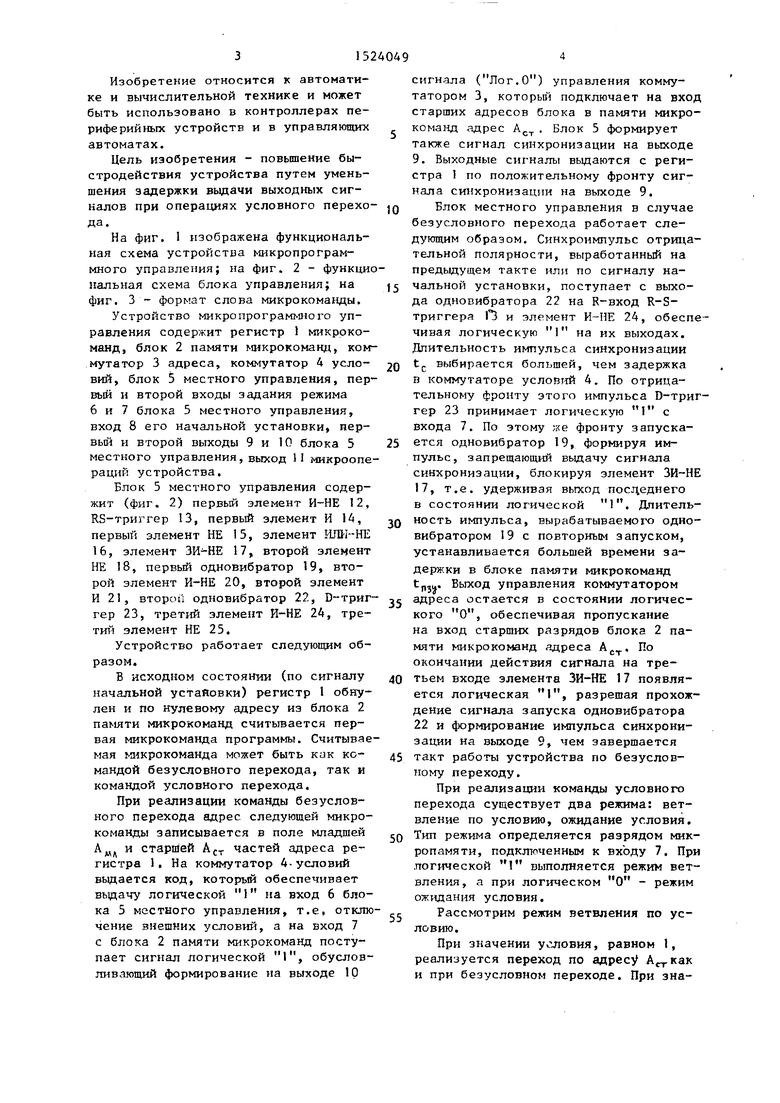

На фиг. 1 изображена функциональная схема устройства микропрограммного управления; на фиг. 2 - функцинальная схема блока управления; на фиг. 3 - формат слова микрокоманды. Устройство микропрограммного управления содержит регистр 1 микрокоманд, блок 2 памяти микрокоманд, коммутатор 3 адреса, коммутатор 4 условий, блок 5 местного управления, первый и второй входы задания режима 6 и 7 блока 5 местного управления, вход 8 его начальной установки, первый и второй выходы 9 и 10 блока 5 местного управления, выход 11 микроопераций устройства.

Блок 5 местного управления содержит (фиг. 2) первый элемент И-НЕ 12, RS-триггер 13, первый элемент И 1А, первый элемент НЕ 15, элемент ИЛК-НЕ 16, элемент ЗИ-НЕ 17, второй элемент НЕ 18, первый одновибратор 19, второй элемент И-НЕ 20, второй элемент И 21, второй одновибратор 22, D-триг гер 23, третий элемент И-НЕ 24, третий элемент НЕ 25.

Устройство работает следующим образом,

В исходном состоянии (по сигналу начальной устайовки) регистр 1 обнулен и по нулевому адресу из блока 2 памяти микрокоманд считьшается первая микрокоманда программы. Считываемая микрокоманда может быть как командой безусловного перехода, так и командой условного перехода.

При реализации команды безусловного перехода адрес следующей микрокоманды записывается в поле младшей А, и старшей частей адреса регистра 1. На коммутатор 4-условий выдается код, который обеспечивает выдачу логической 1 на вход 6 блока 5 местного управления, т.е, отключение внешних условий, а на вход 7 с блока 2 памяти микрокоманд поступает сигнал логической I, обусловливающий формирование на выходе IQ

сигнала (Лог.О) управления коммутатором 3, которьп подключает на вход старших адресов блока в памяти микро- команд адрес А. Блок 3 формирует также сигнал синхронизации на выходе 9. Выходные сигналы выдаются с регистра I по положительному фронту сигнала синхронизации на выходе 9.

Блок местного управления в случае безусловного перехода работает следующим образом. Синхроимпульс отрицательной полярности, выработанный на предыдущем такте или по сигналу начальной установки, поступает с выхода одновибратора 22 на R-вход R-S- триггера 1 Э и элемент И-НЕ 24, обеспечивая логическую 1 на их выходах. Длительность импульса синхронизации

tj. выбирается большей, чем задержка в коммутаторе ycлoв iй 4. По отрицательному фронту этого импульса D-триг- гер 23 принимает логическую 1 с входа 7, По этому же фронту запускается одновибратор 19, формируя импульс, запрещающий выдачу сигнала синхронизации, блокируя элемент ЗИ-НЕ 17, т.е. удерживая выход посдеднего в состоянии логической 1. Дпительность импульса, вырабатываемого одно- вибратором 19 с повторным запуском, устанавливается большей времени задержки в блоке памяти микрокоманд tpju. Выход управления коммутатором

адреса остается в состоянии логического О, обеспечивая пропускание на вход старших разрядов блока 2 памяти микрокоманд адреса А. По окончании действия сигнала на третьем входе элемента ЗИ-НЕ 17 появляется логическая I, разрешая прохождение сигнала запуска одновибратора 22 и формирование импульса синхронизации на выходе 9, чем завершается

такт работы устройства по безусловному переходу.

При реализации команды условного перехода существует два режима: ветвление по условию, ожидание условия.

Тип режима определяется разрядом микропамяти, подключенным к входу 7. При .тгагической вьшолняется режим ветвления, а при логическом О - режим ожидания условия.

Рассмотрим режим ветвления по условию.

При значении условия, равном I, реализуется переход по адресу и при безусловном переходе. При значении условия, равном О, реализуется

переход по адресу А

пер

Блок 5 местного управления в этом случае работает следующим образом. После снятия блокировки с RS-триггера 13 и элемента И-НЕ 24 на инверсном выходе R-S-триггера 13 остается логическая I, а на выходе элемента И-НЕ 24 устанавливается логичесК1{й О, что приводит к появлению логической 1 на выходе 10. Передний фронт этого сигнала повторно запускает одновибра- тор 19, а коммутатор 3 переключается на пропускание адреса Apg.. Появление логической 1 на выходе одновибрато- ра 19 по истечении времени tpji. (логическая 1 на втором входе элемента И-НЕ 20) приводит к запуску одновибра тора 22, чем завершается цикл работы по нулевому значению условия в режиме ветвления.

Рассмотрим режим ожидания условия.

При отсутствии условия устройство

ческих условий регистра микрокоманд, выход кода логических условий которого соединен с первым информационным входом коммутатора адреса, второй информационный вход которого соединен с выходом поля старших разрядов адреса регистра микрокоманд, информационный вход которого соединен с выходом

полей адреса и микроопераций блока памяти микрокоманд, отличающееся тем, что, с целью повышения быстродействия путем уменьшения задержки выдачи выходных сигналов при

операциях условного перехода, выход коммутатора условий соединен с первым входом задания режима блока управления, первьй выход которого соединен с синхровходом регистра микрокоманд, выход поля MiKpoonepaiyiA которого является выходом микроопераций устройства, выход поля младших разрядов адреса регистра микрокоманд соединен с входом младших разрядов

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1262516A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1633402A1 |

| Процессор | 1976 |

|

SU670935A1 |

| Асинхронное устройство для программного управления | 1987 |

|

SU1481712A1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1629910A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при создании микропрограммных автоматов управления устройствами автоматики, в частности в контроллерах внешних устройств ЭВМ и интерфейсных узлах. Цель изобретения - повышение быстродействия устройства путем уменьшения задержки выдачи выходных сигналов при операциях условных переходов. Устройство содержит регистр микрокоманд 1, блок 2 памяти микрокоманд, коммутатор 3 адреса, коммутатор 4 условий, блок 5 местного управления. Цель достигается за счет того, что адрес перехода по наличию условия подготавливается заранее, а в момент смены условия формируется сигнал приема в регистр микрокоманд выходных сигналов с минимально возможной задержкой. 1 з.п. ф-лы, 3 ил.

микропрограммного управления по окон- 25 адреса блока памяти микрокоманд, вычании импульса с одновибратора 19 переходит в статическое состояние анализа условия и ожидает появление его единичного значения. Реализация перехода в этом режиме зависит от момен- ЗО ляющим входом кoм ryтaтopa адреса.

врета времени появления условия и сводится к двум вариантам: условие появляется раньше чем заканчивается сигнал tp, вьщаваемый с одновибратора 19. Сигнал синхронизации на выходе 9 формируется после окончания времени t условие появляется по истечении мени tnju.

При этом режиме на вход блока 2 памяти микрокоманд пропускается адрес к моменту прихода условия информация уже подготовлена на входе регистра 1 и выходных сигналов. Поэтому время реакции предлагаемого устройства на условие всегда одно и то же и исключает время считывания с блока микрокоманд.

Формула изобретения

35

40

45

50

55

рыход которого соединен с входом старших разрядов адреса блока памяти микрокоманд, вход начальной установки устройства соединен с одноимеины- № входами блока управления и регистра микрокоманд.

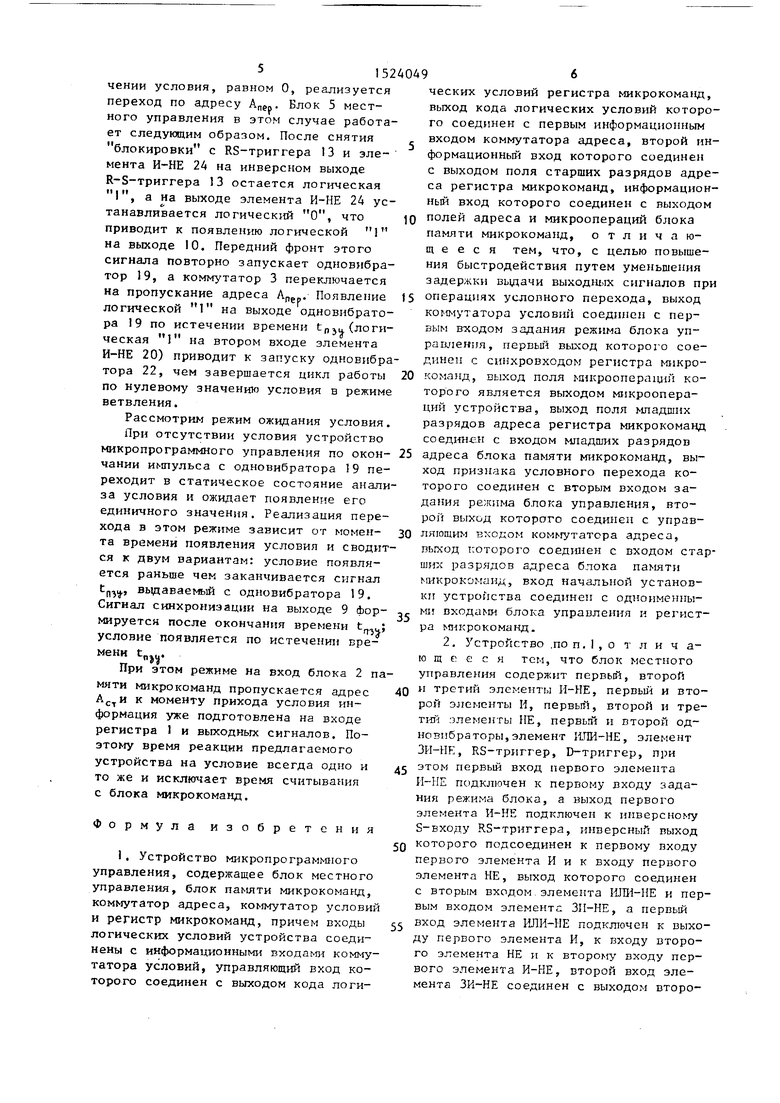

Старшие разряды

Сгларшие paspfldbi affpEca. перевода

(код продер емого {/сло8ия)

Фиг.

тх

Sum, определяющий дариант услоУноео перехода Поле Sbixod/fb/x сималоб

Младшие разряды адреса.

| Майоров С.А., Новиков Г.И | |||

| Структура ЭВМ | |||

| - Л.: Машиностроение, 1979, с | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1295392A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-23—Публикация

1987-10-09—Подача