1

15

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297055A1 |

| Устройство для контроля сдвигателя | 1989 |

|

SU1672456A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1580368A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Устройство для формирования сигналов четности | 1988 |

|

SU1571591A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1325481A1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

Изобретение относится к вычислительной технике и может быть использовано при организации контроля сдвигателей. Цель изобретения - расширение области применения устройства. Устройство содержит блок 1 сдвига контрольных разрядов, блок 2 побитных сдвигов, узел 3 свертки по модулю два, коммутатор 4, группу 5 сумматоров по модулю два. Введение в устройство коммутатора 4 и группы 5 сумматоров по модулю два, позволяющих в совокупности организовать побитный сдвиг, обеспечивает контроль логических и циклических кодов как вправо, так и влево для любой конструкции сдвигателей в блоке 2 побитных сдвигов и блоке 1 сдвига контрольных разрядов, 3 ил.

00

-

о

фиг.1

т

12

Изобретение относится к вычислительной технике и может быть использовано при организации контроля сдвигателей двоичных кодов.

Цель изобретения - расширение об- ласти применения устройства.

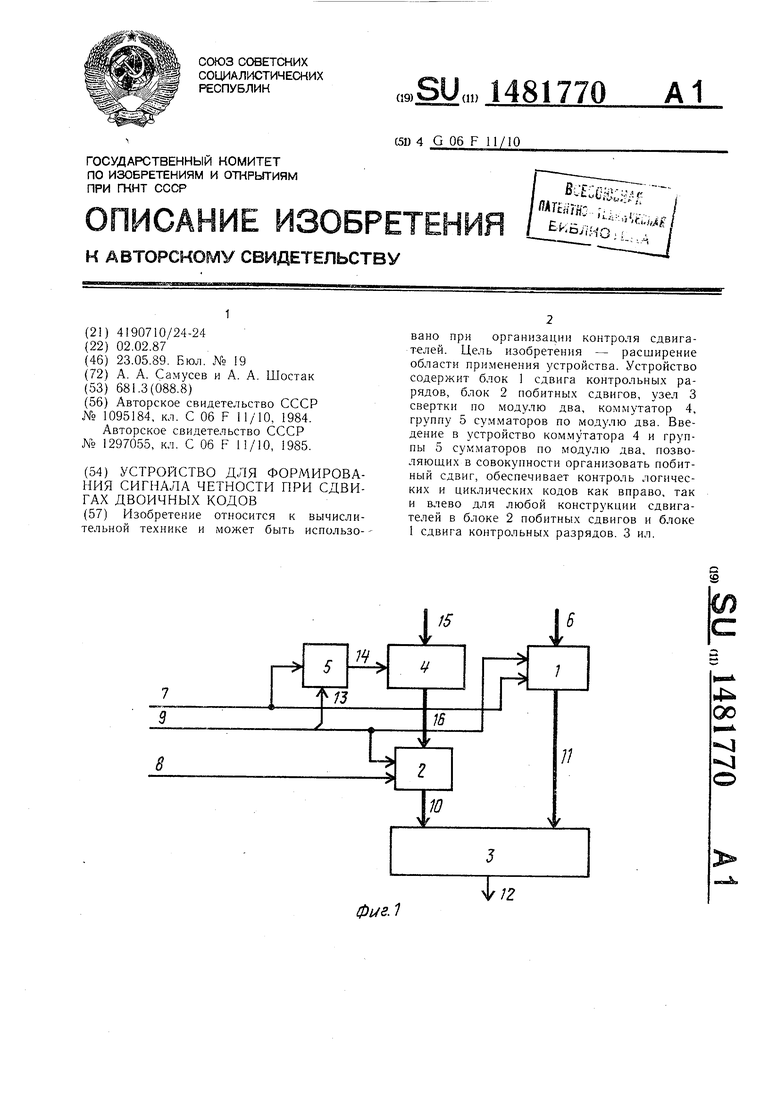

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема блока побитных сдвигов; на фиг. 3 - функциональная схема кодо- преобразователя блока побитных сдвигов.

Устройство для формирования сигнала четности при сдвигах двоичных кодов содержит блок 1 сдвига контрольных разрядов, блок 2 побитных сдвигов, узел 3 свертки по модулю два, коммутатор 4, группу 5 сумматоров по модулю два, вход 6 контрольных разрядов устройства, входы 7 и 8 задания величины побайтных и побитных сдвигов соответственно, вход 9 задания типа сдвига устройства, группу 10 выходов блока 2 побитных сдвигов, выход 11 блока сдвига контрольных разрядов, выход 12 устройства, разряд 13 признака направления сдвига входа 9 задания типа сдвига устройства, группу 14 управляющих входов коммутатора 4, группу 15 информационных входов устройства, выход 16 коммутатора 4.

Блок 2 побитных сдвигов содержит кодопреобразователь 17, сдвигатель 18, дешифратор 19 нулевой комбинации, группу 20 элементов И, разряды 21 и 22 призна- ков циклического сдвига и направления сдвига входа 9 задания типа сдвига устройства, выход 23 кодопреобразователя 17, выход 24 дешифратора 19 нулевой комбинации, выходы 25 и 26 младшего и старшего разрядов сдвигателя 18, выход 27 пер- вого элемента И группы 20, группу 28 выходов сдвигателя 18 без младшего и старшего разрядов, выход 29 второго элемента И группы 20.

Кодопреобразователь 17 содержит группу 30 элементов И, элементы И 31-33, группу 34 сумматоров по модулю два.

Блок 1 сдвига контрольных разрядов сдвигает логически или циклически контрольные разряды соответствующих групп из К разрядов (байтов) сдвигаемого дво- ичного кода. Он может быть построен на БИС-сдвигателе типа К 1800 ВР8.

В блоке 2 побитных сдвигов сдвигатель также может быть выполнен на БИС- сдвигателе типа К 1800 ВР8, где обеспечиваются логические сдвиги вправо и влево на величину разрядов, определяемую кодопреобразователем 17. Эта величина представляет собой дополнительный код числа, установленного на входе 8 задания величины побитных сдвигов устройства.

При нулевых сдвигах на входе 8 уст- ройства устанавливается нулевой код, и на выходе дешифратора 19 нулевой комбинации формируется нулевой сигнал.

При циклических сдвигах в сдвигателе 18 блока 2 побитных сдвигов осуществляются логические сдвиги вправо или влево на (К-1) разрядов.

Каждый t-й разряд информационного входа сдвигателя 18 подключен к (К- - 1-1)-му разряду выхода 16 коммутатора 4 (CteUK-1).

Коммутатор 4 представляет собой -Ц

JV

входовой мультиплексор (N - разрядность сдвигаемого кода). Каждый вход содержит К разрядов.

Устройство работает следующим образом.

В исходном состоянии на группу 15 информационных входов устройства подается

сдвигаемый Л -разрядный код. На

Я

-разрядах входа 6 контрольных разрядов устройства устанавливаются контрольные разряды байтов сдвигаемого кода.

На входах 7 и 8 задания величины побайтных и побитных сдвигов устройства устанавливаются коды, определяющие, на сколько целых байтов осуществляется сдвиг числа коммутатором 4 и на сколько битов сдвигается выбранный байт.

На входе 9 задания типа сдвига устанавливается код, определяющий вид (логический или циклический) и направление сдвига.

Предусмотрены следующие типы сдвига: ЛЛ - логический сдвиг влево, ЛП - логический сдвиг вправо, ЦЛ - циклический сдвиг влево, ЦП - цилиндрический сдвиг вправо. Для задания ЛЛ, ЛП, ЦЛ, ЦП на входе 9 задания типа сдвига устройства в разрядах 21, 22 (13) устанавливаются соответственно коды 10, 11, 00, 01. На выходе 12 устройства формируется предсказанный сигнал четности

В качестве примера рассматривается сдвиг кода 1101100010111110 при и . На входе 6 контрольных разрядов устройства устанавливается код 1111. Для осуществления сдвига на 10 разрядов на входы 7 и 8 задания величины побайтных и побитных сдвигов устройства необходимо подать одинаковый код 10.

При логическом сдвиге влево сдвинутый код будет равен 1111100000000000, сигнал четности которого равен «1.

На входе 9 устройства при этом устанавливается код ЛЛ-10. На группу управляющих входов коммутатора 4 передается код 10, под действием которого на -выходе 16 коммутатора 4 появляется код 1011, который поступает на информационный вход сдвигателя 18 в виде кода 1101. На выходе 11 блока 1 сдвига контрольных разрядов формируется код 1100 На выходе 23 кодопреобразователя 17 формируется дополнительный код от кода 10, который также

равен 10. В результате в сдвигателе 18 осуществляется логический сдвиг влево на два разряда кода 1101 и на группе 10 выходов блока 2 сдвига формируется сдвинутый код, равный 0100. Таким образом, на входах узла 3 свертки по модулю два оказываются коды 0100 и 1100, а на выходе 12 устройства - единичный сигнал.

Аналогичным образом осуществляется в устройстве формирование предсказанного сигнала четности при логических сдвигах вправо с установкой на входе 9 устройства кода ЛП-11. При этом на группу управляющих входов коммутатора 4 поступает код 01 - проинвертированный код с входа

7устройства. В результате на выходе 16 коммутатора 4 появляется код 1000, поступающий на информационный вход сдвигате- ля 18 в виде кода 0001. Далее устройство работает так же, как и пря сдвиге влево, с тем отличием, что в блоке 1 сдвига контрольных разрядов и сдвигателе 18 осуществляется логический сдвиг вправо.

При установке на входе 8 устройства нулевого кода на выходе 24 дешифратора 19 нулевой комбинации формируется логический ноль, а на выходе 23 кодопреобразователя 17 - код 11. На разрядах группы 28 сдвкгателя 18 формируется нулевой код, а на выходах 27, 28 элементов И группы 30 формируется логический ноль.

8итоге сигнал на выходе 12 устройства определяется кодом на выходе блока 1 сдвига контрольных разрядов.

Аналогично при циклических сдвигах на входе 9 устройства устанавливается код ЦЛ или ЦП, при которых на входе 9 устройства в разряде 21 признака циклического сдвига содежится нулевой сигнал. На выходе 23 кодопреобразователя 17 формируется код 11, а на выходах группы 10 блока 2 сдвига - нулевой код. В блоке 1 сдвига осуществляются циклические сдвиги. Сигнал на выходе 12 устройства определяется кодом на выходе блока 1 сдвига.

0

5

0

5

0

5

0

Таким образом, в устройстве обеспечивается формирование сигнала четности при сдвигах двоичных кодов на сдвигателях любой структуры (конструкции).

Формула изобретения

Устройство для формирования сигнала четности при сдвигах двоичных кодов, содержащее блок сдвига контрольных разрядов, блок побитных сдвигов, узел свертки по модулю два, причем группа выходов блока побитных сдвигов соединена с соответствующими входами узла свертки по модулю два, выход которого является выходом устройства, вход задания величины сдвига и вход задания типа сдвига блока сдвига контрольных разрядов являются соответственно входом задания величины побайтных сдвигов и входом задания типа сдвигов устройства, вход задания величины сдвига блока побитных сдвигов является входом задания величины побитных сдвигов устройства, вход задания типа сдвига блока побитных сдвигов подключен к входу задания типа сдвига устройства, информационный вход блока сдвига контрольных разрядов является входом контрольных разрядов устройства, отличающееся тем, что, с целью расширения области применения устройства, в него введены коммутатор и группа сумматоров по модулю два, причем первые входы сумматоров по модулю два группы подключены к соответствующим разрядам входа задания величины побайтных сдвигов устройства, выходы сумматоров по модулю два группы соединены с группой управляющих входов коммутатора, выход которого соединен с информационным входом блока побитных сдвигов, вторые входы сумматоров по модулю два группы объединены и подключены к разряду признака направления сдвига входа задания типа сдвига устройства, выход блока сдвига контрольных разрядов соединен с входом узла свертки по модулю два, группа информационных входов коммутатора является группой информационных входов устройства.

фие.2

Ю

| Устройство для сдвига информации с контролем | 1983 |

|

SU1095184A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297055A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1987-02-02—Подача